TK80/BSの

シンセシステムを復活/拡張したい〜

その19

FPGA,SP−808EX

AKAIハードディスクレコーダ

2018年

2018年

2月24日

FPGA開発用に中古ノートPCを新調しました。レノボのT420Sです。Win7の64ビット、メモリが少なくて4Gです。後で増設します。とりあえず、最新版のVivadoをインストールして持ってきました。

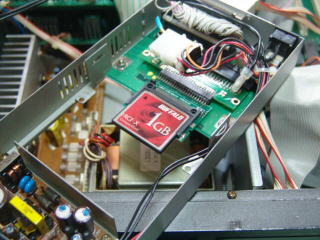

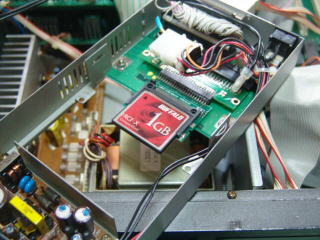

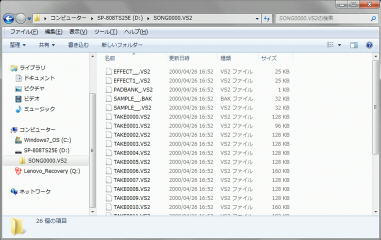

ぜんぜん使っていないSP−808をアパートから持ってきました。ZIPディスクはCFカードに交換されています。内部はEX仕様でデジタル入出力オプションボード付きです。

CFカードの代わりにSDカードを入れてみましたが、認識しませんでした。残念。CFカードは普通?の1倍で良いようです。

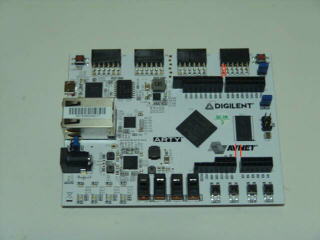

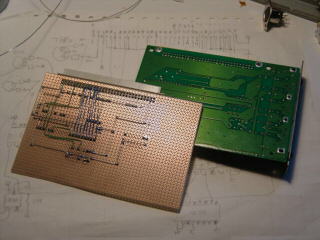

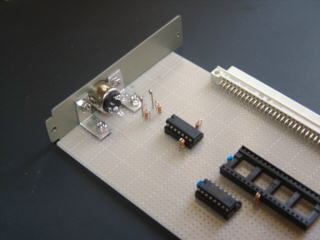

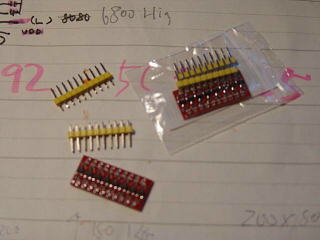

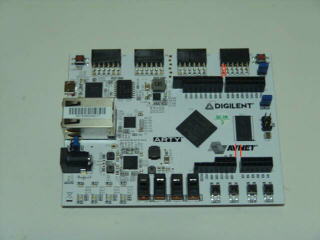

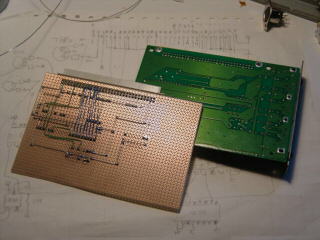

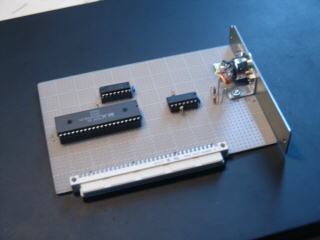

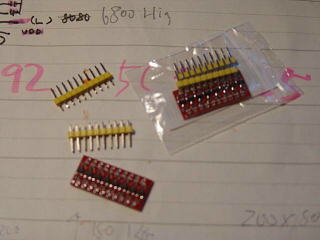

秋月の通販で購入したArtix−35Tとユニバーサル基板、接続ピンヘッダです。

FPGAプログラミング大全をアパートに忘れてきたので、WEBを見ながら、とりあえずLチカ(笑)。

ヤフオクでノート用メモリを購入。8Gバイトです。

SK−88(SC−88Pro)のリズム音をSP−808でサンプリングしました。

2月25日

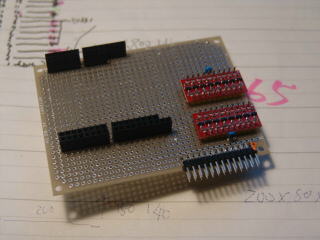

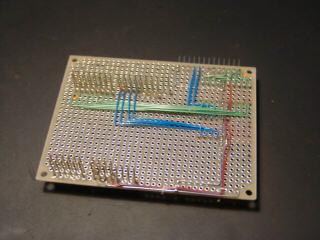

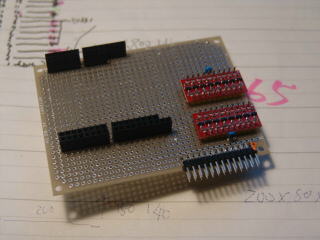

FPGAボードの上に載せるユニバーサル基板を作製します。アルドウィーノ互換のピンなので、上側のコネクタの間隔はハーブピッチになっています。ピンを曲げる必要があります。

DR8用の外付けCFですが、266倍が刺さっています。SP−808に使っている普通の1倍?の1Gを接続したところ、転送速度が間に合わないというエラーが出て使えませんでした。ある程度早いものを使う必要があるようです。

MSP430のUSB−MIDI変換を修正して9ch目をそのままUART−MIDIに出力するようにしました。SP−808に内蔵されている仮想アナログシンセ用です。1〜8chがDCO・アナログシンセ、9chと10chがSP−808の仮想アナログシンセとサンプリングリズムです。

3月3日

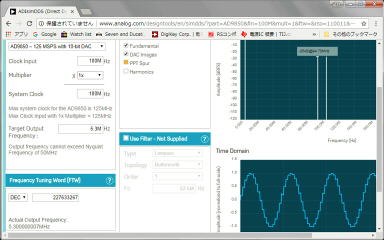

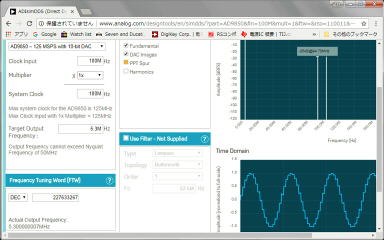

アナログデバイセズのWEBページでDDSのシミュレーションができます。選んだデバイスはAD9850です。100MHzから5.3MHzを生成しています。出力フィルタ無しです。

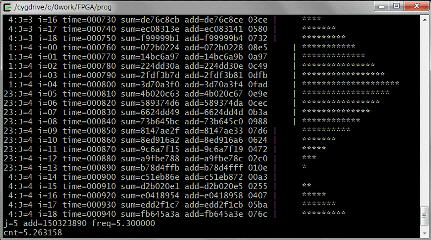

Cで同じように計算してみます。テーブルはあらかじめ用意しないで都度、三角波を計算します。三角波の中央値でコンパレートすると5.3Mhzは5.263158Mzになりました。

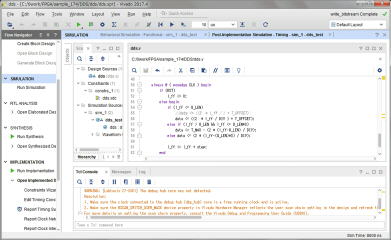

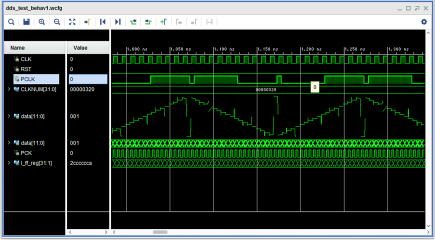

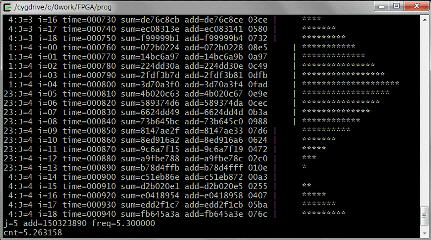

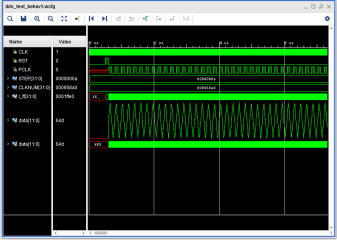

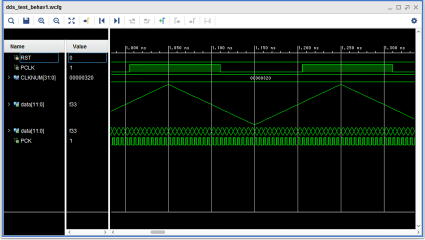

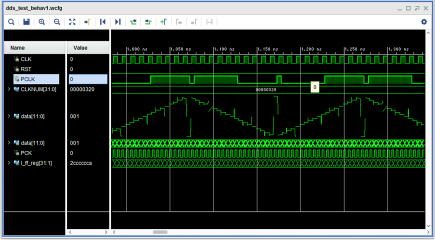

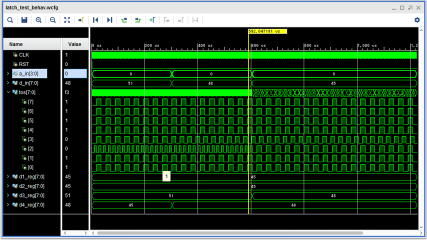

CをVerilogに変換してVivadoでシミュレーションしてみました。

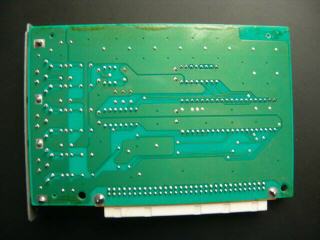

友人SからDR8のMIDIインターフェースを借りました。部品は汎用品で、そのまま作れそうです(笑)。

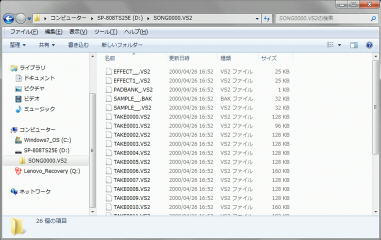

SP−808のCFカードですが、ノートPCに接続したところ、普通のFAT16でした。カードリーダでバックアップできるので良かったです。外付けZIPドライブを買おうかと思ったのですが必要ないです。

会社の廃品置き場にあったアルドウィーノのMEGA(ADK)とUNOです。Lチカを動かすと、双方とも動作良好でした。UNOはCF/RTCボート付き。

FPGAのユニバーサル基板のピンヘッダのハーブピッチの部分です。普通のユニバーサルの場合にはハーブピッチ分だけピンを曲げないと入らないです。MEGAとUNOで間違えて拡張基板が刺さらないようにコネクタがズレているようです。

ボルカビーツもサンプリングします。SK−88と比べてみました。SK−88はステレオでなかなか良いです。mp3はこれです。リズムとベース部(仮想アナログシンセ)がSP−808で、それ以外は旧DCO・シンセです。

3月4日

MIDIインターフェースをDR8に入れてみました。メニューにMTCマスターの設定項目が追加されます。

ネットの通販で購入したワイヤラックです。訳あり品で送料無料で2980円でした。中身は無印中国製です。早速、DR4/8の載っている台をワイヤラックの前側ポールが入るように切り取ります。

仮組み完了、機材は置いただけで配線は次回に持ち越しです。

3月10日

今週末にアパートから移動したMM−200(ラインミキサ)とA−880(MIDIパッチ)です。設置しただけで配線できてません。

先週の続きです。DR8内のMIDIインタフェースとSP−808の同期テストを行います。DR8をMTCマスターにしてSP−808をスレーブに設定します。MTCで正常に同期しました。

次にPCとDR8を接続します。DR8はマスタのみなので、PC側をスレーブにします。残念ながらDOMINOはMTC/MIDIクロックのスレーブにならないため、もう一つのフリーのシーケンサの世界樹を使います。MTCでは上手く同期できないようなので、MIDIクロックでテストすると同期できました。DR8側をソングモードにしてオフセットを上手く調整すれば曲の頭も合って同期できました。

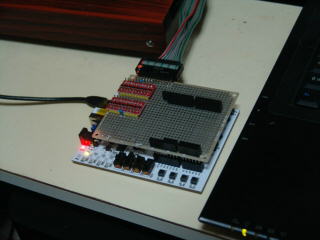

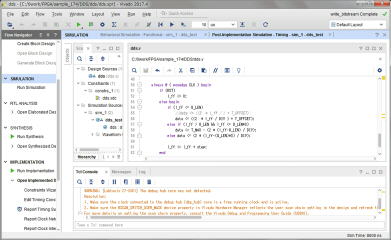

FPGAのDDSの続きです。先週は合成しただけでシミュレーションしましたが、今回は実際にボードに論理を書き込んでみます。

100MHzから5.3MHzを出力してみます。周波数カウンタで測定します。5.3MHzです。

今度は5.32MHzです。こちらもほぼ、5.32Mhzです。Cで計算したよりも細かく出力できるようです。

3月11日

実際に欲しいのはもっと周波数が高くて20〜30MHzくらなので、元クロックをMMCM(PLL)で2倍にした200MHzから作ってみました。合成後のシミュレーションでは問題ないですが、インプリ後では上手くいきません。上下で折り返すところでアドレスの加算が間違っているようです。

SP−808と6chミキサを載せるワイヤラックをホームセンタで購入してきました。丁度、安売り中で、1980円でした。後ろに見えている小型オシロが載っているラックと同じ物です。

3月17日

今週末の機材移動はVP−9000(サンプラ)とS−760(サンプラ)、もう一台のA−880(MIDIパッチ)です。VP−9000のCD−ROMとS−760のHDDも運びました。配線は全然できてません。

友人Sから借りたDR4のMIDIインタフェースです。シールに隠れていた型番はH8/330でした。DR8とは異なり、CPUを使っています。ワンタイム版です。PLCCのアダプタを作って、プログラムを読み出せれば作れるかも知れません(笑)。早速、動作確認しました。

世界樹をスレーブにしてMIDIクロックで同期できました。

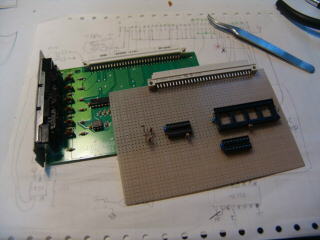

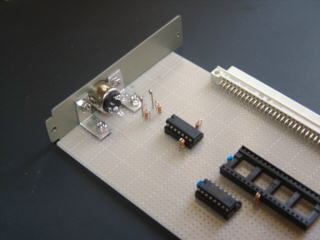

マルツの通販で購入した74LS05、74HC390、DIN5ピンのMIDIコネクタとユニバーサル基板です。

こちらはモノタロウで購入の64ピンの2列DINコネクタです。

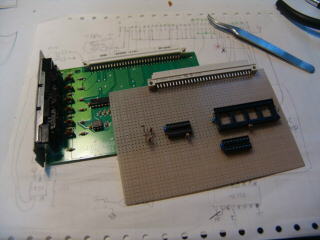

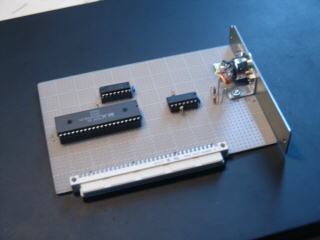

DR8のMIDIインタフェースを作製します。ユニバーサル基板のサイズを合わせて、DINコネクタを仮止めします。

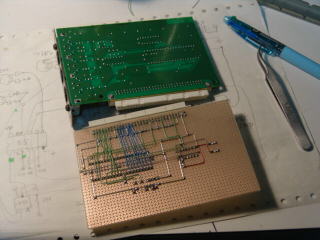

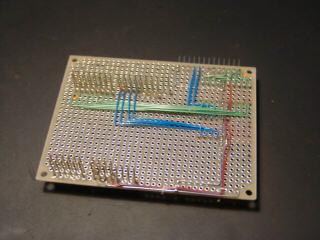

本物をお手本に配線して行きます。MIDI出力のみで入力とスルーは実装しません。

ほぼ、完成しました。

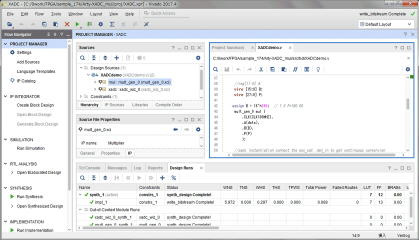

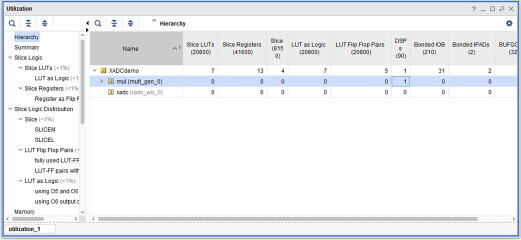

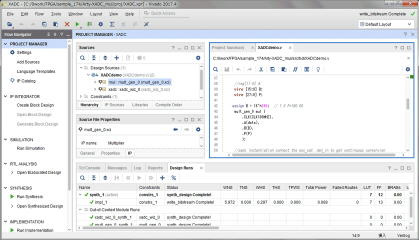

FPGAの続きです。DCOの9ビット/DDS化?に向けて色々と実験しています。DigilentのサイトにあるXADC(ADコンバータ)のサンプルコードに固定小数点の乗算器を追加してます。IPカタログから乗算器を追加して、変換されたADCの値を1.5倍にしてみます。固定小数点の乗算は位取りを考慮すれば整数の乗算と同じです。

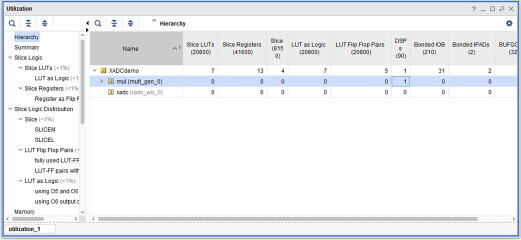

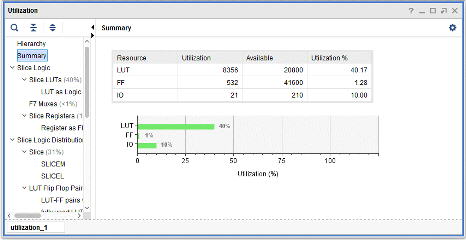

乗算器はDSPを使うように指定します。リソースで確認するとDSPが使われているとが確認できました。

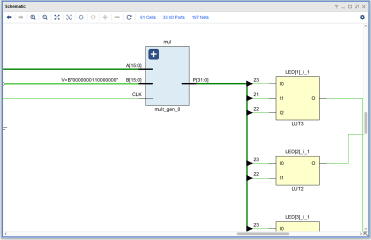

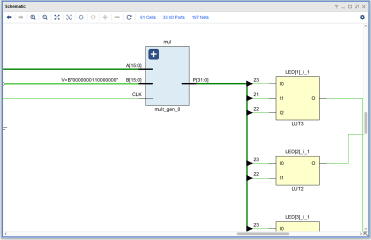

合成後の回路図も確認しておきます。乗算器が追加され、ポートBに1.5の定数が接続されています。元々は13〜15ビットでLEDを点灯させていたのを位取りで21〜23ビットに変更しています。

ファンクションジェネレータの出力を1.5倍にした時と同じLED表示になりました。正常動作しています。

3月18日

MIDIインタフェースのパネル加工です。5ピンDINのMIDIコネクタを固定する穴加工し、L字金具を2個作製しました。

ユニバーサル基板にパネルをL字金具で固定します。DR8に仮固定してみます。問題なく固定できました。肝心のMX16C450(UARTコントローラ)はEbayで購入済みです。

少し前から気になっていたMC80+のLED表示ですが、1つだけ暗いです。以前はたたくと直っていたのですが(笑)。

パネルを外して、コネクタを挿し直しました。接触不良だったようです。直りました。

3月24日

FPGAにDDSの論理をダウンロードしてみます。スライドスイッチで音程を変えられるようにしました。

まず、音として聞くことのできる64分周モード、440Hzです。続いて、DCOのROMテーブルを読み出す*64モードです。28160Hzです。正常に動作しているようです。その他の周波数も9ビットのTOSよりも良いようです。

Ebayで購入したDR8用のUARTコントローラ(MX16C450PC)が届きました。

早速、DR8のMIDIボードに取り付けます。

MIDIクロックモードで同期させました。借りているお手本ボードと同じ動作になりました。

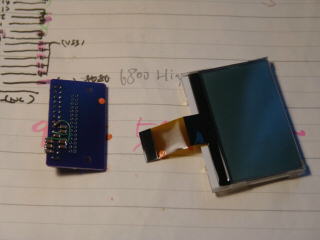

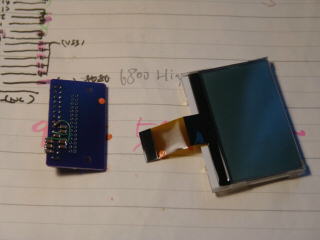

DOC用の9bit/DDS化ですが、論理に余裕があればソフトマクロCPUのMicroBlazeを入れてユーザインターフェースを制御したいと思います。下はMSP430のUSB−MIDIでも使用した128x64のLCDです。SPIモードでも動作するので、microblazeに繋げたいです。フレキ変換基板にコンデンサを取り付けておきました。

アマゾンで購入の5V−>3.3Vレベル変換基板です。MC80+のバスは5Vのため、これで3.3VにシフトしてFPGAに接続します。MC80+バス入力の26ピンのコネクタも取り付けました。

元々はVOTRAXのSC−01音声合成ボード用の26ピンケーブルはMC80+バスと同じ信号線なので、レベル変換が正しく動作しているかオシロで確認しました。正常動作しています。

3月25日

A−880(MIDIパッチ)を介してMSP430のMIDIを接続します。とりあえず、最小限の接続です。

MIDI出力はSP−808に、入力はSK−88にそれぞれ接続しました。

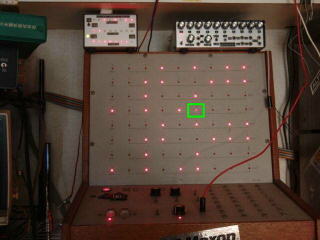

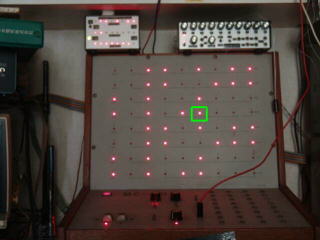

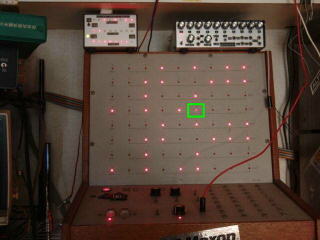

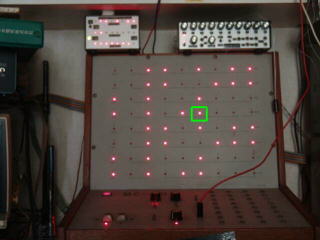

レベル変換したMC80+バスをFPGAに接続します。スライドスイッチで1〜8チャンネルを選択して、MC80+のノート情報をラッチしてボード上のLEDに表示させる論理を書き込みました。PCからMSP430経由で音出しして、MC80+のLED表示と比較します。正しく、FPGA内にラッチされてることを確認しました。

3月26日

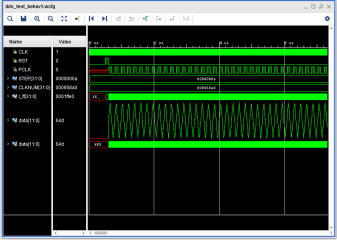

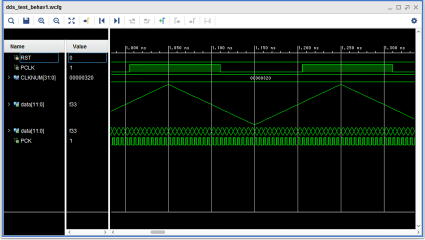

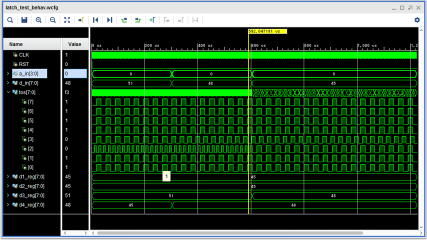

ノートをラッチする論理にDDSを8個組み込んで、シミュレーションを行います。8本のtos信号を出力します。これがDOC用の64倍クロックです。

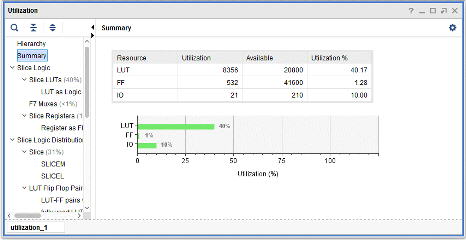

DDSが8個入るか心配でしたが、LUTが40%くらいの使用量です。

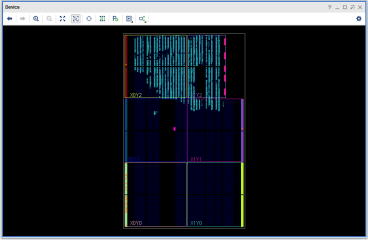

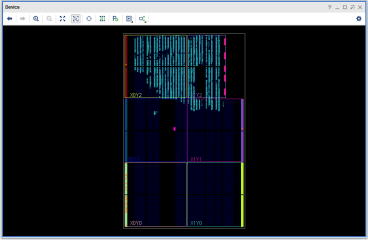

デバイスの図です。まだ実装していないのはXADCを使ったCV入力と、ポルタメント制御です。容量に余裕があればMicroBlazeを使ったユーザインターフェースも実装できるかもしれません。

3月27日

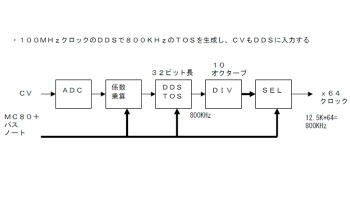

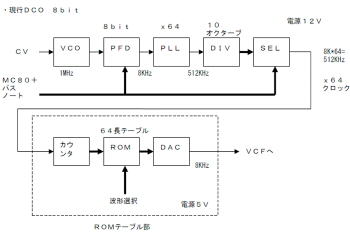

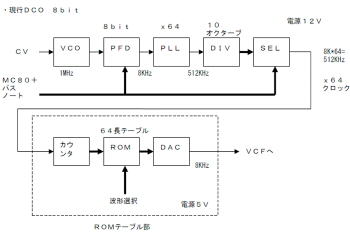

DOCのDDS化の方針です。はじめに現行のDCOのブロックは以下です。CVは外部からの変調入力でLFOを入力すればビブラートがかかります。DIVはバイナリカウンタでオクターブを生成します。SELはオクターブを選択するセレクタです。ノートデータをデバイダとセレクタのデータに変換している部分は省略しています。破線内はカウンタで波形テーブル(2732)を読み出している部分(5V電源)でこれを残し、前半の8ビットでTOSを作っている部分(ここは12V電源)をDDS化してTOSの音程を高精度化します。

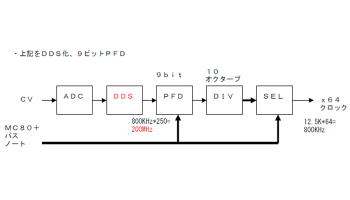

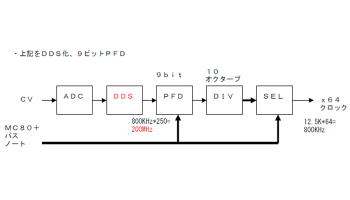

上記のVCOの部分をDDSで置き換えて、9ビットのデバイダでTOSを作る方法です。この方法ではDDSの出力が200MHzで元クロックはもっと高い必要があり、実現できません。

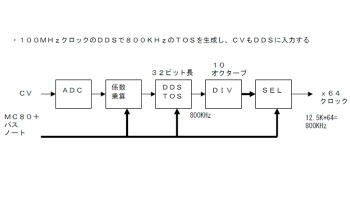

以下はDDSでTOSを作り、CVもDDSの設定値に加算して作るブロックです。この場合は100MHzから800KHzを生成すれば良いのでFPGA内に実装可能です。CVの係数乗算部にノートデータが入っているのは音程によってCVの効きが異なるのを補正するためです。