TK80/BSの

シンセシステムを復活/拡張したい〜

その20

FPGAでDCOのDDS化

2018年

2018年

3月31日

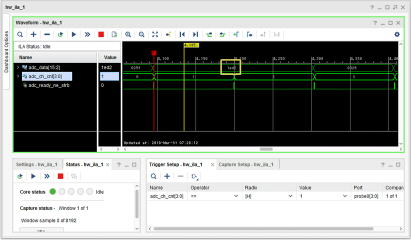

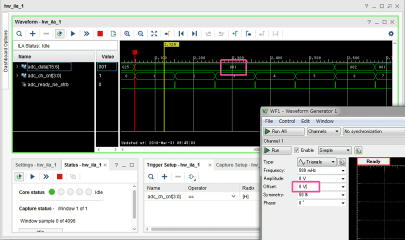

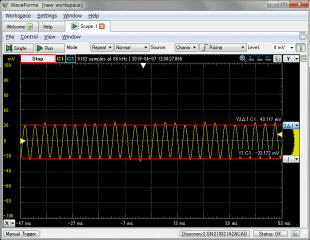

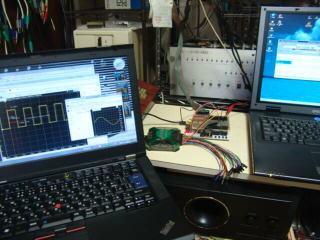

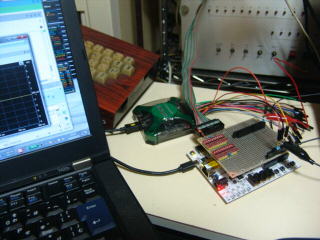

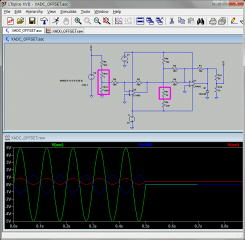

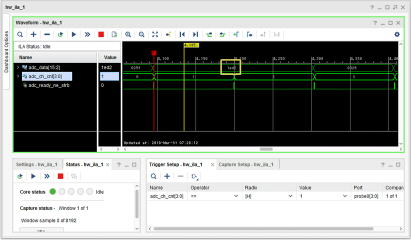

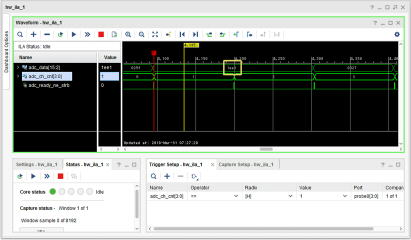

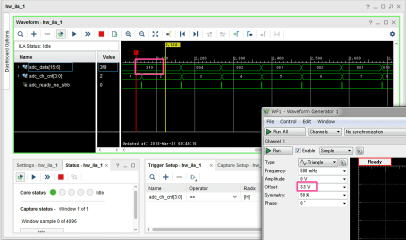

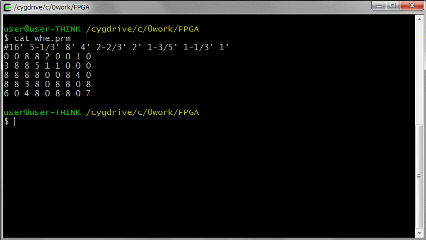

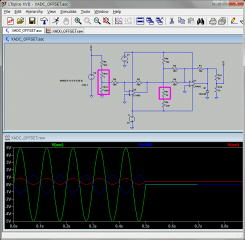

この週は土曜のみの作業でした。FPGAのXADC(ADC)の動作のノイズの確認をします。アナログディスカバリで電圧を出力して、XADCポートに接続します。

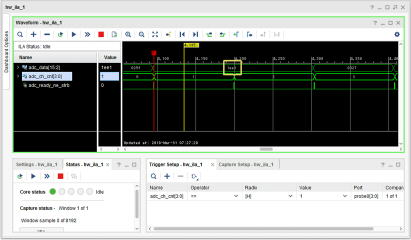

Vivadoのロジアナ機能を使って変換値を確認します。同じ電圧で最大、最小値からノイズ分を確認します。12ビットの内、2ビットくらいがノイズ分のようです。

2ビットを落として10ビットで、レベルを0〜3.3Vに振ってみます。0x001と0x3f9で、ほぼ10ビット一杯に振っています。良いようです。

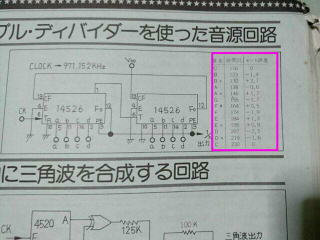

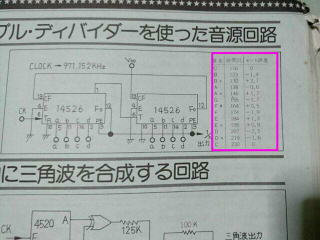

現行DCOのデバイダの分周比は”エフェクター自作&操作術'81”に載っている値と同じで、これにはセントエラーも載っています。このエラーを無くすのが今回のDCOのDDS化の目的です。

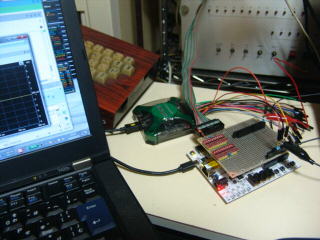

64分周モードでMC80+バスに接続して、SP−808の仮想アナログシンセの音とミックスして音程の確認をしました。mp3はこれです。SP−808、FPGA−DDS、2つのミックス、現行DCO、現行DCOとSP−808のミックスの順にドレミ〜が鳴ります。DDSで生成した音程は市販のシンセとズレが無いことを確認しました。

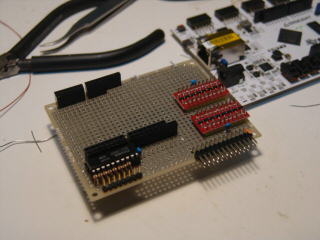

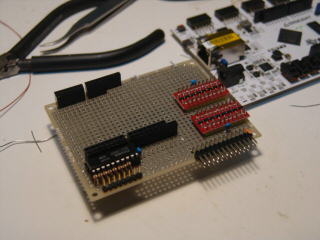

DDS化に伴い、DCO内蔵の波形データも拡張する予定です。現在のROMは2732ですが、これを手持ちの2764に交換します。ただし、ピン数が24−>28ピンと多くなるため、工夫が必要です。

ROMは中古のため、ROMイレーザで4個づつ消去しました。

ROMライタで消去されたことを確認します。新しい波形データはホイール・オルガンの音をまねして作る予定です。

4月7日

ヤフオクで3.5mmプラグを30個購入しました。手持ちと合わせて32個です。16本のパッチケーブルが作れます。DDS用です。

VK−8Mを置く台をSP−808の横に設置しました。

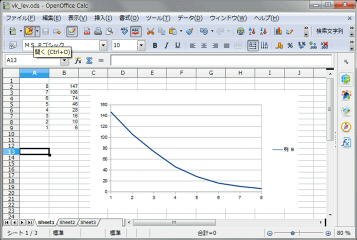

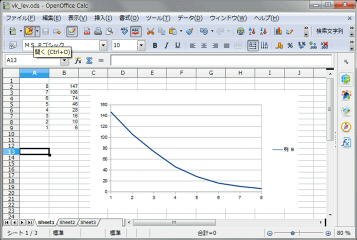

DCO用のROMテーブル作成の準備です。SK−88で鳴らして、ドローバの位置と出力レベルを確認します。

順番にレベルを確認していきます。

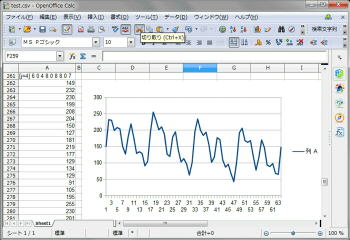

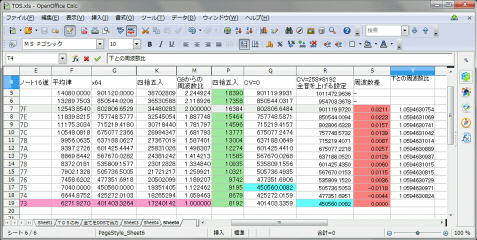

8〜1までレベルを記録してグラフを作りました。ROMテーブルの生成プログラムにレベル設定を追加しました。

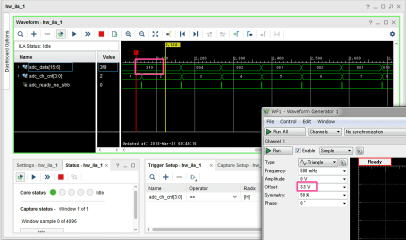

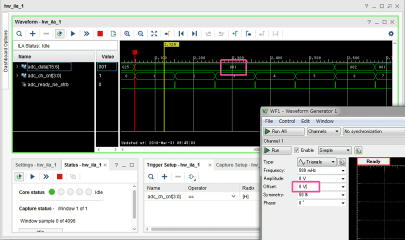

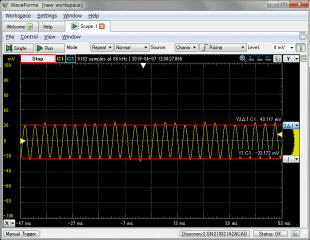

DDSの論理にCV入力を追加します。アナログディスカバリでLFOを作り、DDSを変調してテストします。

4月8日

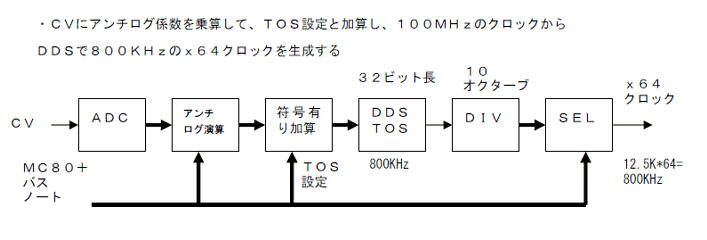

CVの入力にアンチログ演算を入れます。8192に2の12乗根を半音毎に乗算してCV値に乗算します。ARTY評価ボードのA0〜A5は3.3V入力ですが、8192は変調幅を約5半音に調整します。演算後のCVはDDS設定値に加算できます。この演算しないと音程が崩れます。これはDDSが昔で言うV/Hz系の発振器だからです。

上記の論理を組み込み、動作確認します。SK−88といっしょに鳴らして、音程を確認します。良いようです。

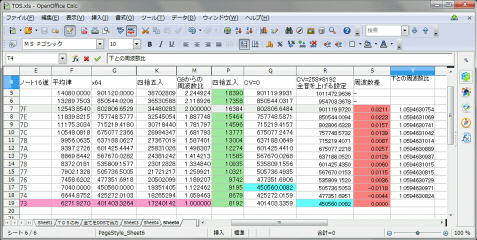

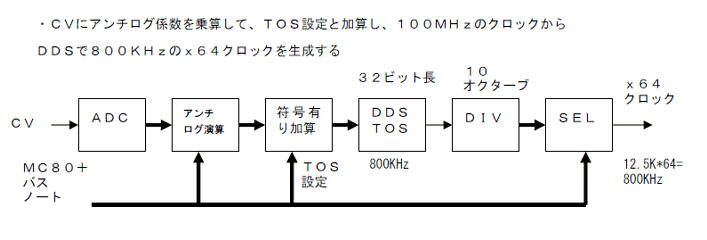

アンチログ演算を追加した新しいブロック図を作成しました。現在、データのラッチ部と以下の8個分がFPGAに実装されています。

PCからMSP430のUSB−MIDI−>MC80変換を介して、4chで音出ししてみました。DCOの代わりにデバッグモードの64分周の方形波で、CV変調は無しです。後段は8chアナログシンセです。MP3はこれです。

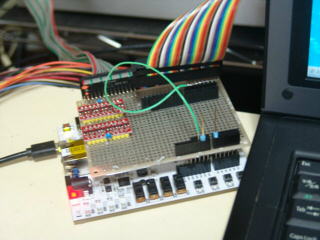

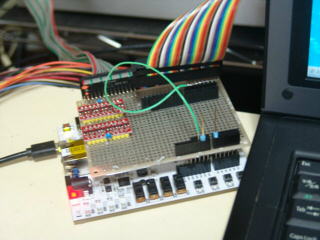

x64クロック出力にHCT245を追加しました。信号をケーブルで長く伸ばして実験していると、FPGAが壊れる可能性があります。HCTでは出力レベルもDCOと同じ5Vにできます。

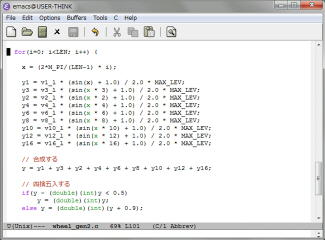

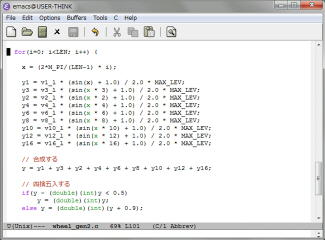

ROMテーブル作成プログラムにドローバレベルを設定ファイルから読み込む機能を追加しました。ただし、8’を基準に作ると5−1/3’は1.5倍で64長テーブルに入らない、また、16’は上側の半波になってしまうため、16’を基準に波形を作成します。16’に対する8個のドローバの周波数比は1、3、2、4、6、8、10、12、16です。出力はCSVで合成波を出力します。本来は1/2、1.5、1,2、3、4、5、6,8です。合成部は以下のようにしました。

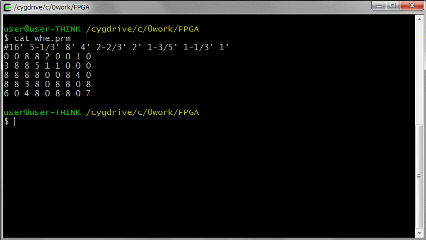

設定ファイルは以下のようなテキストファイルです。

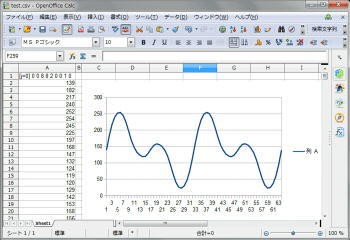

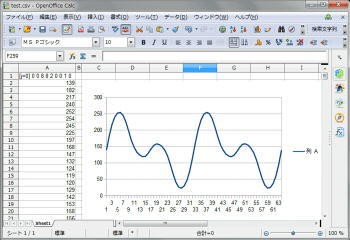

オープン・オフィスのCalcに読み込んで、波形を確認します。ドローバレベル008820010の波形です。

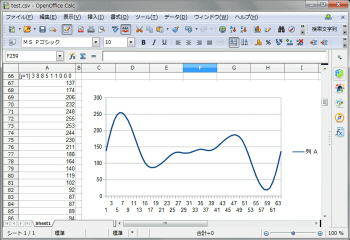

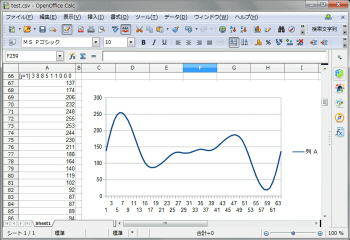

続いて388511000の波形です。

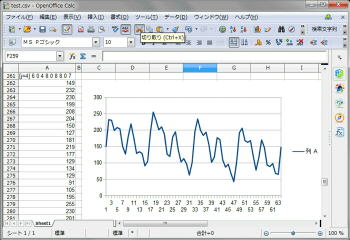

604808807の波形です。波形を集めて、インテルHEXに変換すればROMライタで書き込めます。

4月14日

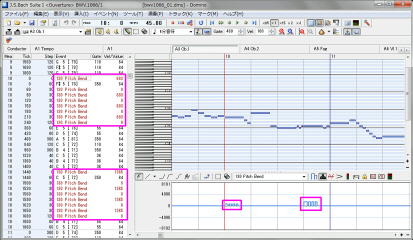

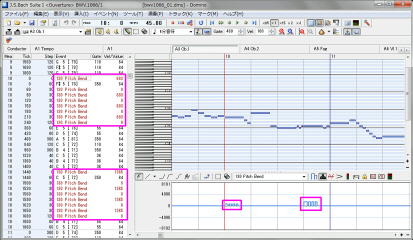

久しぶりにMSP430のUSB−UART−>MC80+のプログラムを修正しました。手持のBACHのSMFファイルの中にピッチベンドを使っているものがあり、これに対応させました。ただ、DCO側は半音単位でしか音程を調整できないため、ギターのチョーキングのような細かい制御はできません。

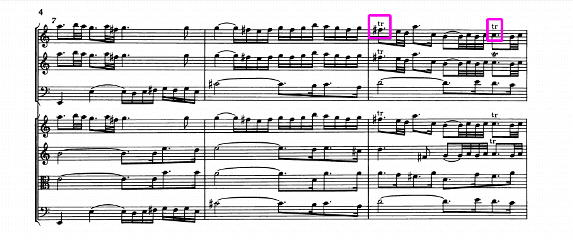

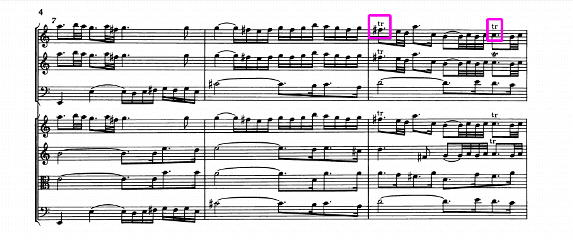

以下、ピッチベンドが使われている管弦楽組曲1番、オーボエのパートです。トリルの部分にピッチベンド使われています。ピッチベンドの仕組みは予めピッチベンドセンシティビティによってピッチベンドの幅が指定され、その後に送られるピッチベンド値によって音程を上下させます。ここではピッチベンドセンシティビティは12、ピッチベンドが683/1365で半音と全音の幅になっています。ここにピッチベンドの早見表があります。

フリーの楽譜で確認しました。トリルであれは、半音単位の制御なので、問題なく処理できます。1声と4声で録音しました。MP3はこれとこれです。

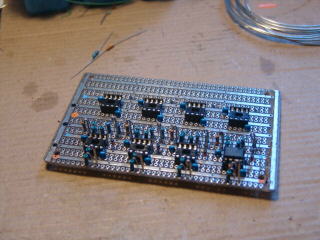

DCOのDDS化用の部品をマルツと秋月から購入しました。オペアンプを使ったCVオフセット回路を組み込むため、電源トランスも購入しました。電源電圧は+−5Vです。右はオペアンプ、ICソケットなどの小物部品です。

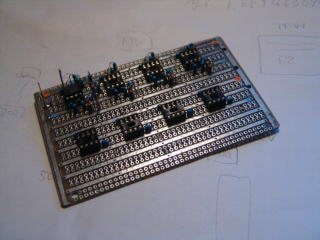

CVのオフセット回路用のユニバーサル基板は手持ちのものを使います。

4月15日

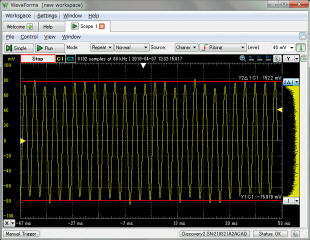

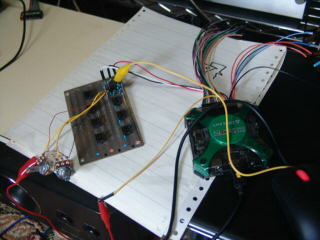

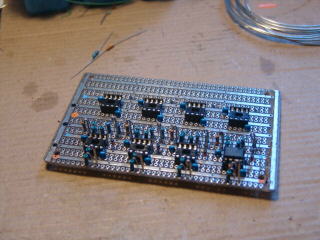

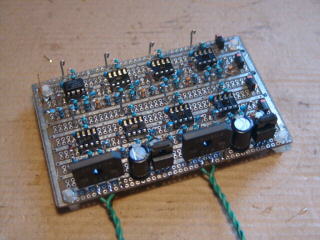

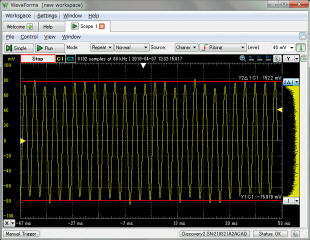

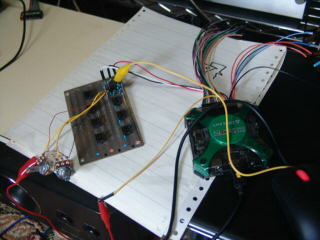

CVのオフセット回路を1ch分だけ作製してテストしました。+−5Vの電源なので、アナログディスカバリから電源供給できます。電源、ファンクションジェネレータ、オシロスコープがアナログディスカバリ1台で使えます。

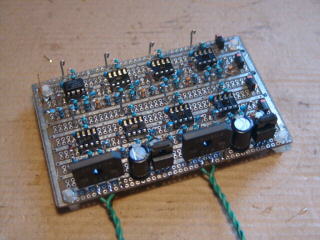

1ch分、作製完了しました。あと、7ch分作製します。

4月21日

先週の続きです。CVのオフセット回路を4ch分作製しました。回路は右です。赤枠はボリュームです。+−5Vの入力を0.5Vのオフセット付きで最大1Vまで調整します。

ARTYボードのアナログ入力のA0〜A5のアッテネータを取り外し、A6〜A11と同じく無しにします。右回路図の上側の2.32Kオームは取り外してショートし、下側の1Kオームは取り外します。代わりにCVオフセット回路基板に2.2K−1Kオームを実装します。

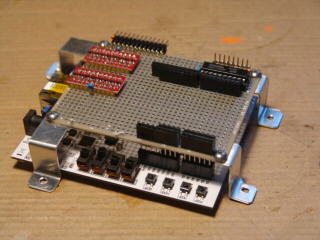

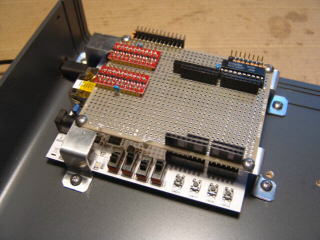

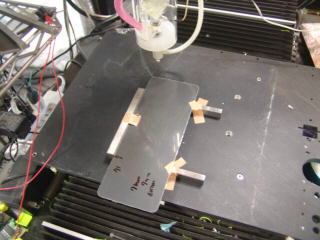

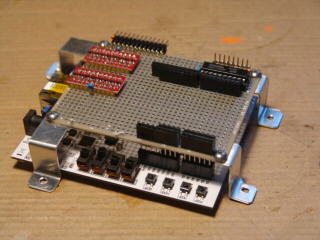

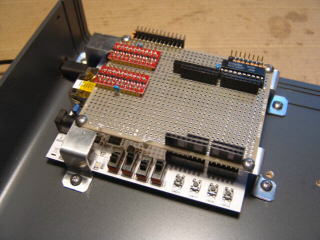

ARTYボードには取り付け穴が無いので、上に重ねているのレベル変換−クロックドライバボードで支えます。アルミ板でステーを作製しました。

下側ケースには部品の取り付け穴開け加工をします。

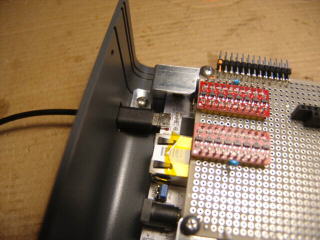

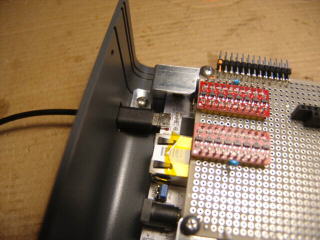

レベル変換−クロックドライバボードのMC80+バスはリアパネルから、ARTYボードのUSBコネクタは側面になるので、下ケースの側面に穴開けしました。

4月22日

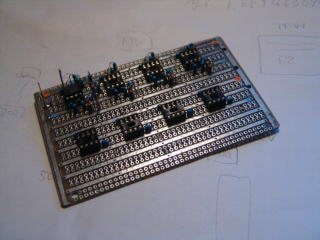

CVのオフセット回路を8ch分作製し、電源回路も追加しました。

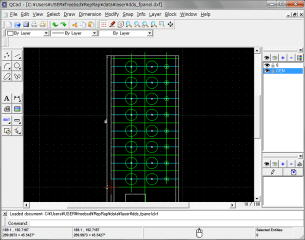

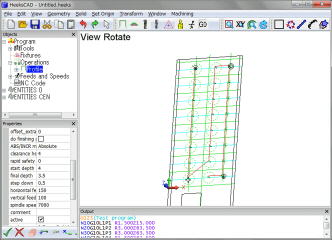

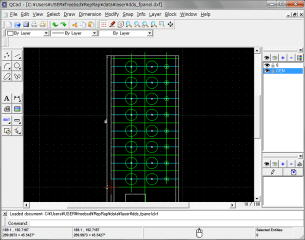

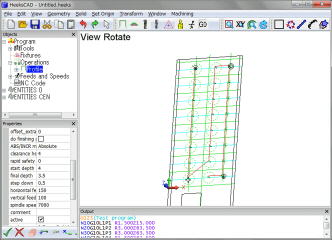

フロントパネルの穴開けを行います。Qcadで図面を書いて、HeeksCNCでGコードを生成します。

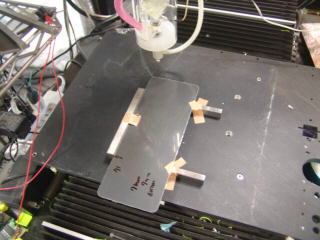

レーザ加工機でセンタ穴を塗装面にマーキングをします。ポンチを打って、ボール盤で穴開けします。左側のスペースはMicroBlazeのSPIで制御予定の128x64ドットのLCDパネルを取り付ける予定です。まだ、DDS部とMicroBlazeを組み合わせて合成できていません。元々DigilentのWEBページから持ってきたXADCのIPが、見つからないというエラーです。

CVのオフセット回路をテストします。トランスを取り付け、とりあえず4ch分のみパネルのボリュームとジャックに接続しました。オフセットとCVのモジュレーションの調整が正しく動作することを確認しました。