TK80/BSの

シンセシステムを復活/拡張したい〜

その23

DDSのユーザインタフェース作製

ラダーフィルタの準備

TK80−>MSP430−>MIDI出力

2018年

2018年

6月9日

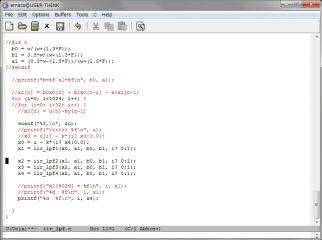

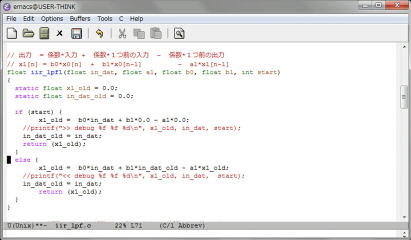

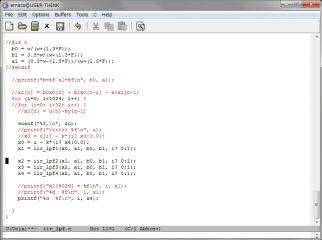

ここにラダーフィルタのデジタル化のページがあります。このページではVCFの代わりに計算機で係数の計算が簡単になるように、フィルタの式がまとめられています。上手く動作すればFPGA内に組み込めます。このページを参考にPCでプログラムを作成しました。式の構成は1次のIIRのLPFを4個直列に接続してフィードバックを掛けてレゾナンス制御します。サンプリング周波数は48KHzです。下のプログラムでは1次のLPFを4回呼んで、フィードバックを掛けています。ダイオードを使った実際のラダーフィルタは非線形になり、このフィルタとは特性が違います。このページの参考文献の中にダイオードラダーを使ったフィルタが載っています。後で気がつきましたが、x4の式が間違っています(笑)。

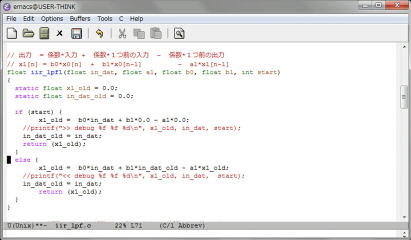

下は1次のLPF部です。初期時N=0の時にN−1の時の値を0にする必要があるため、少し工夫が必要です。

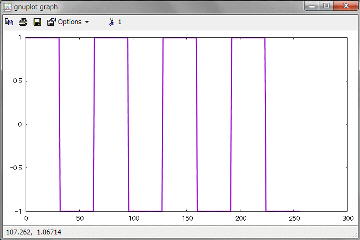

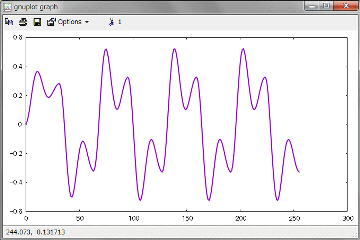

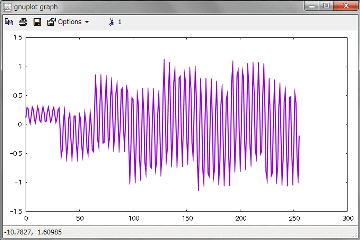

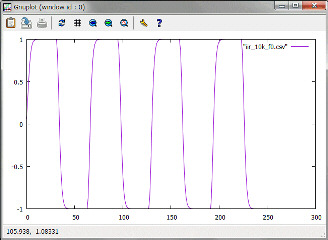

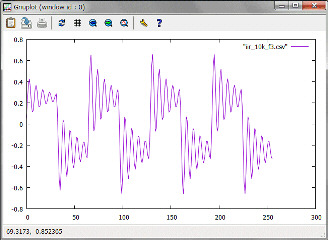

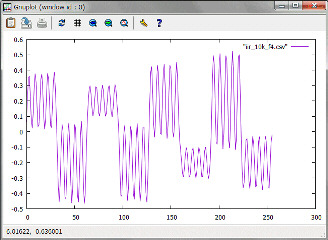

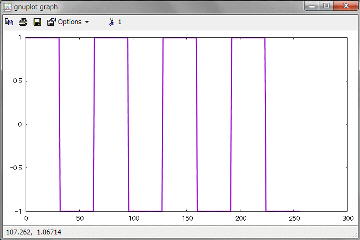

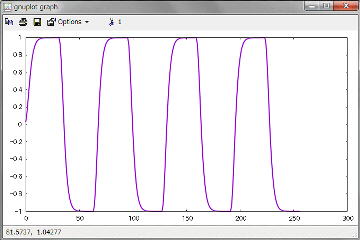

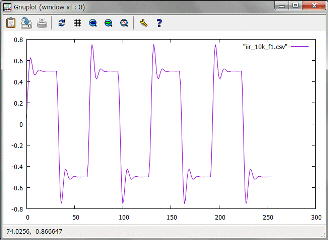

入力信号です。+−1.0V、デューティ比50%の方形波です。32個のデータ毎に交番するので周波数は750Hzです。波形はgnuplotで確認します。

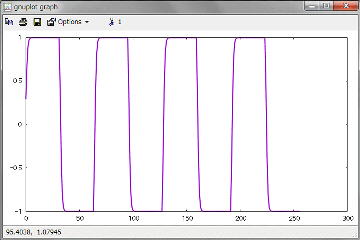

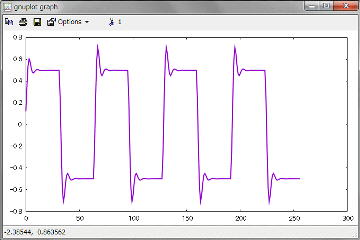

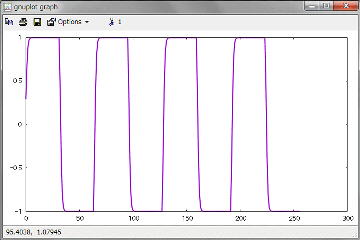

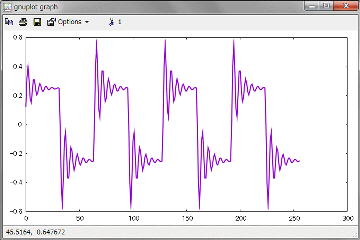

カットオフ周波数20KHz、フィードバック無しの時の出力です。

カットオフ周波数5KHz、フィードバック無しの時の出力です。

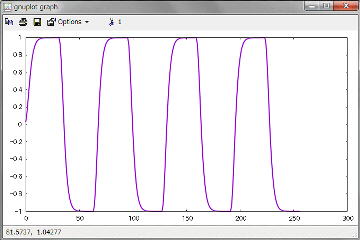

カットオフ周波数2KHz、フィードバック無しの時の出力です。

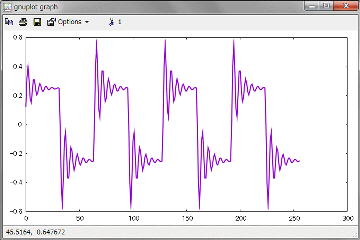

カットオフ周波数2KHz、フィードバック係数3.0の時の出力です。フィードバックが掛かると、出力レベルは低くなります。

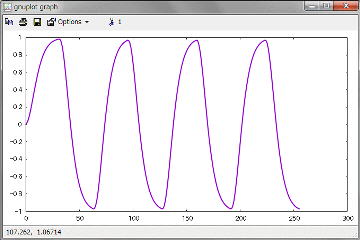

カットオフ周波数10KHz、フィードバック係数2.0の時の出力です。

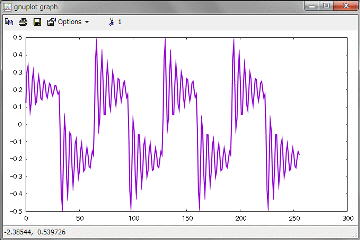

カットオフ周波数10KHz、フィードバック係数3.0の時の出力です。

カットオフ周波数10KHz、フィードバック係数4.0の時の出力です。レベルは0.5VP−Pくらいになっています。

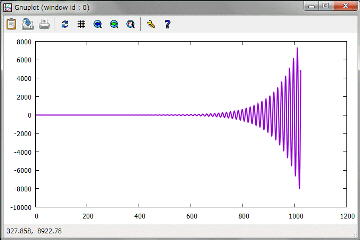

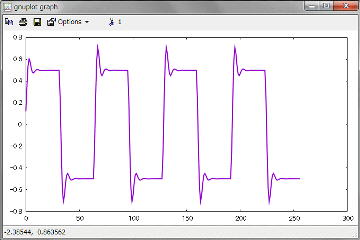

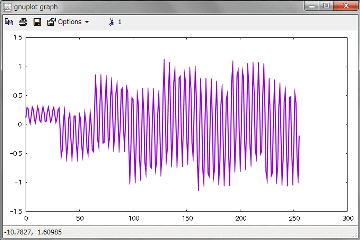

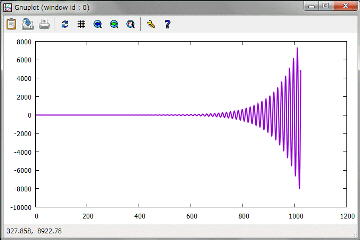

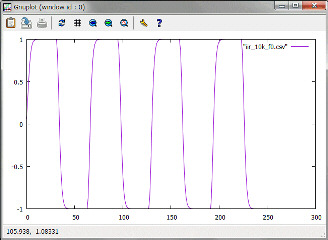

カットオフ周波数10KHz、フィードバック係数5.0の時の出力です。自己発振が始まりかけています。シミュレーションでは安定した振幅で自己発振することはできません。

上記の状態を続けていると、振幅は8000を超えて、どんどん大きくなっていきます。

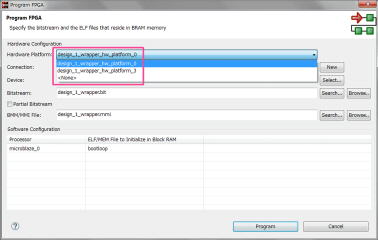

先

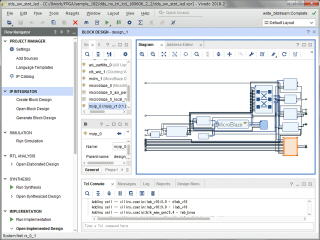

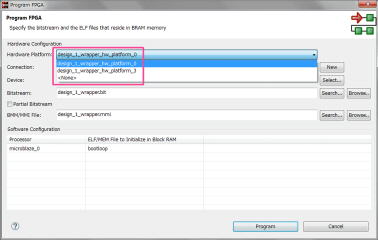

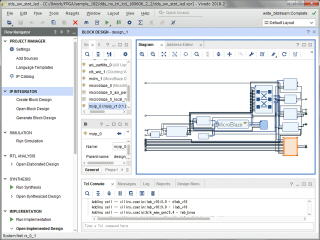

週のVivadoのSDKの思った通りに動かない場合がある件ですが、FPGAへの書き込み時にxx_hw_platform_xが選べることが分かりました。選択したxx_hw_platformがプログ

ラムと結合されて、FPGAへの書き込まれます。xx_hw_platform_xを消すと欠番を埋めるように番号が使われるので、間違えないように、生成された時間を確認して、最新のものを選びます。

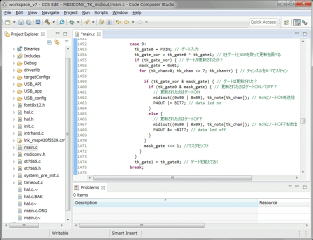

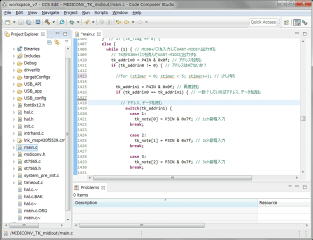

FPGA内のMicroBlazeでLCDとスイッチを使って、DDSにユーザインターフェースを追加しました。設定項目はノートのオフセット、CVの効き調整、LCDのコントラスト、エラーLEDのクリアの簡単なユーザインターフェースです。オフセットやCVの効き調整は簡易IPのslv_reg[3:0]経由で制御します。スイッチ入力は割り込みではなくポーリングです。MSP430と違い、スイッチを早く動かすと反応しません(笑)。青色LEDのINFO1はハートビートで点灯します。赤LEDはERRORでオフセットでエラーが発生した時に点灯します。もう一つの青色LEDのINFO2は未使用です。

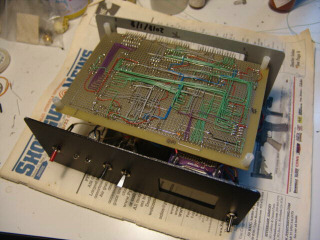

友人Sから貰ったDR4のMIDIインターフェースボードをDR4に組み込んでみました。DR4からMIDIインターフェースボードが認識されましたが、ボードに載っているH8のファームのバージョンが1.06のため、メニュー項目が少ないようです。

6月9日

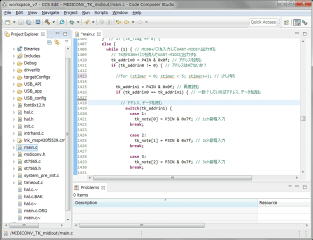

MSP430のUSB−MIDIのプログラムを少し修正しました。修正したのはノートのオフセットを予め設定された値にする機能です。設定スイッチは割り込み駆動のため、オフセットのスイッチ操作1回に半音づつしか可変できないため、大きくオフセットする時は面倒でした。また、TK80からのデータ出力中はMSP430は何もしていなので、ポートを入力に変えてMC80+バスをキャプチャし、UART−MIDIにデータ出力する機能を追加予定です。

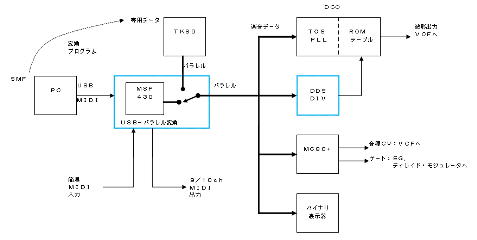

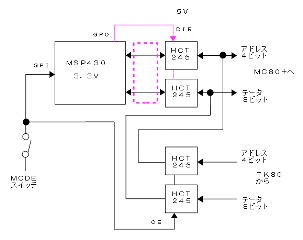

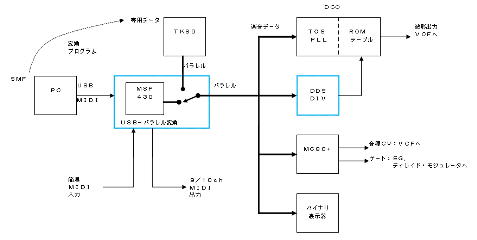

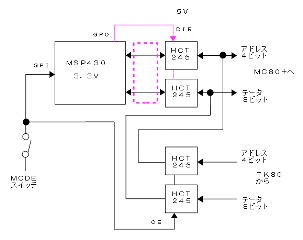

上記オフセットですが、下はMSP430とDDSのブロック図です。元々はTK80とDCOのみのシステムにUSB−MIDIを追加したので、MSP430内で以前のTK80と合わせるためにマイナスにオフセットしています。そこにDDSが加わったため、オフセットをキャンセルする必要があります。また、DCOのトーンホイールテーブルは1オクターブ高いなど、煩雑です。

ソニーのリズム音源を組み込んだ旧リズムシーケンサですが、出力レベルが大きい(2.5Vp−p)ので、ボルカビーツと同じレベル(0.3Vp−p)位に調整しました。

リズムシーケンサにパターン・シーケンサにデータを書き込んで、久しぶりにTK80で録音してみました。TK80−>MSP430−>DDS−>DCO(ROMテーブル)−>8chシンセの接続です。MP3はこれです。このソニーの音源の難点は各音源のレベルが個別に調整できないことです。

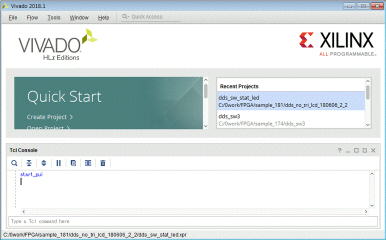

Vivadoが2018.1になったのでインストールしました。2018.1ではフリーのIPが増えていて、I2SやSPDIFなど、デジタルのシンセサイザに使えそうなものもあります。ただ、各IPはAXI−Streamバス経由で接続する必要があるようです。

2017.4で作成したDDSの論理は使用している各IPをアップグレードして合成、インプリできました。

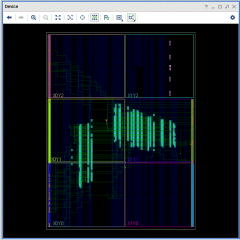

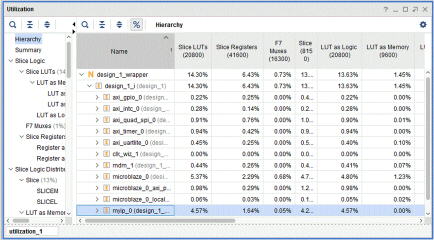

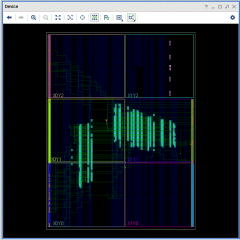

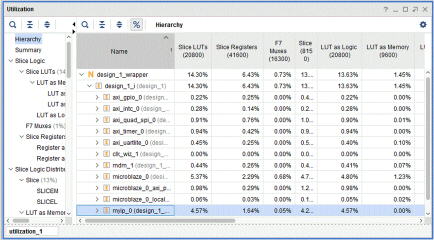

ロジック使用率です。

6月17日

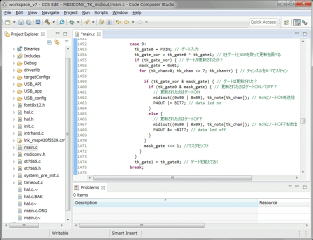

この週末は日曜のみの作業でした。MSP430のUSB−MIDIにTK80から音出し中にアドレスの変化を検出して、ノートとゲート情報をMSP側に取り込み、MIDIに出力するコードを追加しました。

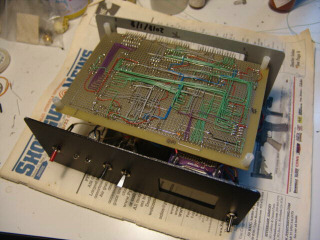

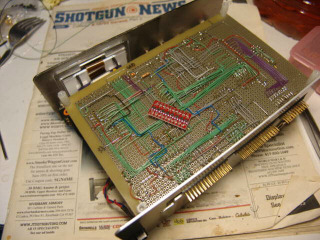

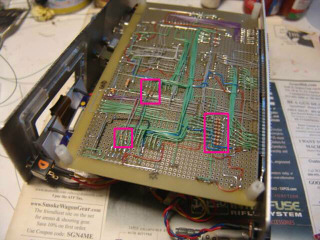

ハードウェアの修正を開始しましたが、5V−>3.3Vのレベル変換が必要でした。

今回の修正はMSP430とMC80+のレベル変換のHCT245がMSP側にも向くようにDIRをGPOで制御します。ただ、MSPは3.3Vなので、そのまま接続できません。赤点線内に5V−>3.3Vのレベル変換が必要です。

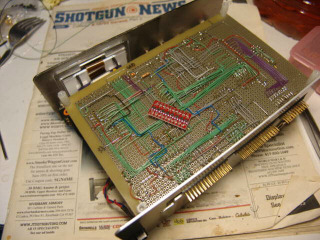

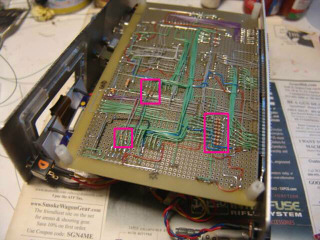

以前にDDS用に購入した8ビットのレベル変換が1枚余っていました。アドレス分の4ビットが足りません。WEBを調べていると、ここに情報がありました。ここによると、MSPの入力端子に付いているクランプダイオードの仕様を守って抵抗を直列に入れてもいいということです。これなら簡単です。

6月23日

先週の続きです。上記のページを参考に3Kオームの抵抗をデータとアドレスバスに入れて、5V−>3.3V変換します。

6月24日

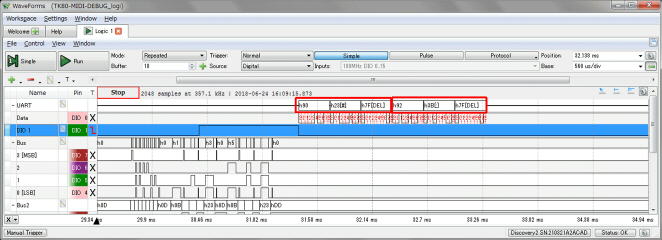

TK80から音出しして、作成したMSP430のプログラムを介して、SC−88へMIDI出力します。

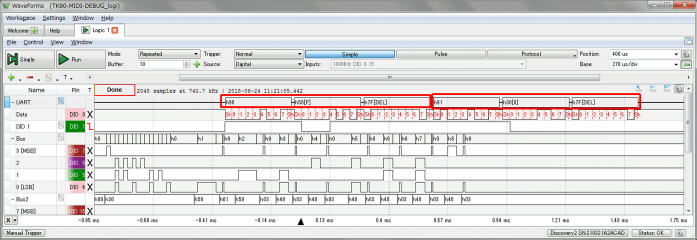

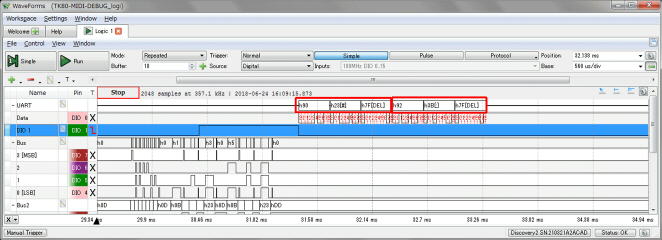

上手く動いてません。アナログディスカバリを接続してMC80+バスとUARTのタイミングを確認します。

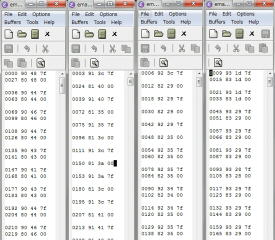

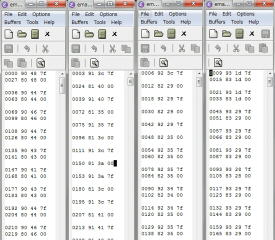

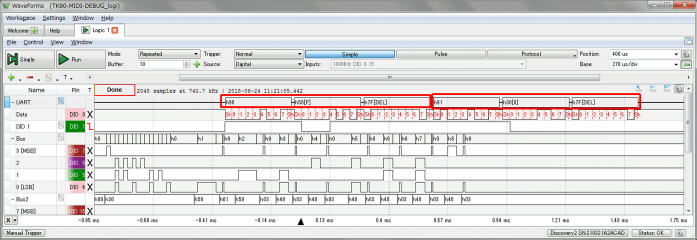

まず、4ch出力時にアナログディスカバリのUARTプロトコルアナライザでMIDI出力データを取り込み、データをチャンネル毎に整理して、確認します。アナログディスカバリのボーレートのプルダウンメニューに31.25Kはありませんが、直接値を入れれば設定できます。結果はノートON/ノートOFFが正常にが出力されていません。ノートON/ノートOFFは必ずセットで出現するはずです。

バスタイミングとMIDI出力関数の必要時間を確認します。MC80+バスを解析しながら、順次MIDI出力する方法では処理が間に合っていないことが分かります。先頭で3バイトをMIDIで出力している間に、MC80+バスでは3チャンネル弱出力しています。デバッグ用のP1.5のDO1はMIDIの3バイト出力関数の先頭でHIGHにして終了時にLOWにしています。HIGH幅が3バイト出力するの必要な実時間です。MIDIの31.25Kbpsに比べると、2MHzの8080の音出しの方が断然早いです(笑)。

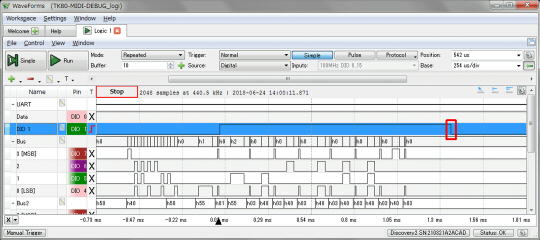

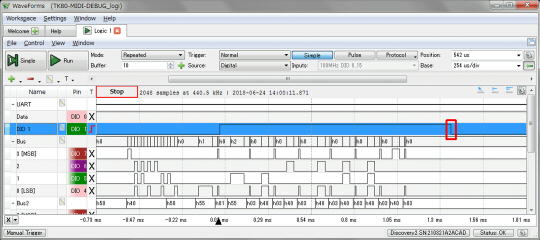

プログラムを修正して、バスの解析とMIDI出力の処理を分けるようにします。TK80の出力するバスは必ず8ch分出力する訳ではないので、単純にバスアクセスの終了が分かりません。ゲート検出でタイムアウトをセットして、タイムアウト発生で最後のゲート検出を検出します。下記のDO1の赤枠はタイムアウトが発生したところです。

タイムアウトが発生したところで、まとめてMIDI出力するようにプログラムを修正しました。これでも偶にイベントが欠落することがあります。動作不良でノートOFFが出ないと、SC−88側で音が残ってしまい、不良が直ぐ分かります。ゲートの幅を測定し忘れましたが、下記のロジアナ波形から、大体2〜3μSecと思われます。MSP430は25MHzで動きますが、タイマ割り込みも動いているため、短いゲートの幅ではポーリングで取りこぼしているのかもしれません。次回、TK80側のプログラムを修正して、ゲートのタイミングを長くすると改善するか確認します。友人Sの作成した8chシーケンサプログラムはバイナリしか残っていないため、逆アセンブルして解析しないといけません。

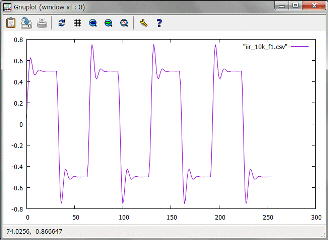

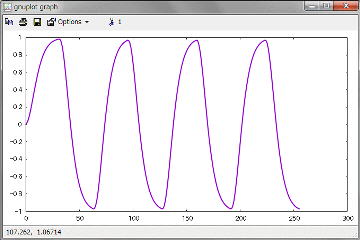

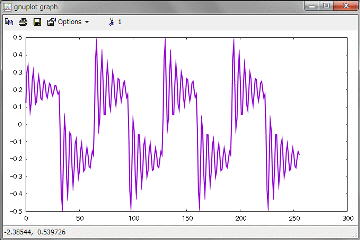

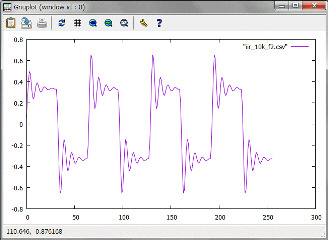

以前に作ったデジタルラダーフィルタの式が間違えていたので、修正して波形を出し直しました。カットオフ周波数10KHz、フィードバック係数0の時の出力です。

カットオフ周波数10KHz、フィードバック係数1.0の時の出力です。

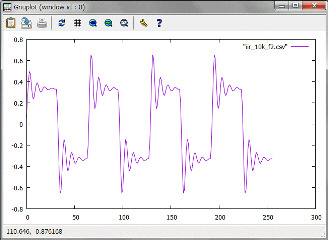

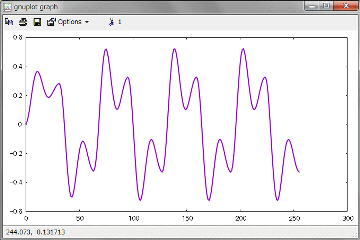

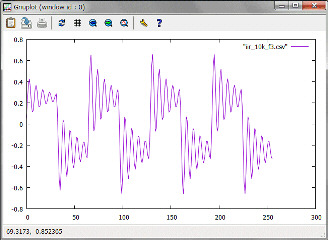

カットオフ周波数10KHz、フィードバック係数2.0の時の出力です。

カットオフ周波数10KHz、フィードバック係数3.0の時の出力です。

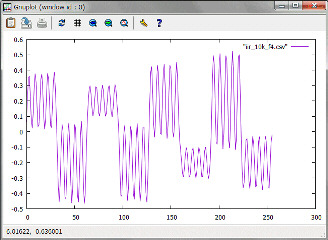

カットオフ周波数10KHz、フィードバック係数4.0の時の出力です。

FPGA開発用のノートPCをアパートに持ってきて、Vivadoの新しいバージョン2018.2をインストールしました。ファイルが大きいのでテザリングでインストールする勇気はありません(笑)。つい、4週間くらい前は2018.1だったんですが。2017.4で作ったDDSの論理は合成、インプリメントできました。