TK80/BSの

シンセシステムを復活/拡張したい〜

その25

DCO用ROMエミュレータの作製

2018年

2018年

7月28日

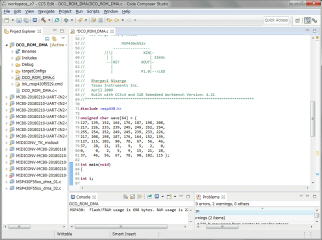

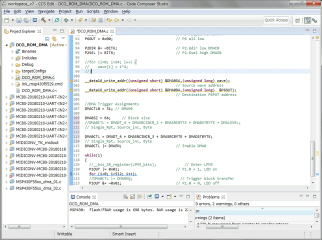

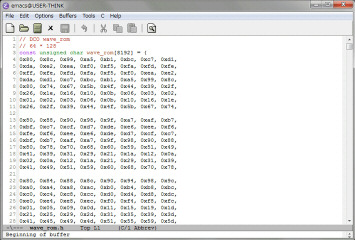

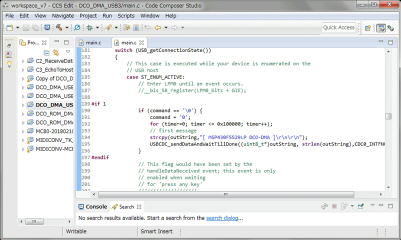

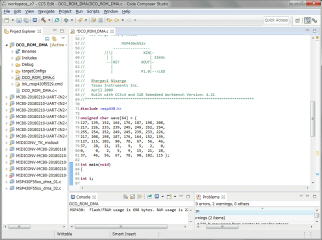

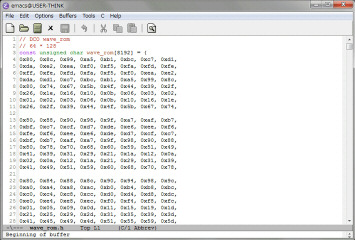

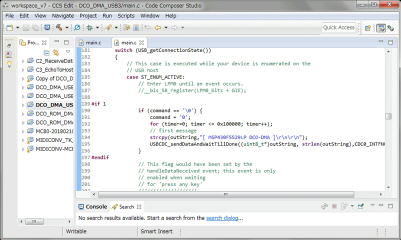

少し前に、DCOのROMを2732から2764に変更してトーンホイールオルガンの波形を真似して64個を追加しました。適当にパラメータを選んだので、使える波形が少なかったです(笑)。ROMも紫外線消去のため、作り直しも面倒です。そこで、手持ちで余っているMSP430F5529ローンチパッドでROMエミュレータを作ることにしました。当初、MSPのポートにRAMを接続してバスを切り替えて使う予定でしたが、MSPのユーザ・ガイドを見ているとDMAが使えることが判明しました。早速、DMAのサンプルコードを見てみます。下はメモリからUARTの送信データレジスタにDMA転送するプログラムです。ROMエミュレータではメモリからデータ出力ポートのデータレジスタにDMA転送すれば良いので、これを参考にできます。

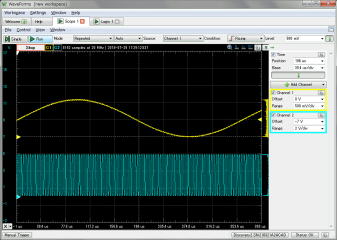

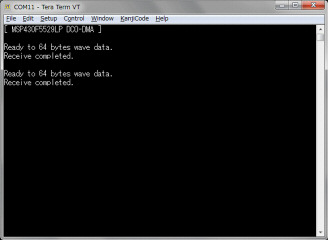

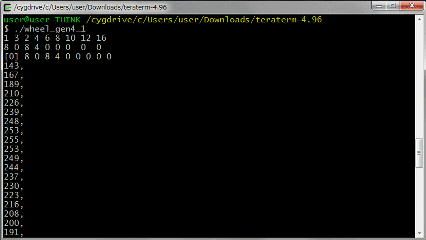

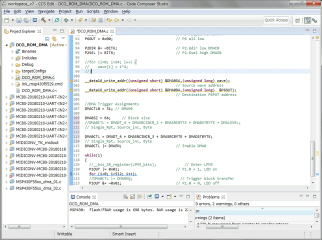

上記のサンプルを参考に外部DMA要求でデータを出力するテストプログラムを作成します。SIN波のデータを配列に入れて、ROMのA0を外部DMA要求信号のDMAE0(P2.6)に接続します。このDMAE0のエッジをトリガにして、単一繰り返し、サイズ64バイト、ソースアドレスはインクリメントモードでDMAを行うように設定します。データはP6に出力します。

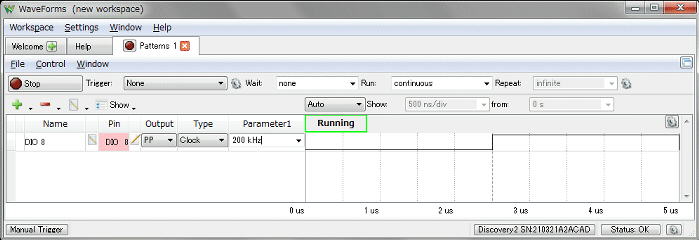

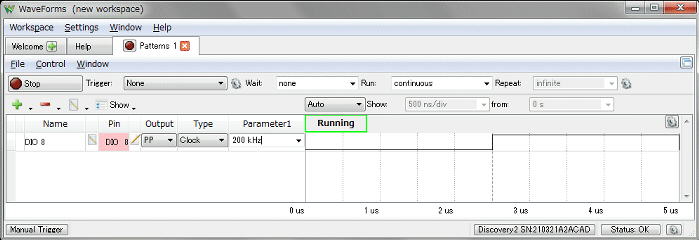

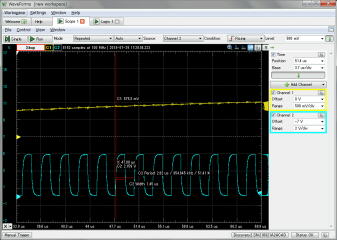

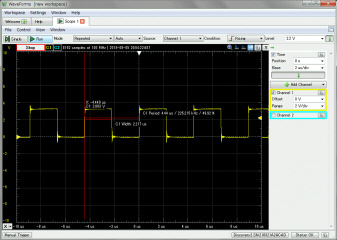

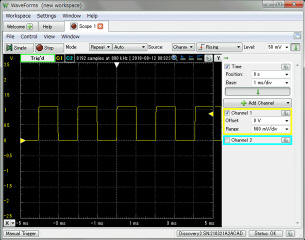

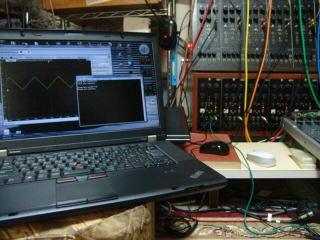

アナログディスカバリを接続して動作確認を行います。

アナログディスカバリのD8をパターンジェネレータのクロック出力に設定して、DMAE0(P2.7)に接続します。

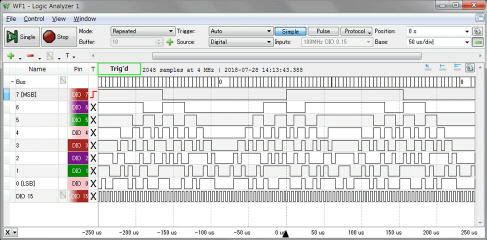

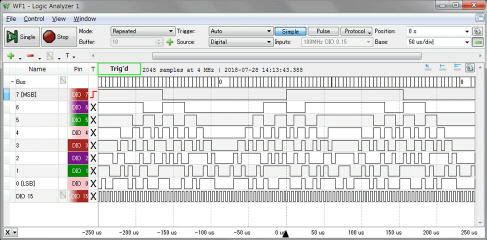

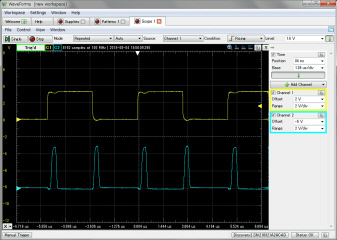

データのP6はアナログディスカバリのD0〜D7に接続してロジアナで取り込みます。DMAE0の立ち上がりでデータが出力され正常に動作しているようです。

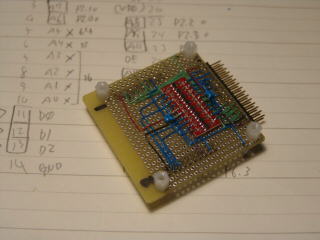

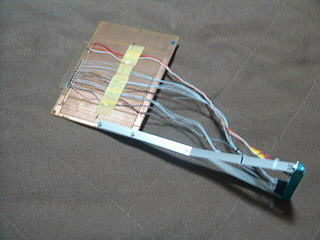

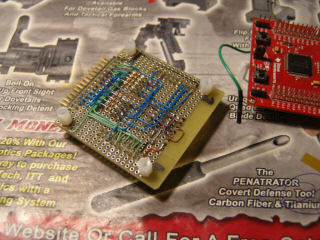

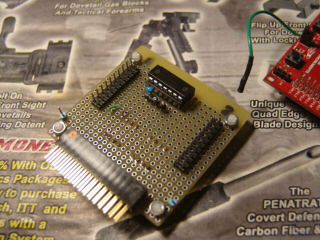

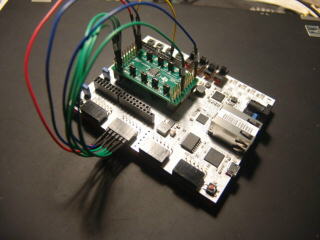

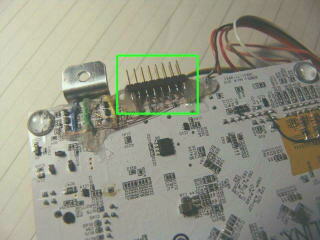

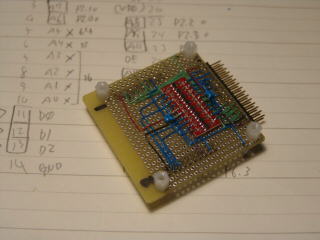

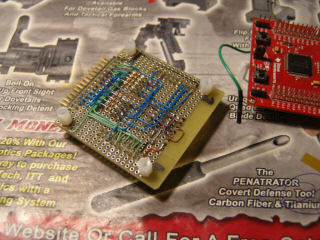

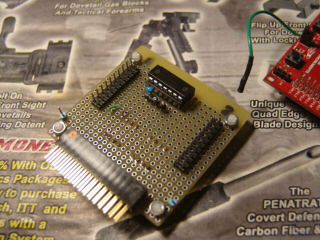

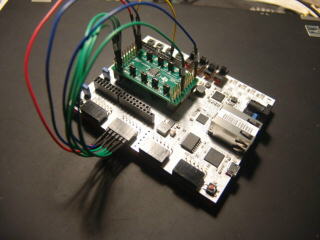

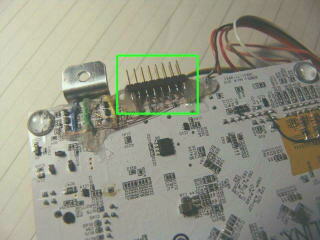

基本動作は問題なさそうなので、ローンチパッドの下に接続するボードを作製します。手持ちの部品を集めて〜

フラットケーブルに30ピンのコネクタを圧接し、ケーブルの先端に28ピンのICソケットをハンダ付けします。ボードの裏に5V−>3.3V変換ボードを両面テープで取り付けました。

ジュンフロン線で配線します。ROMのA6〜A12はフロントパネルからの波形選択信号で、P2で入力します。MSP430に入力する信号は5V−3.3V変換ボードを介してレベル変換します。

7月29日

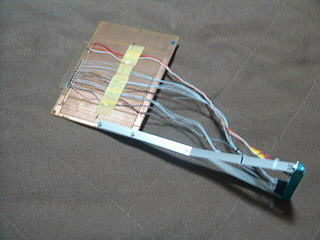

DCOは以前に作製したDCO用のエクステンダボードを介して筐体の外に出します。ケーブルを延長してコネクタの位置を調整して全長を長くしました。

修正したエクステンダボードでDCOが動作するか確認します。8ch全て動作させるには筐体内のマザーボードのコネクタの位置関係でDCO1ではなく、2ch目のDCO2を使います。動作良好です。

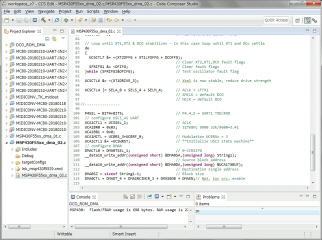

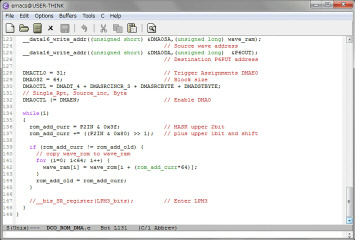

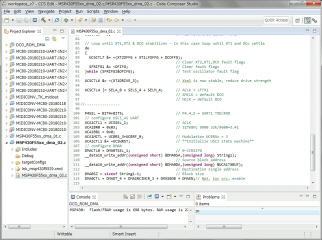

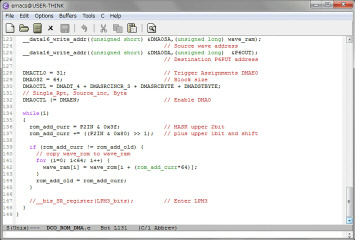

上記のDMAテストプログラムを修正してパネルの波形選択に対応させます。DCOのROMデータ(64バイトx128個分)をデータ文にしてインクルードしてプログラムのROM領域に配置します。whileループ内で波形選択信号に変化があれば、オフセットを計算してROM領域からRAMにコピーします。

動作確認をすると、パネルのスイッチの波形選択が動作せず、信号が全て論理1になっています。最後の127番の波形のみ出力されていました。5V−>3.3V変換ボードは純ロジックは変換できますが、プルダウン抵抗を使っているフロントパネルからの信号は変換できませんでした。変換ボードのHV側入力が10Kでプルアップされているためです。これらの信号は3Kオームの直列抵抗に変更しました。結局、5V−>3.3V変換ボードを通っている信号のはA0(DMAE0)信号だけになりました。

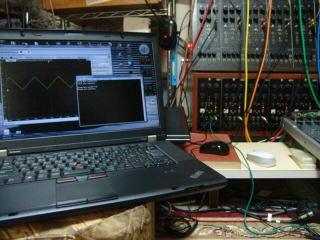

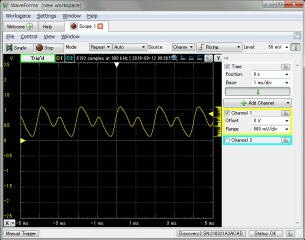

DCOのROMの代わりにROMエミュレータのICソケットを挿して動作確認します。フロントパネルのトグルとロータリスイッチの波形選択信号でROMエミュレータが動作するようになりました。普通のROMが載っているのと同様に128個の波形が選択できます。下は三角波を出力している所です。ちょっとピンボケ。

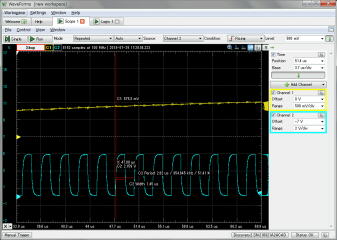

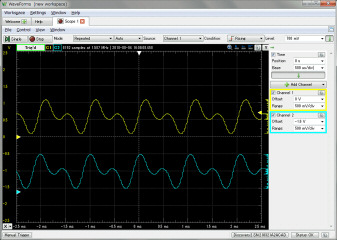

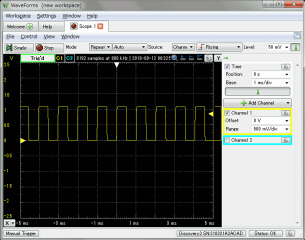

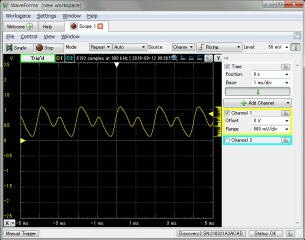

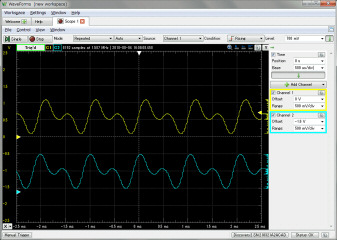

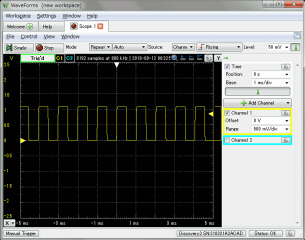

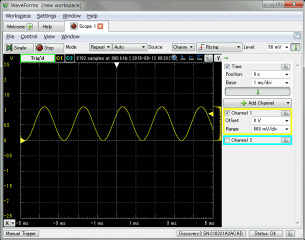

クロックのA0(DMAE0)が約354KHzの時のSIN波の出力です。DMAはクロックの立ち上がりでインクリメントされるため、出力波形はクロックの64x2分の1になるので1オクターブ下が出力されます。次回、プログラムを追加してUSB−UART(CDC)から波形データをRAMに転送できるようにする予定です。

8月4日

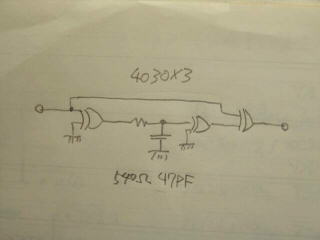

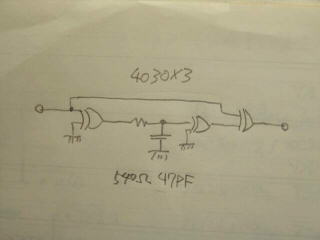

先週、5V−>3.3V変換ボードを通る信号をスキップして抵抗に置き換えました。変換ボードを通っているのはA0の1本だけなので、変換ボードを取り外して、全て3Kオームの直列抵抗に変更しました。また、A0をDMAE0に接続すると音程が1オクターブ低くなるので、A0の周波数を2逓倍する回路を追加します。部品は手持ちの4030(EX−OR)を使いました。

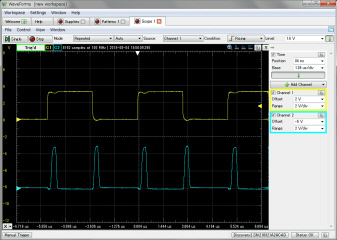

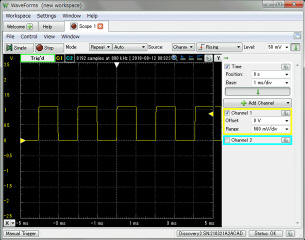

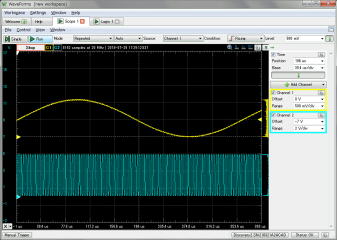

ROMエミュレータをDCOボードに接続して、2逓倍回路を動作確認します。

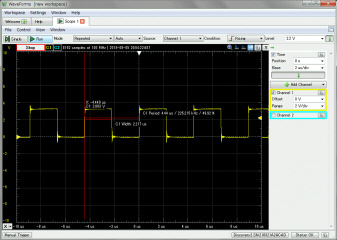

2逓倍回路の波形です。上がA0信号で下が2逓倍出力です。MSP430のDMAE0は立ち上がりエッジで動作するためパルス幅が短くても問題ありません。通常の1chとMSP430のROMエミュレータを使った2chが同じ周波数になりました。

8月5日

ちなみに、2逓倍回路は以下のようにしました。

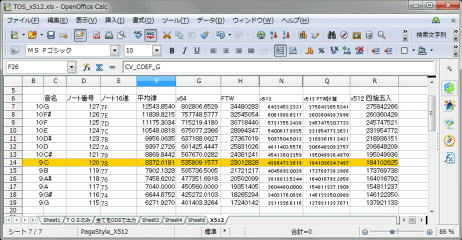

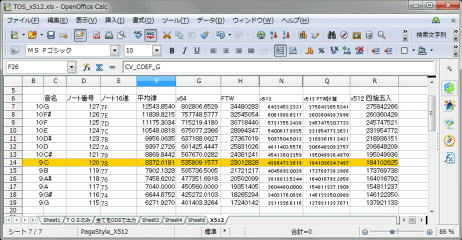

DDSの論理に512倍クロック出力を追加してみます。FPAGに新たにデジタルシンセを組み込んだとき使う音程クロックです。現在のDCOのクロックは64倍ですが、テストとして512倍のクロックを生成してみます。8倍したDDS設定値(FTW)のオープンオフィスの表を作成しました。

512倍クロックとオクターブ分周カウンタも3ビット拡張し、今使っている64倍クロックも同時に生成します。論理を作成して合成、インプリしました。512倍クロックの8本は3色LEDポートにアサインしました。このLEDは凄く明るいです。点灯しているので信号が出力されてるようです。

ch1だけ512倍クロックを外に取り出して、アナログディスカバリで測定します。440Hzの512倍の228.28KHz付近になっていることを確認しました。

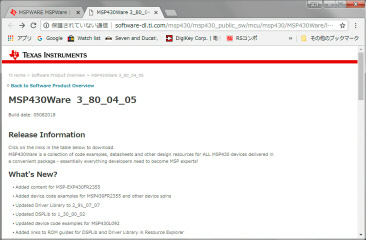

MSP430で動いているDCO用ROMエミュレータにUSB−CDCを追加するために、サンプルコードの”C3_EchoToHost”をビルドしましたが、ガレージのPC環境では、なぜかCDCドライバがインストールできませんでした。ドライバのインストール時にinfファイルのディレクトリを指定しても、”ドライバがみつかりません”となります。MSP430Wareのバージョンは3.6でした。アパートのPCにROMエミュレータを接続すと正常にインストールできます。MSP430Wareのバージョンは3.8でした。次回、ガレージのPCもアップデートしてみます。

8月11日

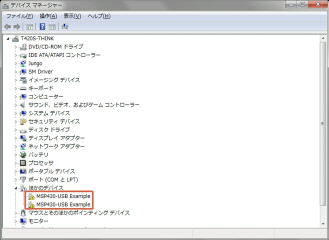

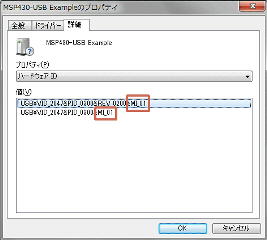

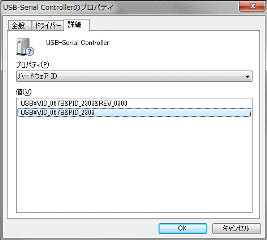

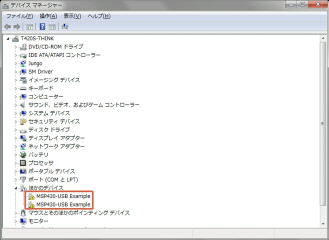

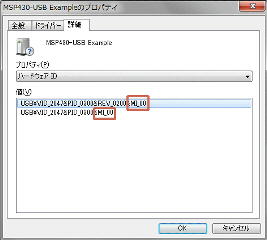

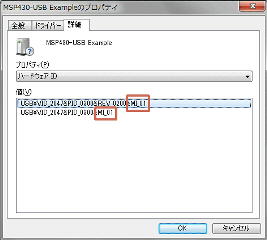

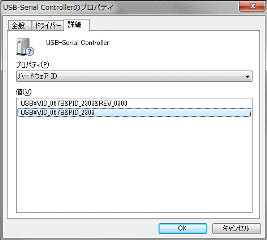

MSP430Wareのバージョンによらず、ガレージのノートPC(Win7 64ビット)ではCDCドライバが正常にインストールできませんでした。アパートのノートPC(Win7 64ビット)をガレージに持ってきて、色々と試してみましたが、結局原因が分からずドライバはインストールできませんでした。アパートのPCではMSP430ボードを接続すると、以下のように1つデバイスが出現してその後、infファイルを指定して正常にドライバがインストールされます。

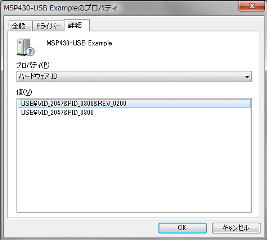

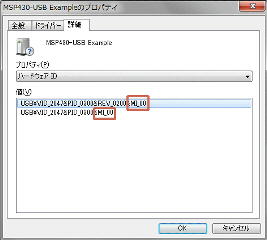

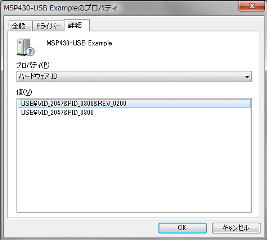

ガレージのPCではデバイスを接続すると、なぜか2つ出現して〜

この時、ハードウェアIDを確認するとMI_00、MI_01の連番になっています。その後、infファイルの場所を指定してもドライバが見つかりませんで終了します。これはinfファイルの中に連番のハードウェアIDが記述されていからと思われます。元々、CDCは制御とデータの2つの通信路があるので、この辺をWindowsがとり間違えているのか?一連の不具合をまとめると、ドライバ本体usbser.sysはバイナリ比較で同一です。ガレージのPCでビルド、転送したMSP430をアパートのPCに接続すると正常(この時、ガレージのPCからコピーしたinfファイルを使用)。これをガレージのPCに接続するとドライバがインストールできないという症状です。

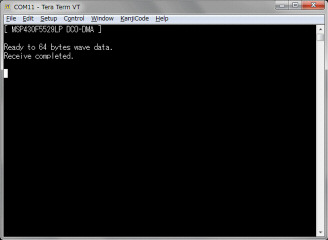

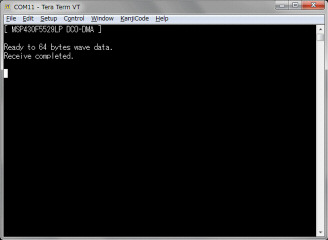

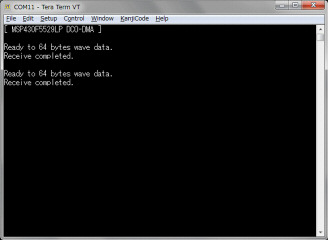

アパートのPCでは正常にCDCドライバがインストールできるので、サンプルプログラムのC2_ReceiveDataにDCO用ROMエミュレータのプログラムを結合して、USB−CDCから新しい波形のロードとROM領域の128個の波形の選択ができるようにしました。

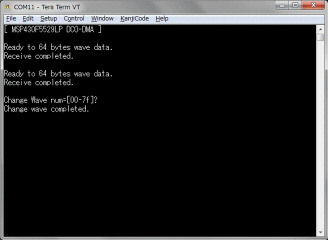

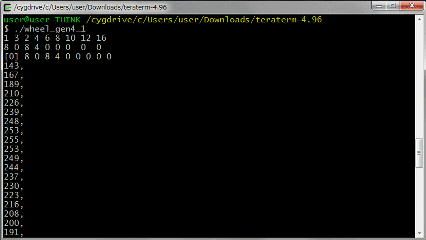

コマンドはロードが’l’でteratermのバイナリファイル転送機能を使ってPCから64バイトの波形をRAM領域に転送します。コマンドはエコーバックはせず、コマンド種別をPC側に送ります。

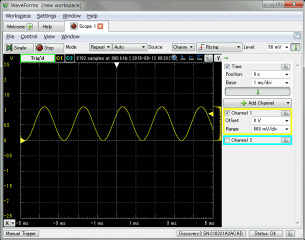

テスト用に作成した周波数1倍の方形波です。

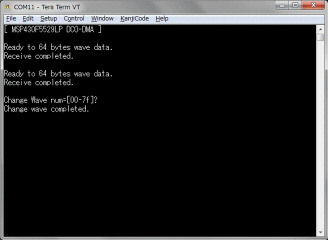

続いて、別の波形をロードしてみます。

こちらもテストで作成した周波数2倍の方形波です。

波形変更コマンドは’c’で、0〜127番の波形番号を2桁16進で指定し、ROM領域の波形をRAMに転送します。

00を入力すれば、0番のSIN波が出力されます。

トーンホイールオルガンの波形生成プログラムはドローバのレベル1セット入力すると、1波形分のバイナリファイルを出力するように修正しました。

上記で生成したトーンホイールの波形ファイルはロードコマンドで転送できます。最終的には使える波形を64個集めて、再度、8チャンネルのDCOの波形をROM化します。

8月12日

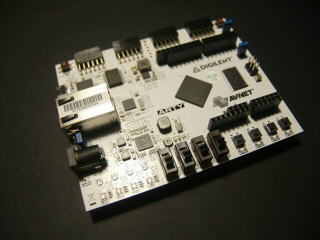

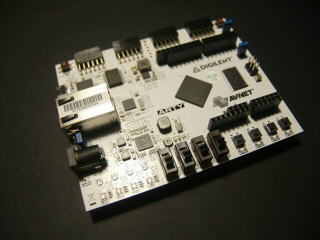

マルツから、再度ARTYボードを購入しました。

SPIのDAC評価ボードも購入しました。DACの型番はDAC8568で、本来はMSP430のローンチパッド用ですが、今回はARTYに接続して使います。16ビットの8ch出力です。16ビットのデータを出力するのに32ビットが必要です。仮に48KHzサンプルで8ch同時に出力するには単純計算で48K*8*32=12.288Mb/Secです。実際にはチャンネル間に少し間隔が必要かもしません。クロックの最大周波数は50MHz、セットリングタイムは10uSecなので、音声帯域は出力可能と思われます。

DACボードをARTYボードに両面テープで固定し、ジャンパ線で配線を追加しました。FPGA内にデジタルシンセを実装する実験用です。とりあえず、Pmodコネクタに接続しました。

8月18日

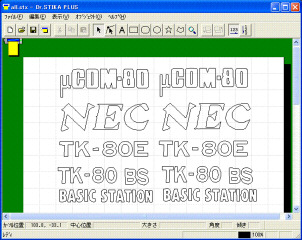

TK80のロゴを使ってグラスにサンドブラストします。古い取説などからロゴをデジカメで撮影します。コントラストを上げてからBMPに変換して、STIKAにインポートして閾値を調整し、シートを切り出します。抜き文字をグラスに貼ります。

アマゾンでFPGAマガジンの17号を購入しました。”DDRメモリを接続して大容量メモリにアクセス!”という記事があり、ARTYに載っている256MBのDDR3の使い方が出ています。

アパートから、USB−CDCの3.3VのUARTケーブルを持ってきました。

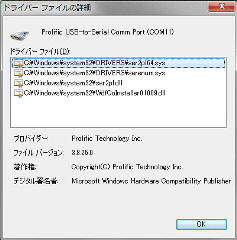

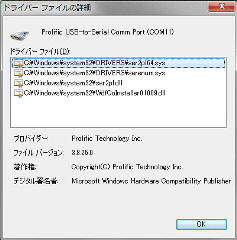

ガレージのPCに接続すると、認識してWindows Updateから自動的にドライバが普通にインストールされました。ただし、ドライバ本体はusbser.sysではありません。

ドライバはメーカ製です。

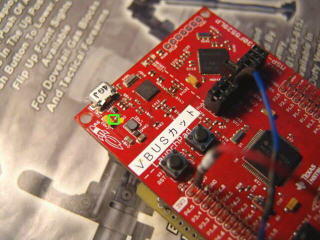

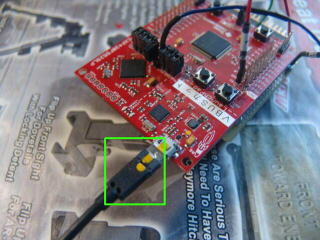

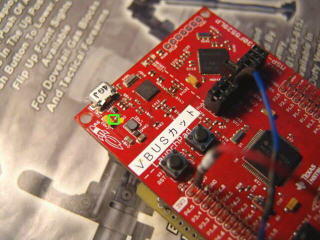

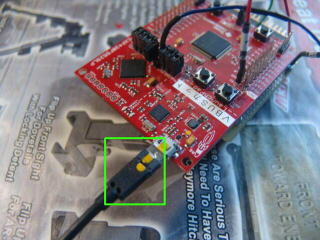

MSP430のROMエミュレータの電源をDCO側から取るように修正します。マイクロUSBから接続されている5VのVBUSをカットし、ROMコネクタの28ピンをジャンパ線でローンチパッドの5Vに接続します。MSP430の3.3V電源もこの5Vから生成します。これで、PCに接続しなくてもROMエミュレータが動作します。

グラスの続きです。ブラストする所以外をガムテープで厳重にマスクします。隙間があると、文字以外がブラストされて失敗するので、良く確認します。

ガレージ裏で、スピードブラスタでサンドブラストします。

砂が当たったところは、すりガラスになります。マスクを剥がすと完成です。

8月19日

ROMエミュレータをDCO1に組み込みます。使用頻度の低いボリュームを1つ外して、USBケーブルが通せるようにします。

マイクロUSB側のコネクタをボリュームの穴に通るように8mm幅まで小さくします。

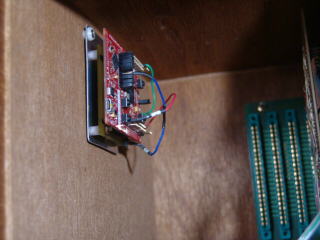

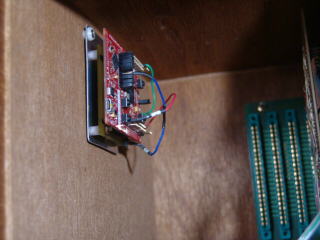

筐体内に固定できるようにアルミ板で固定プレートを作製し、筐体の左側に固定しました。

DCO1とROMエミュレータを接続して、DCO2も筐体に戻します。PCからコマンドを送って動作確認します。動作良好です。

先々週、512倍クロックを追加したDDSのARTYボードを修正します。LEDが点灯すると、凄く明るいのでLEDに接続されている抵抗を取り外し、点灯しなくします。コネクタを追加して、512倍クロックをポリウレタン線で配線しました。

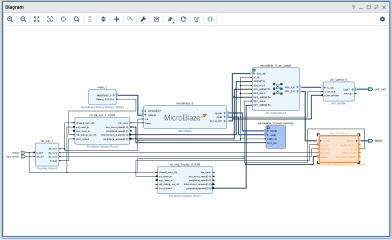

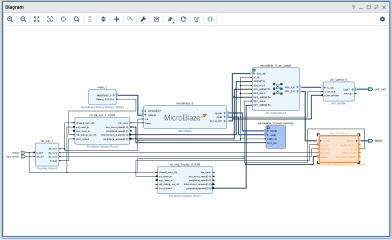

FPGAマガジンを見ながらMicroBlazeにAXI経由でDDR3を接続し、インプリ後、bitファイルの生成まで終了しました。