TK80/BSの

シンセシステムを復活/拡張したい〜

その26

ARTYにSPI−DACを接続してみる

2018年

2018年

8月25日

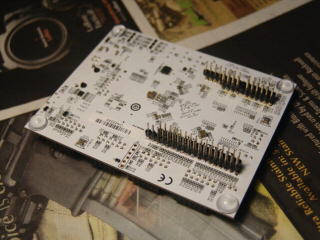

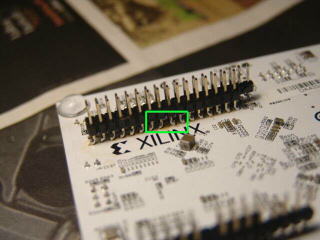

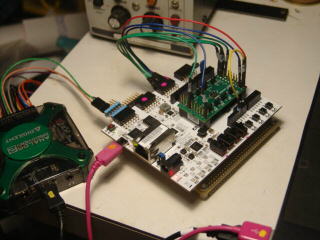

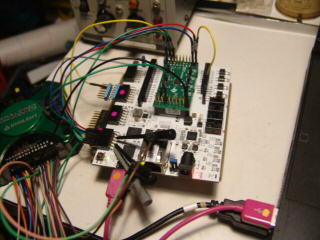

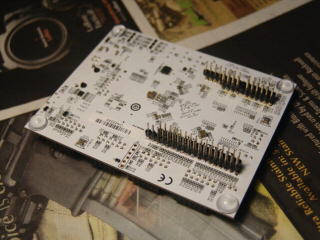

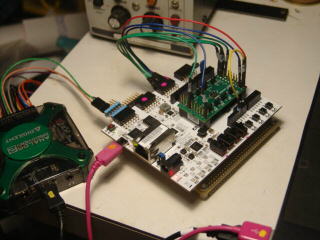

ARTYボードの下に拡張ボードが接続できるように、ピンヘッダをハンダ付けします。下にボードを付けた方がケースの取り付けが簡単になります。コネクタはアルドウィーノ互換なので、ハーフピッチの部分がありますが、うまく位置をコネクタの位置を調整すると、ピンを曲げなくてもハンダ付けできます。

下ボードにはコネクタと四隅に取り付け用の固定穴を開けます。ユニバーサルボードは端材なので中央に穴が開いています(笑)。

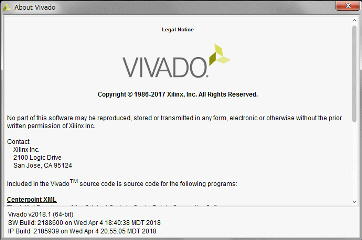

ガレージとアパートのPCを入れ替えたので、現在のガレージのPCのVivadoのバージョンが1つ低い2018.1になっています。

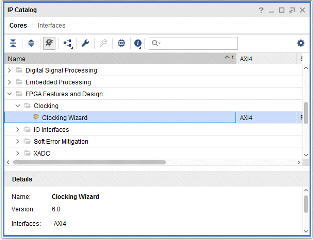

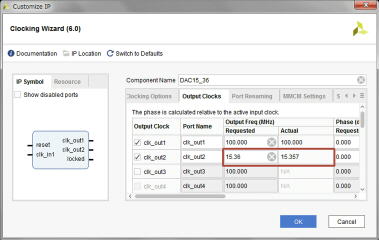

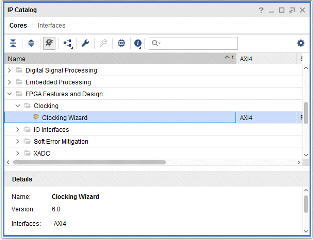

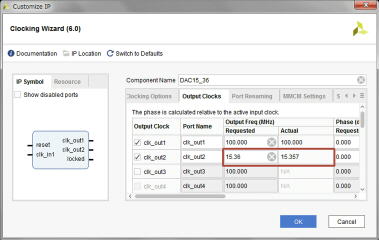

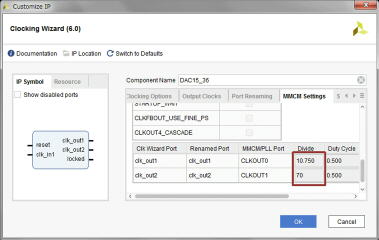

MicroBlazeの入っていない素のDDSの論理にDAC用のMMCM(PLL)を実装します。周波数は実装するデジタルフィルタのサンプリング周波数の48KHzの320倍の15.36MHzにします。VivadoのIPからClockingWizardを選びます。

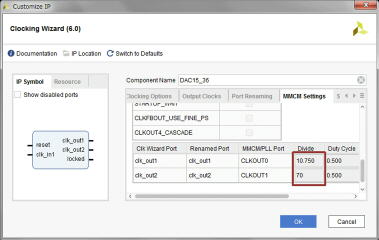

クロックを15.36MHzに設定すると、15.357MHzになり、各分周器の分周値が自動的に計算され、PLL用の逓倍用の分周が10.75で、VCOの出力分周が70です。Fout=100*10.75/70=15.35714MHzです。このときのVCOの出力周波数は1.075GHzになります。ブロックダイアグラムの無い素の論理にIPを組み込む方法はここを参考にしました。これKEK(高エネルギー加速器研究機構)の関連ページみたいです。1〜10まで細かく手順が書いてあるので非常に助かります。

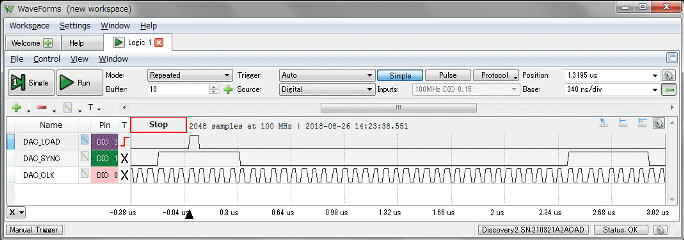

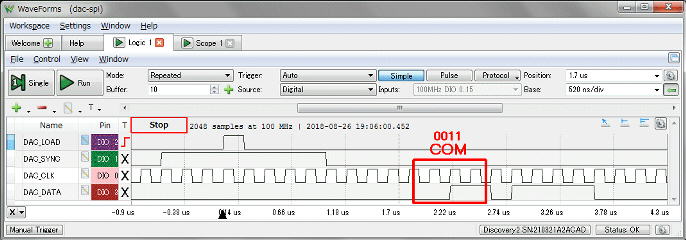

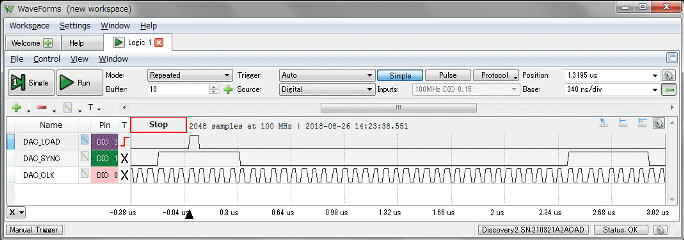

上記の15.36MHzから生成するDAC用のタイミングを確認します。現在接続されているDACボードとは別のPmodコネクタにアサインし、アナログディスカバリで確認します。

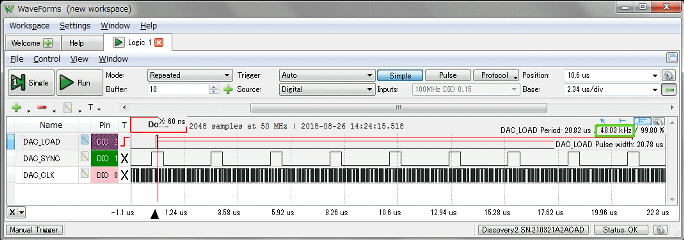

上から、内部信号のLOAD(内部320ビットのシフトレジスタのロード信号)、DACに接続するSYNCとCLKです。DACのレジスタは32ビットですが、SYNC信号がHIGHの休止時間を前後それぞれ4ビットとって、1chあたり40ビットとします。40*8=320ビットで一巡します。

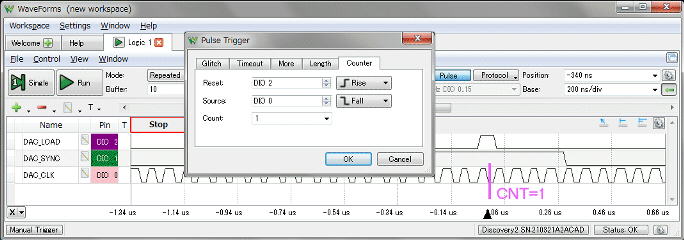

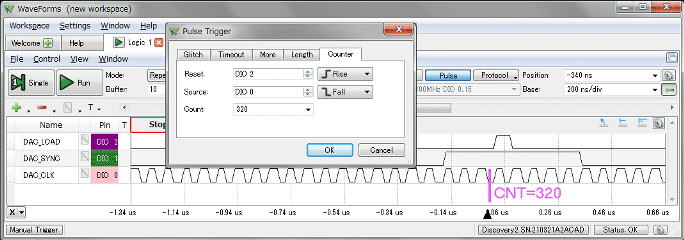

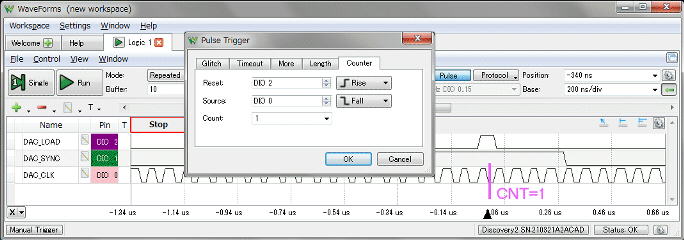

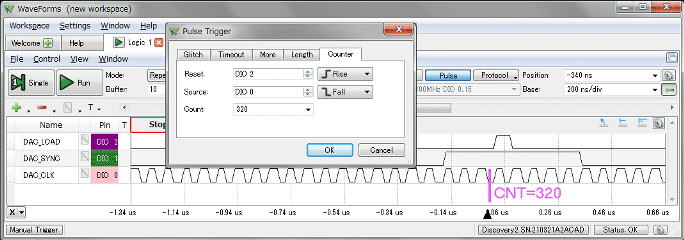

アナログディスカバリにはカウント値でのトリガをかける機能があり、これを使って320カウントが正しく動作しているか確認できます。SYNCの立ち上がりでリセットして、CLKの立下りでカウントします。下はカウント1の時です。

トリガカウントを320に設定して、カウント1の時の1つ手前に来ていることを確認しました。0〜319でカウントしてます。正しいです。LOAD信号は320カウンタが最後の319の時に1クロックだけ発生します。

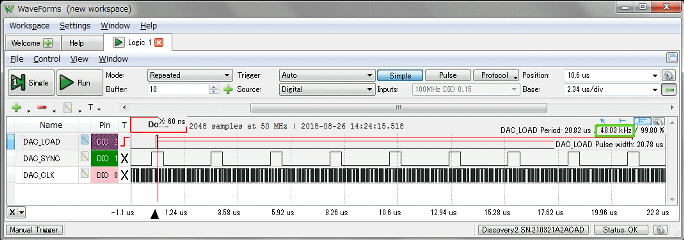

全体の波形です。LOAD信号の間隔を測定します。周波数は48KHzになっています。SYNCが8回出て320ビットで一巡しています。正しく動作しているようです。

8月26日

タイミングは良さそうなので、下位のモジュールに40ビットのDACのデータ用のシフトレジスタを実装します。動作はLOADでデータをレジスタに書き込み、その他の時はシフトするだけです。

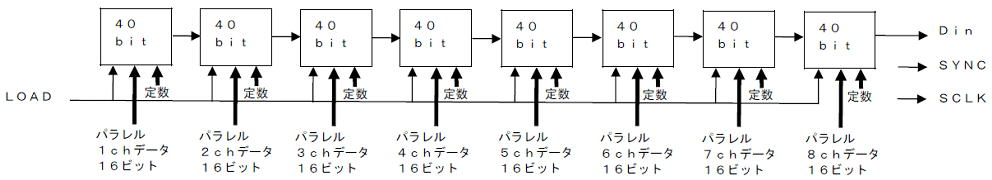

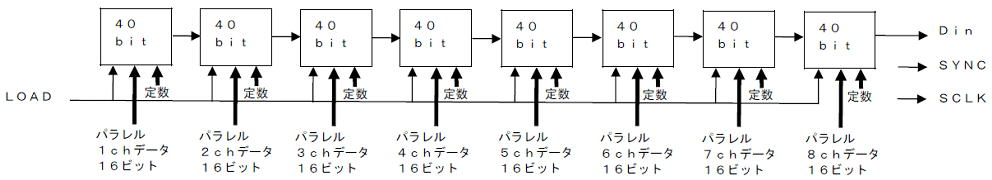

上位のモジュールで下位の40ビットシフトレジスタを8個直列に接続します。1〜8chの順で接続し、最後の8chの出力をDACのDinに接続します。内部の48KHzのLOAD信号でロードされた前段(DCOやデジタルラダーフィルタを想定、最終的にはDCA)のパラレル16ビットの波形データを8個直列にシリアルに変換してDACに送ります。

320ビットのシフトレジスタのブロック図は以下のようになっています。SCLKは15.36MHzのクロックです。定数部は前後のSYNC休止期間、コマンドやアドレスを含み合計で24ビットです。

Pmodを繋ぎ変えてDACボードに接続します。データはダミーで8chは0x8000、1chは0x1000です。正常であれば8chのLEDは点灯するはずです。テスタで測っても0Vでした。

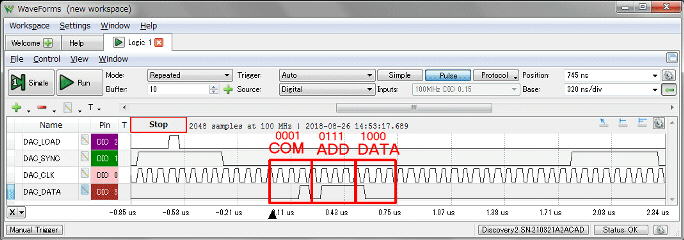

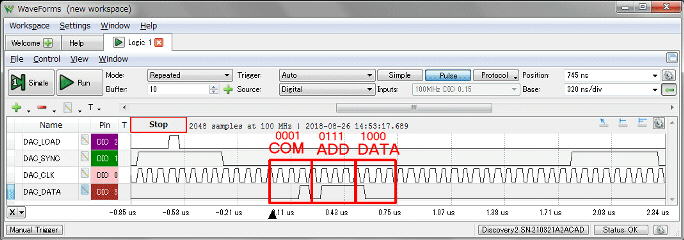

DACに送っているデータを確認してみます。先頭の8chです。コマンドは0001、アドレスは0111、データの先頭は1000です。

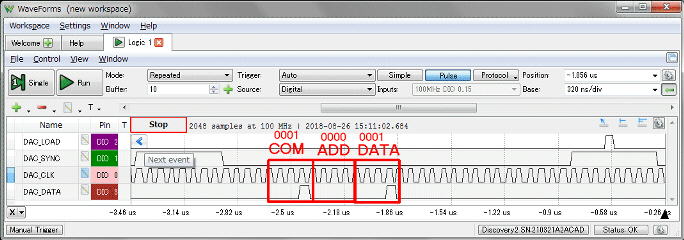

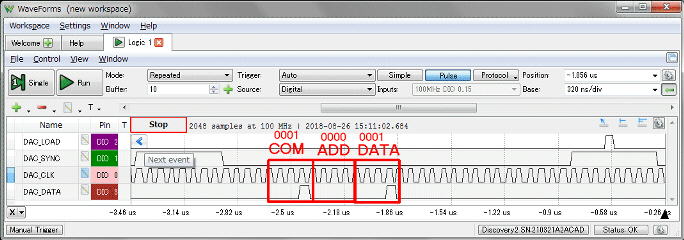

続いて、最後の1chです。コマンドは0001、アドレスは0000、データの先頭は0001で合っています。アナログディスカバリは非常に便利なのですが、サンプリング周波数が100MHzなので、ここで測定している15MHzくらいがきれいに測定できる上限周波数です。波形が台形になってくるのは良くできてます(笑)。

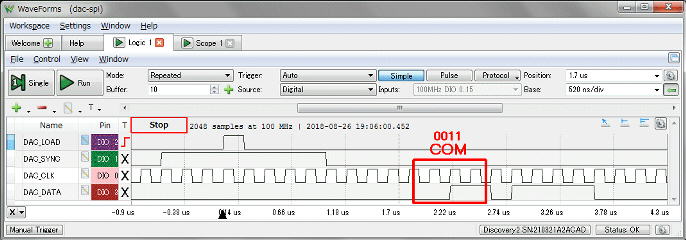

データシートを確認すると、コマンドは0001(レジスタライト)ではなく、0011(アップデート)でした。コマンドを0011に修正しました。クロックをアナログディスカバリでもきっちり取れる5MHzに変更してみました。各出力は0Vのままで正常動作していません。次回、再度動作確認します。

8月27日

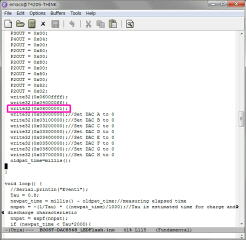

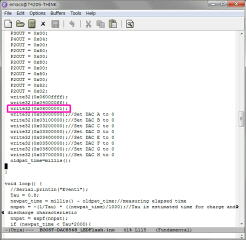

DACボードは元々MSP430LP用なのでサンプルプログラムがあります。アルドウィーノ互換の環境用ですが、ダウンロードして、コードを確認しました。データをクリアする前に幾つかコマンドをDACに送っています。0x08000001はデータシートで確認すると内部リファレンスをイネーブルにするコマンドでした。データシートを読むと、デフォルトで内部リファレンスがディゼーブルになってました。出力が出ない原因が分かりました。論理で初期化コマンドを送るのは面倒なので、外部リファレンス端子にリファレンス電圧を供給するのが早そうです。

8月29日

アパートに一式を持って来ていたので、アナログディスカバリの電源機能で2.5Vを生成し、外部リファレンスに接続して確認したところ、出力レベルに応じてLEDの点灯を確認しました。8ch〜1chに0x8000〜0x1000を出力ているので、8〜3chは点灯、1と2chが消灯です。