TK80/BSの

シンセシステムを復活/拡張したい〜

その30

IPの再構成とディレイドLFOの実験

パラメータ入力用MSP430

デジタルシンセの2ch化

2018年

2018年

10月13日

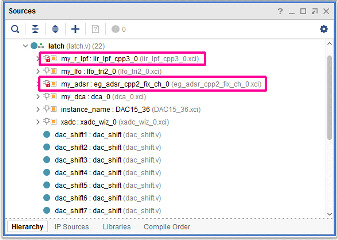

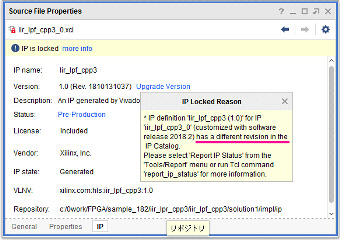

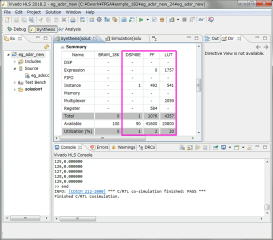

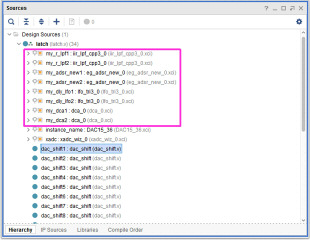

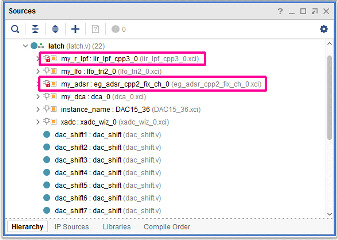

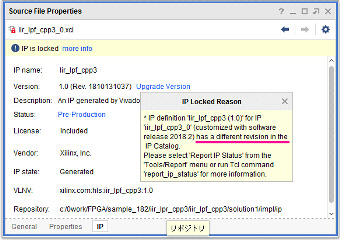

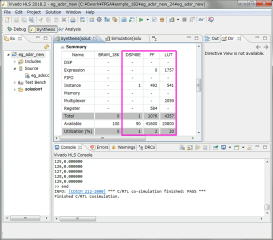

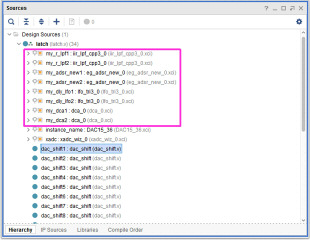

ガレージとアパートの双方でFPGAを作成していると、どちらのPCで作成したのが最新のIPか、本体なのか、分からなくなってきます。以下はIPががロックされているという表示です。この状態でもIPの変更はできませんが、合成してビットファイルを生成することはできます。

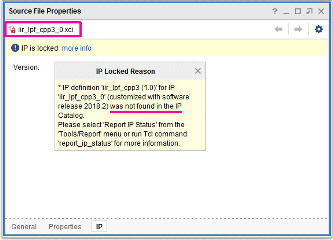

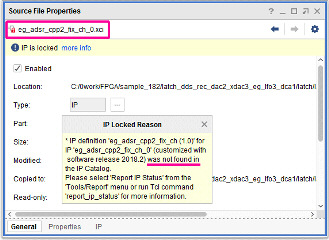

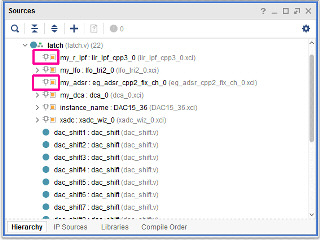

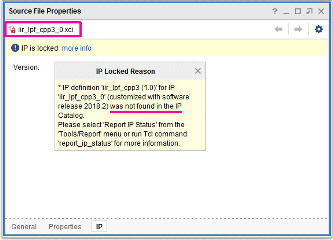

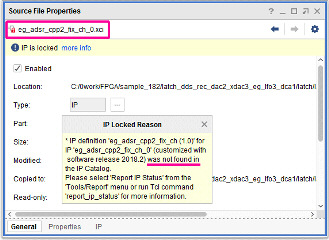

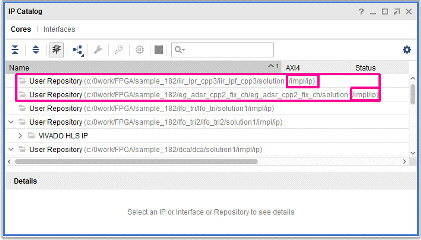

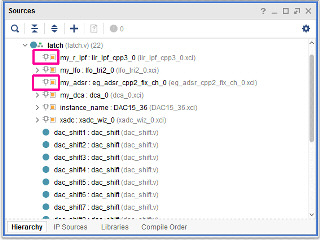

詳しくみると、IPカタログに所定のIPが無いということのようです。左はラダーフィルタで右がエンベロープジェレータです。

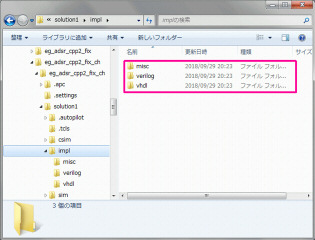

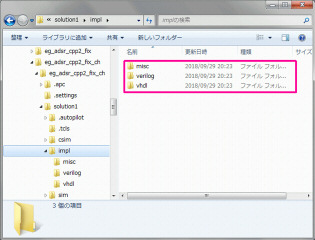

IPのロケーションを確認します。

実際にディレクトリを確認するとIPが入っているはずのディレクトリが無いです。本来はIPディレクトリの下にIPのファイルが必要です。原因はVivadoの本体プロジェクトファイルのみをコピーして、HLSで作成したIPのRTLエクスポートファイルが無いためです。

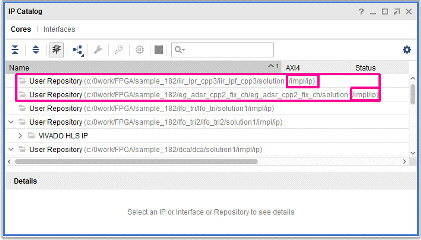

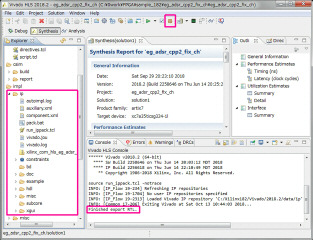

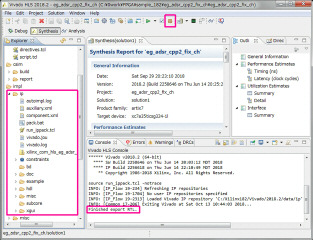

HLSのプロジェクトはUSBメモリにバックアップがあるので、再度HLSで合成して、RTLをエクスポートをします。

再度、Vivodoで確認すると、今度はメッセージが変わって、レビジョンが違っているというメッセージになりました。

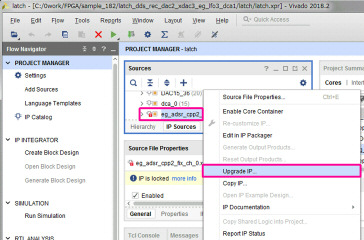

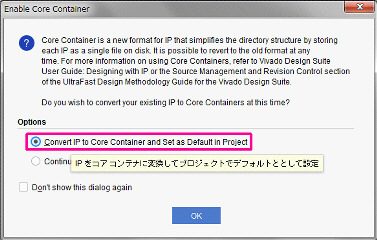

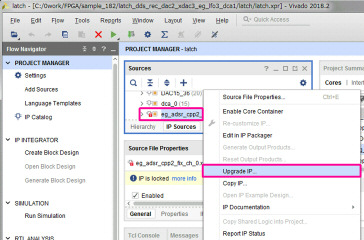

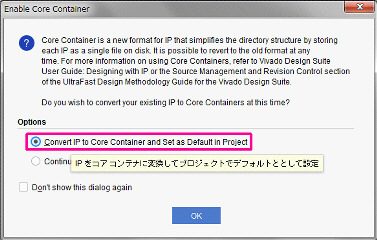

IPソースのウインドで、右クリックでメニュー表示して、IPをアップグレードを選びます。上の変換の方を選びます。

ロックの表示が消えました。

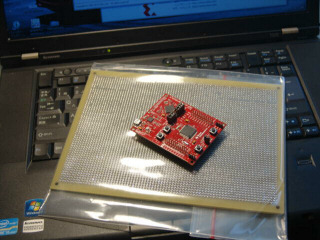

パラメータ設定用のMSP430ローンチパッドとユニバーサル基板、ICソケットを秋月で購入しました。

こちらはAitendoのLCDとフレキ変換基板、SPI−ADC用のQFNピッチ変換ボードです。ADCはAD7699を使用する予定です。

10月14日

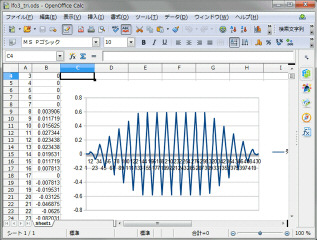

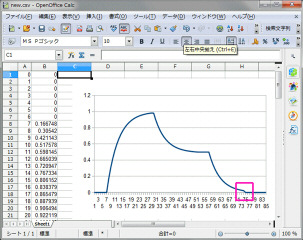

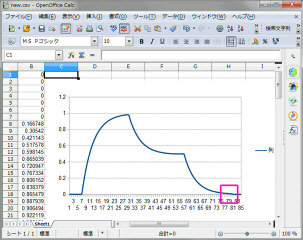

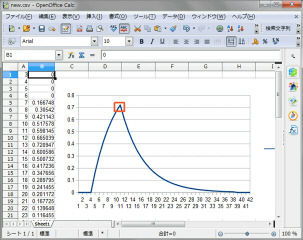

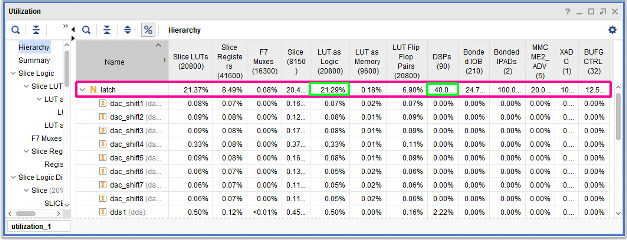

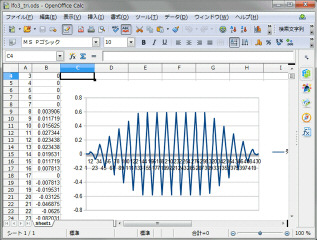

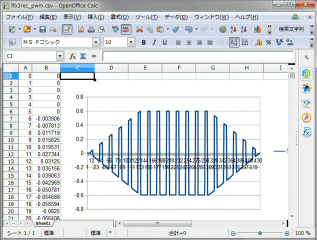

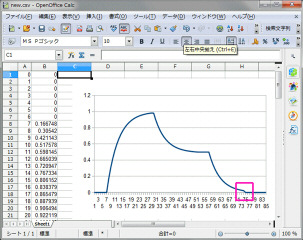

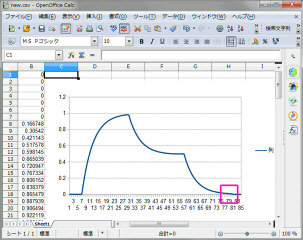

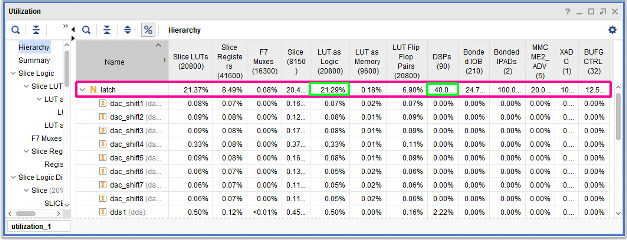

LFOをディレイド・モジュレーションに修正します。簡単のため、コンデンサの充放電波形ではなく、直線でARを作ります。下はテストベンチの擬似ゲートで確認したシミュレーション波形です。ゲートの立ち上がりで三角波のレベルを0にクリアしてシンクロさせ、アタックに続き、ゲートONの定常、ゲートOFFのリリースです。

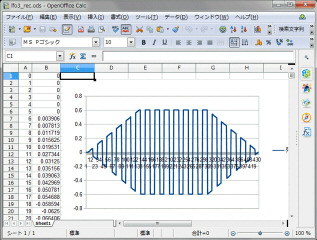

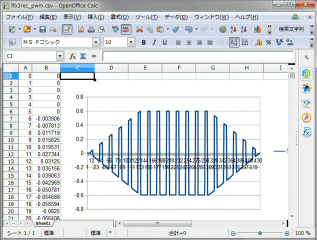

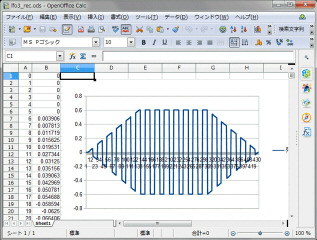

波形を矩形波に変更したシミュレーション、右はPWMでパルス幅を短くした状態です。

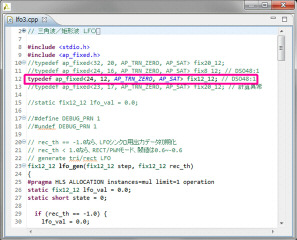

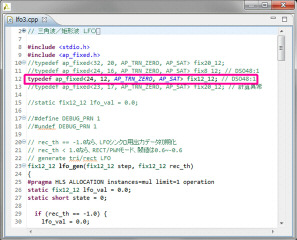

リソースを圧縮するために、ディレイド・モジュレーションLFOの内部処理はfix12_12にします。

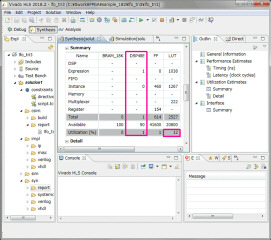

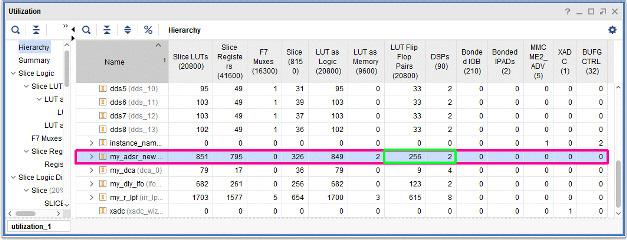

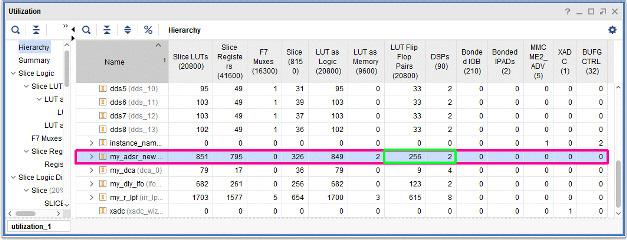

DSP48は1個ですが、LUTの使用数が多いです。右は単純な三角波のLFOのリソースです。ちなみに、内部処理をfix20_12で行うとDSP48の使用量は3個になります。

10月14日

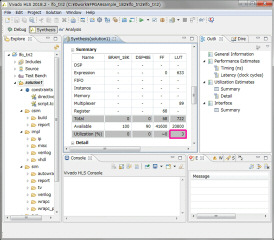

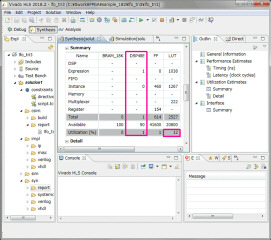

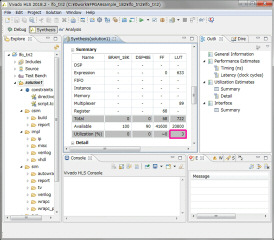

Vivadoで合成後にディレイド・モジュレーションLFOのリソースを確認します。LUTは上に比べて3分の1以下になって772に、DSP48は1つ増えて2個になりました。HLSの使用量はあくまでも見積もりのようです。

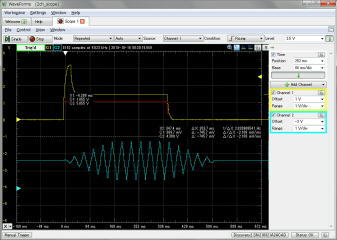

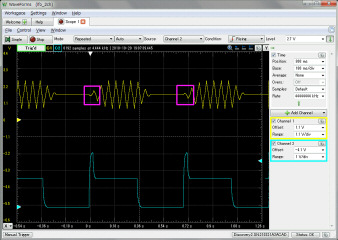

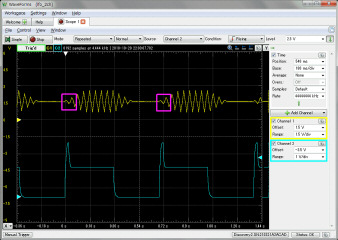

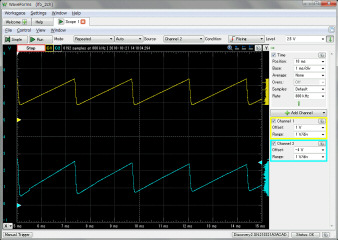

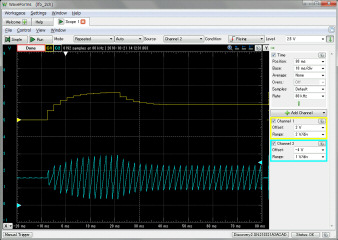

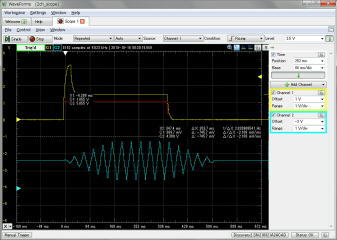

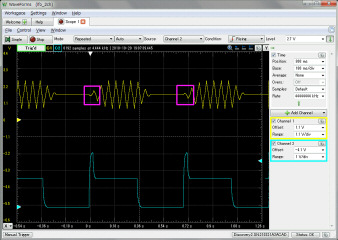

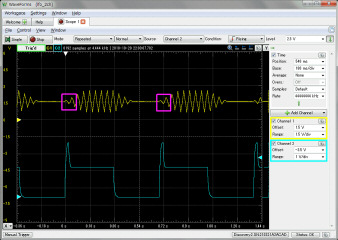

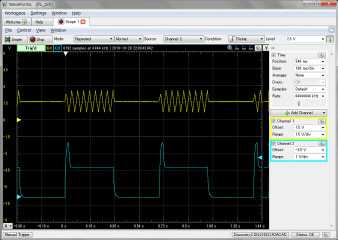

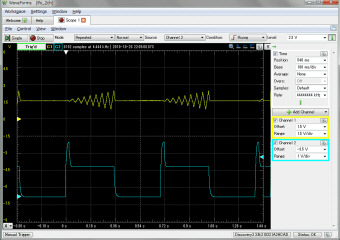

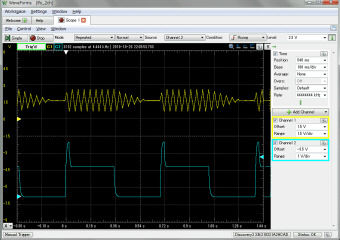

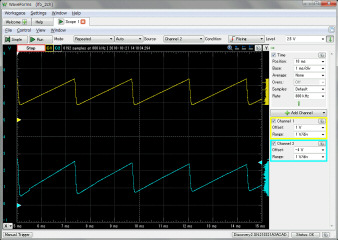

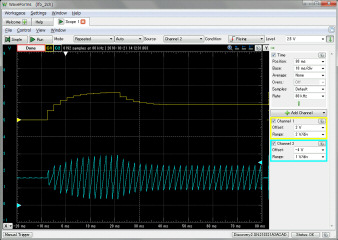

LFOをデバッグ用にSPI−DACへ出力して確認します。タイミング確認のためにエンベロープジェネレータと合わせてアナログディスカバリに取り込みました。正常動作しています。

10月18日

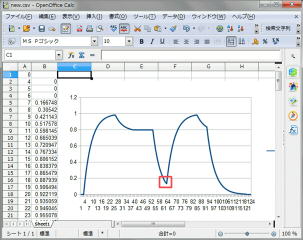

エンベロープジェネレータのコードを修正しました。リリースの終了値が少し大きくて段が目立つので0.02を0.005に変更しました。

続いて、アタック中にゲートOFFになったときにリリースに移行するように修正します。

同じく、ディケイ中にゲートOFFになったときもリリースに移行します。

続いて、リリース中にゲートONになったときはアタックに移行します。いずれも、HLSのCシミュレーション結果から波形を作成しました。

リソース圧縮のため、引数と内部処理をfix12_12に変更しました。DSP48は1個になりました。見積もり上はLUTの使用量が多いです。今週末に合成/インプリして再確認します。

10月21日

合成後のリソースを確認します。LUTは256個に減って、DSP48は2個に増えています。

DDSとデータ入力のラッチは8ch分、その他シンセ部が1chの現状のリソースです。

モノタロウで購入のタカチのCFシリーズ傾斜アルミケースとアマゾンのツマミです。FPGAデジタルシンセのパラメータ設定用です。ケースは正面パネルは単体になるので加工しやすいです。側面はプラスチックです。

ケースのサイズは約A5サイズのユニバーサル基板に合わせました。

ケースの正面パネルは片側だけ黒に塗装されています。パネルに部品を配置してみました。6個のロータリエンコーダのパラメータ表示の7セグLEDは手持ちの部品が数種類あり、全体の配置から部品を決定します。肝心のロータリエンコーダがまだ来ていません。

LFOのゲートシンク機能の不具合です。プラス側から始まる時とマイナス側から始まる時がありました。コードを修正して、必ずプラス側から始まるようにしました。

10月21日

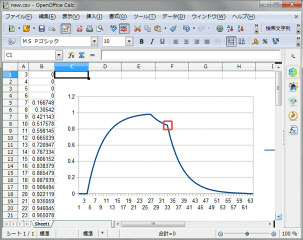

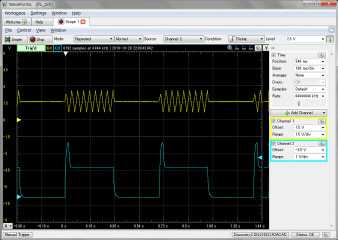

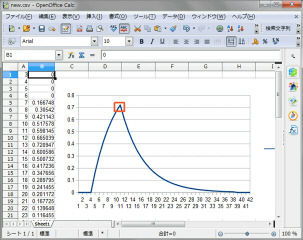

LFOの続きです。ディレイ機能のパラメータをボード上のXADCに接続されているボリュームから調整できるようにしました。下はアタック、リリースとも最短の時です。

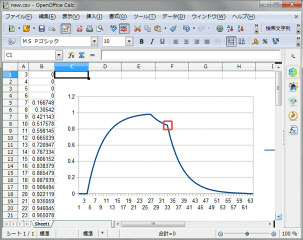

それぞれ、アタックとリリースの時間を延ばした時です。

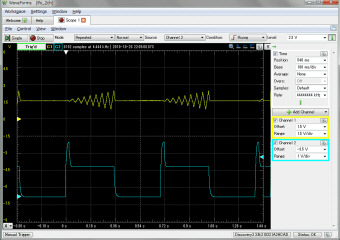

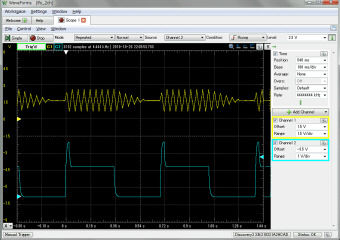

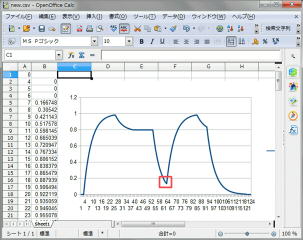

だいぶ前にるDDSトーンジェネレータに追加した512倍クロックと同じロジックを使ってノコギリ波を生成させます。DDSから512倍のロックを出力させ、新規に波形変換ロジックを追加します。512倍クロックでバイナリカウンタを動作させると、出力はレベルが10ビット、周波数が1倍のノコギリ波になります。下はラダーフィルタとDCAから出力です。また、波形変換ロジックからは1倍の方形波を出力します。切り替えはボード上のスライドスイッチで行います。

ラダーフィルタはスルーして、エンベロープジェネレータで変調したDCAの出力です。現状はボード上のスライドスイッチで方形波、ノコギリ波を選択します。次回、ミキシングできるように修正します。

10月29日

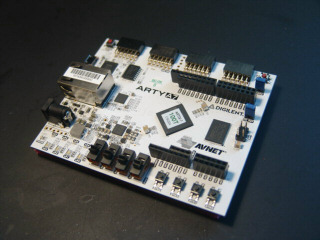

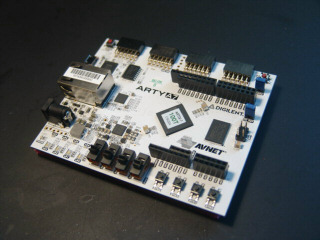

この週末は日曜のみの作業です。マルツ経由のDIGIKEYからのArtix−7の100Tの載ったARTYボードが来ました。A7バージョンになって電源周りが変更になっています。USBのVBUSと外部のDCジャックの電源の切り替えショートピンが無くなり、自動になりました。価格は3万円弱ですが、35Tボードに付属していたVivadoのライセンスは付いてません。WEB版で足りているのでライセンスの有無はあまり関係ありません。

同じく、外部から波形をアナログ入力するSPI−ADCのAD7699です。16ビットの8ch入りです。残念ながら、安い評価ボードが無く、AitendoのQFN変換基板に実装して使用します。サイズが4x4mmと小さいので、失くさないようにテープで変換基板に固定しておきます。後でハンダ付けしますが、実体顕微鏡下で行う必要があります。

こちらはマルツ在庫のコパルの非接触ロータリエンコーダです。50パルス/回転、スイッチ付きです。6個の内5個が固定金具付きですが、在庫が無かったため1個だけ金具無しです。出力のピンヘッダは2.54ピッチではないため、金具が無いと基板を固定できません。少し工夫が必要です。

同じく、ロータリエンコーダのA/B相をクロックとディレクション信号に変換する74HC74と7セグLED点灯用のシリアルパラレル変換の74HC595です。

パネル載せる7セグLEDを決定しました。先週の小さいものは2.54ピッチでないため却下、中くらいの緑色のものはDPセグがないので、これも却下です。大きめの2連の赤に決定しました。また、6個のパラーメータ設定用のツマミは仮に置いてあります。一回り大きいものをアマゾンに発注済みです。

先週の予定では方形波とノコギリ波のミキサーを作るはずでしたが、2ch対応を先に行いました。ラダーフィルタとEG、LFO、DCAを1づつ増やして2chに対応させました。

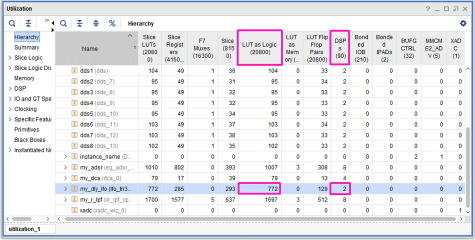

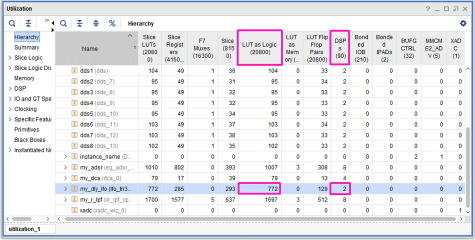

2ch組み込み後のリソースを確認しておきます。DSP48は56個使っています。DDS用に2個使用して、8ch実装済みです。現状のロジックでは1chあたりDSP48を22個使っている計算です。現状のままなら、ぎりぎり4ch分が入ります。新しく購入した100TボードはDSP48が240個入っているので、もう少し機能を追加しても8ch分入ると思われます。

2chに対応させるため、DCOのチューニング用に2つボリュームを追加しました。PCからMSP430のUSB−MIDIパラレル変換を介してテスト録音しました。2chともノコギリ波で少しレゾナンスを掛けています。MP3はこれです。