TK80/BSの

シンセシステムを復活/拡張したい〜

その31

デジタルシンセのEGの不具合対策

DCOのビブラート追加

パラメータ設定器作成開始、SPI−ADCの追加

2018年

2018年

11月3日

アマゾンで購入したロータリエンコーダ用アルミ製ツマミは6個購入したのですが、4個しか送られてきませんでした。連絡して追加で送ってもらうようにしました。

エ

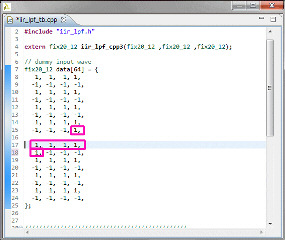

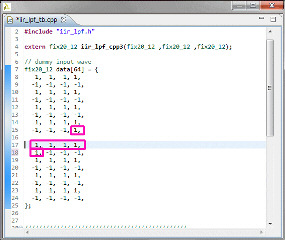

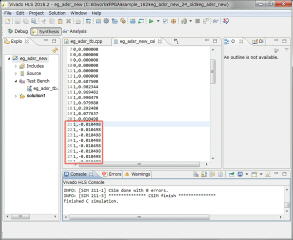

ンベロープジェネレータの不具合です。アタック、リリース時間が、ゲート動作よりも長い時に、1つおきに直ぐ

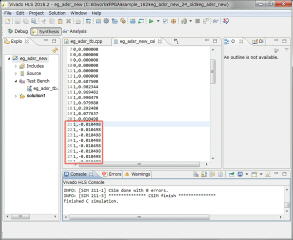

に0になってしまいます。本来は滑らかに、つながらないといけません。HLSのCシミュレーションでも同じ結果になりました。

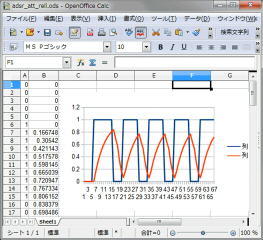

プログラムを修正し、Cシミュレーションを行います。滑らかにつながるようになりました。

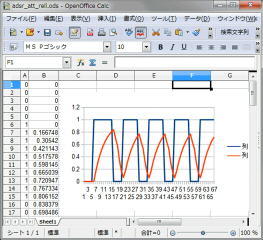

別の不具合です。アタック、ディケイとも短い時にサスティーンが0だと、逆にレベルが最大になります。本来は太赤線のように0のはずです。

HLSのCシミュレーションを行うと、同じ条件で0に近いマイナスの値になっています。これが上位モジュールの演算でプラス側に反転していることが分かりました。Cシミュレーション時のマイナス値を1にして、分かりやすいようにして確認します。対策は値がマイナスなら0を返すようにしました。

11月4日

SPI−ADCを変換基板にハンダ付けします。実体顕微鏡下で行います。QFNパッケージは真上からみても端子が見えないので、変換ボードを斜めにしてハンダ付けします。4x4mmのチップが無事、変換基板に乗りました。

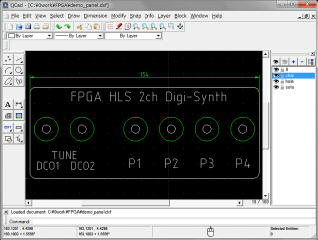

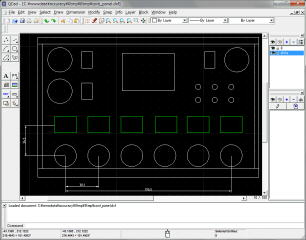

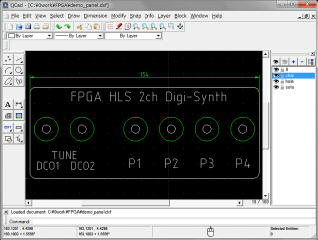

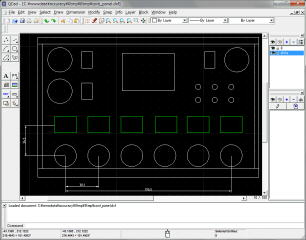

2chになり、DCOのチューニング用のボリュームが2個増えて合計6個に増えたため、アクリル板でボリューム固定用のパネルを作製します。QCADで図面を作成しました。

レーザ加工機で3mmのアクリルを切り出してボリュームを移設しました。

DCOをLFOで変調できるようにしてビブラートに対応させました。また、ボリュームで設定するパラメータの初期化を行い、電源ONで直ぐに音が出せるようにしました。MIDI経由のSP−808と一緒にテスト録音しました。mp3はこれです。

SPI−ADCに電源系のコンデンサを追加しました。

11月10日

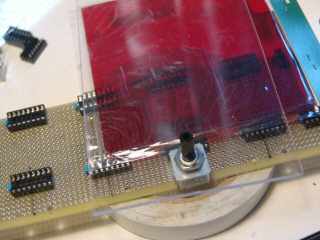

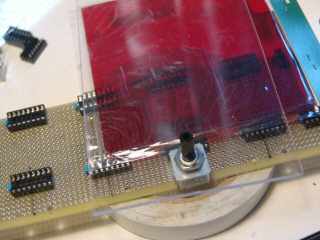

仕事で渋谷に行ったので、ハンズに寄って透明赤のアクリルを購入して持って来ました。厚みは2mmです。近所のホームセンタでは赤は在庫していませんでした。パラメータ設定器のLED用のカバーです。

SPI−ADCのAD7699を接続するためのロジックを追加します。クロックとデータ変換指示のCNV信号、8chのデータがシフトレジスタに揃った時に、データを外にラッチする内部信号を生成します。

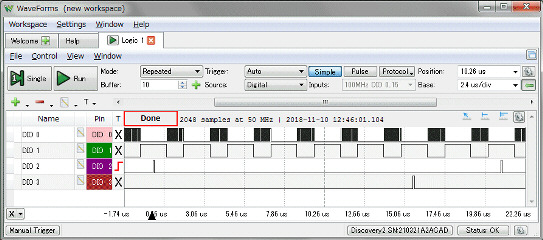

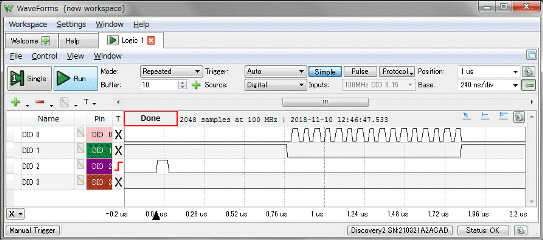

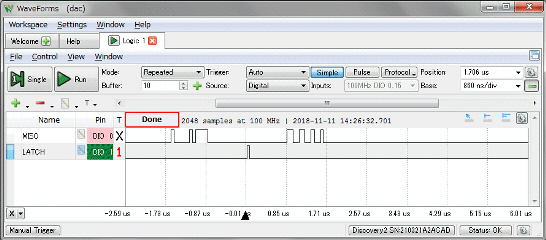

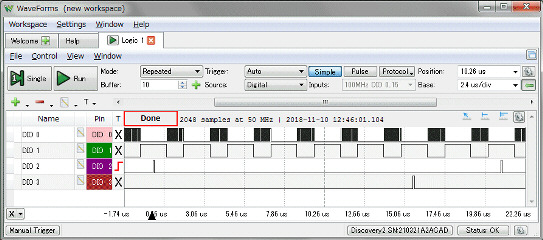

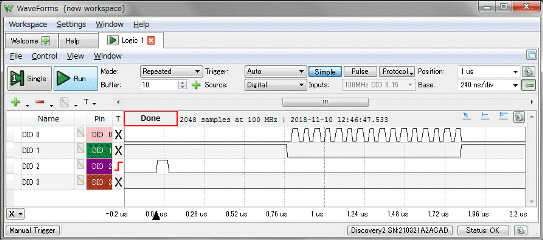

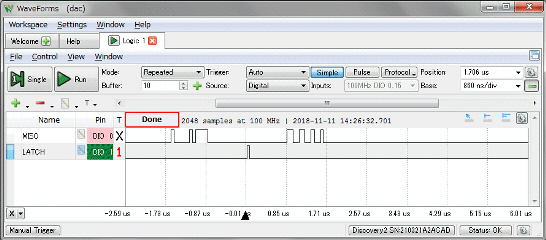

信号の拡大波形です。CNV信号はSPIのSS信号などと同じタイミングです。

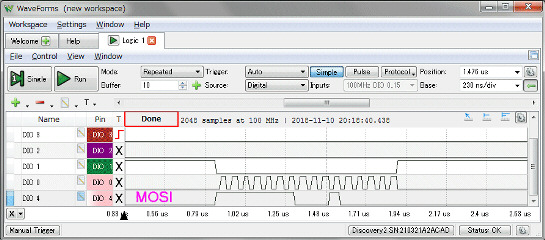

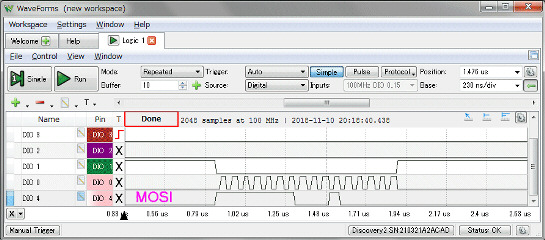

MOSI信号で変換の設定データを出力します。長さは16ビットで、リファレンス電源、チャンネル番号などを含んでいます。設定データと変換結果は2ブロック分ズレているので注意が必要です。

11月11日

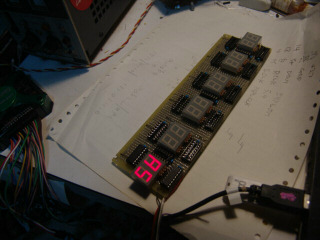

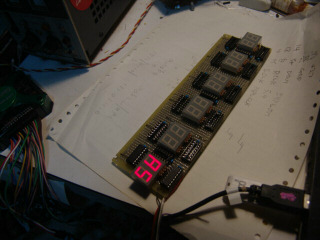

パラメータ設定器の作製を開始します。初めにパネルの部品配置図をQCADで作成します。ロータリエンコーダと7セグLEDはユニバーサル基板に載せるので2.54ピッチで配置します。

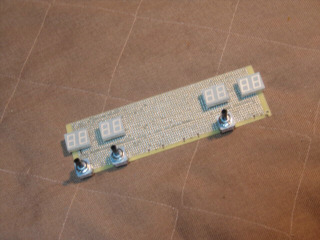

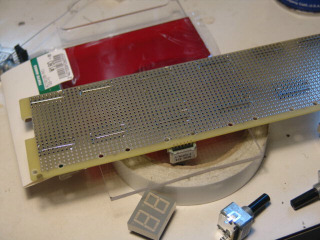

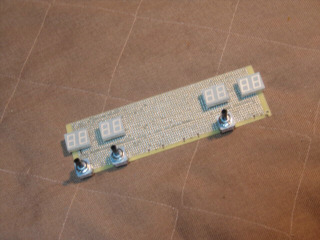

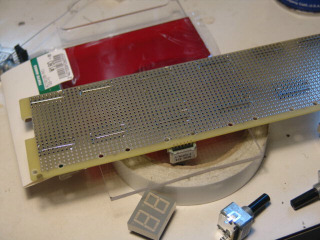

上記の配置図からロータリエンコーダ/LED基板の作製します。大きい基板から切り出し、ロータリエンコーダと7セグLEDを仮載せしてみます。部品の隙間にはLED用のシリアルパラレル変換、ロータリエンコーダのディレクション生成用のD−FFのロジックICが載ります。7セグLEDは2mm厚のアクリルを挟んで、パネルの裏に面一にします。

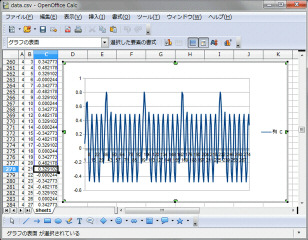

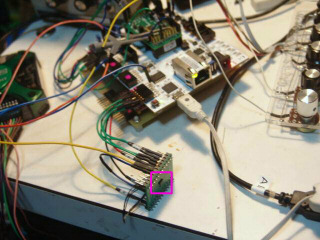

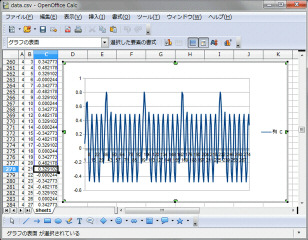

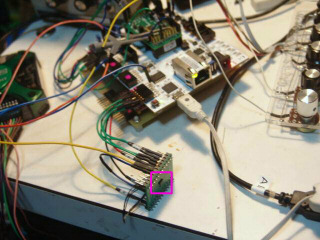

SPI−ADCを接続してロジックの動作確認します。シリアルデータ内のチャンネルが分別しやすいように1と8チャンネル以外はGNDに接続しておきます。

ロジアナでSPI−ADCの変換信号のMISO信号を確認します。1と8の2チャンネル分のみ出力されています。前側が8で後ろが1チャンネルの変換データです。動作しているようです。

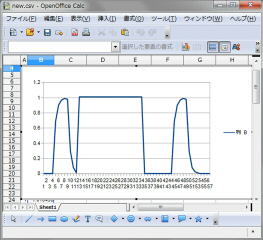

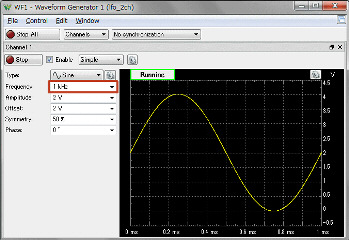

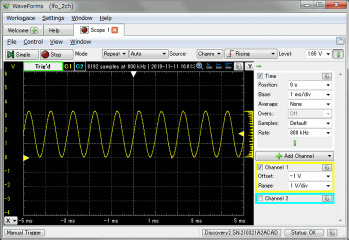

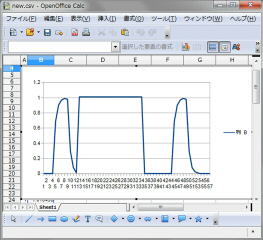

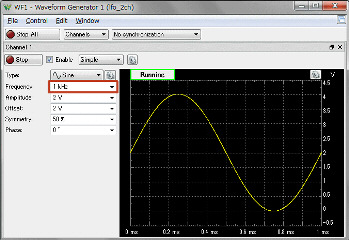

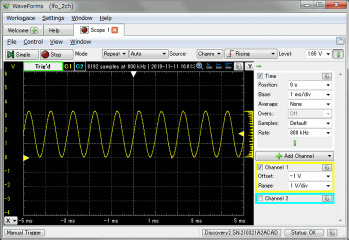

アナログディスカバリの信号発生器で1KHzのサイン波を1チャンネルに入力します。ADCのリファレンスは約4Vなので。2Vを中心に2V振ります。8chのデータがシフトレジスタに揃ったところでラッチし、内部でSPI−DACに接続してループバックします。動作良好です。

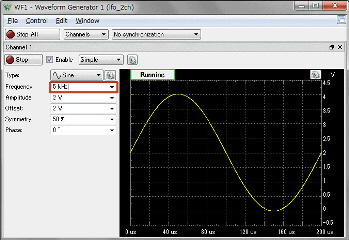

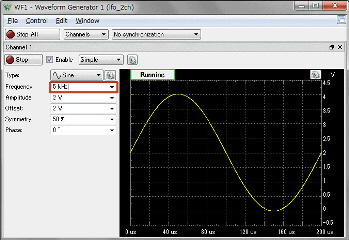

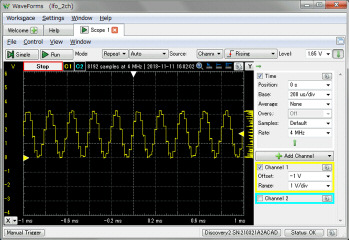

周波数を5KHzにして、再度確認します。サンプリング周波数は48KHzなので、良いようです。

11月17日

不足分のツマミが来ていました。これで6個揃いました。

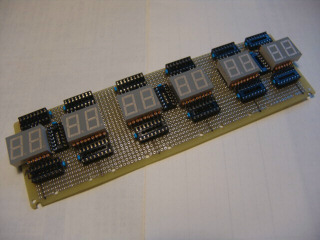

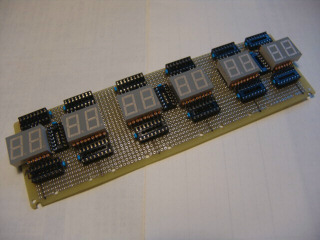

7セグLEDの高さを調整します。基板はロータリエンコーダで保持してパネルに取り付けます。7セグLEDを浮かせてハンダ付けし、2mmのアクリル板を挟んで、パネル裏面に合わせます。

ロータリエンコーダのシャフトを5mm短くしました。

11月18日

パラメータ設定器の7セグLEDの配線を行います。MSP430のGPOでシリアルデータ(クロック、データ、ラッチ信号の3線制御)を出力して12桁の7セグLEDを点灯させます。使用するデバイスは74HC595です。

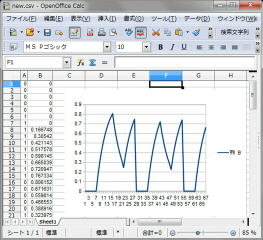

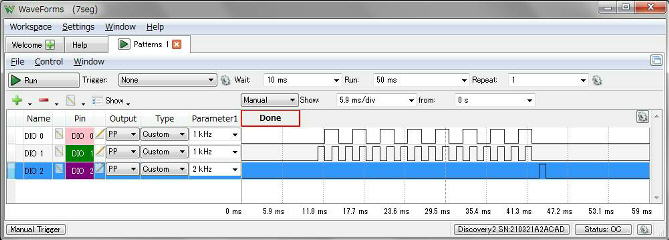

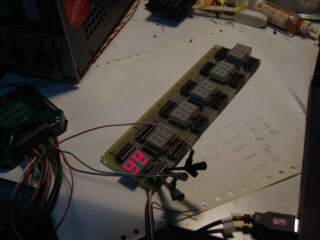

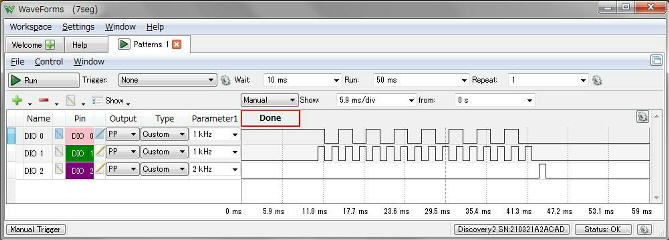

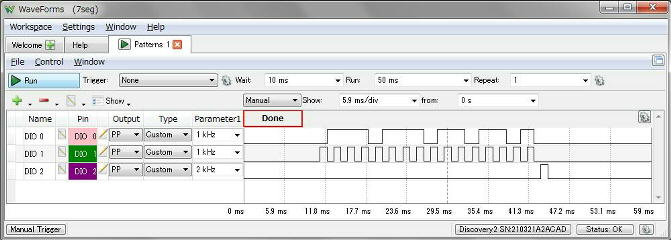

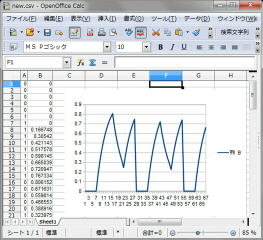

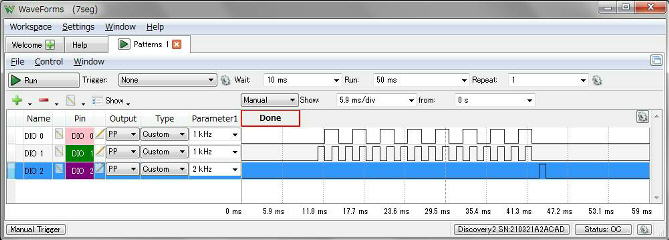

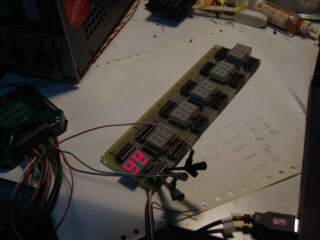

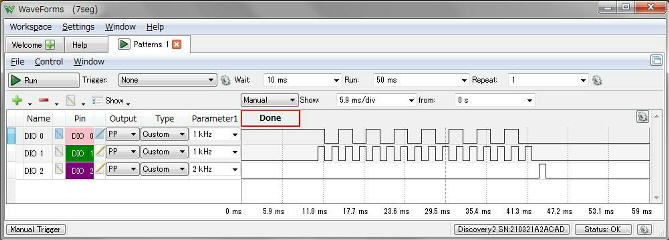

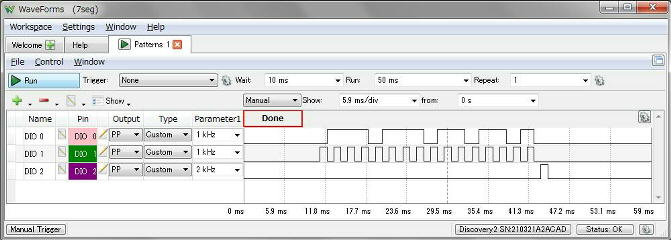

2桁のみ配線が完成したので、アナログディスカバリのパターンジェネレータを使ってテストします。初めにシフトレジスタに送るデータを”55”にしてみます。

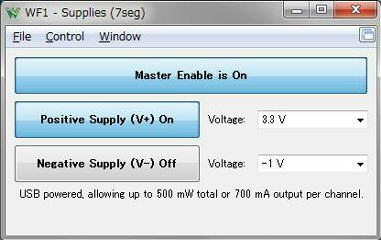

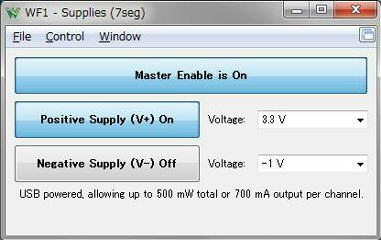

電源もアナログディスカバリを使います。3.3Vに設定します。

シフトレジスタにパターンを送った後にラッチ信号を出力して点灯させます。7セグLEDのセグメント名とHC595のデータビットを合わせてあります。正常動作しているようです。

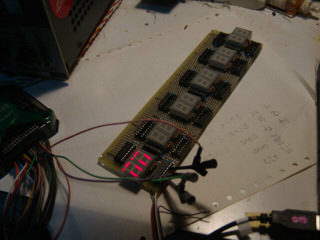

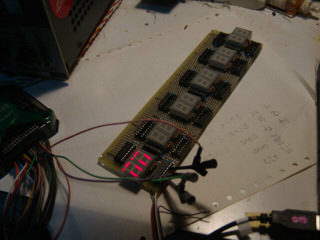

続いて、”AA”を送ってみます。

DPも点灯しています。正常動作しています。

次にセグメントのパターン”A5”を点灯させてみます。手動でデータを入力します。

後ろの2桁は正常動作していることを確認しました。2桁の動作が確認できれば、あとは配線を真似して行えば簡単です。

11月24日

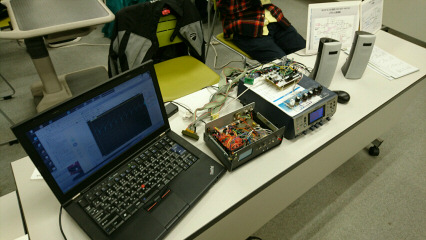

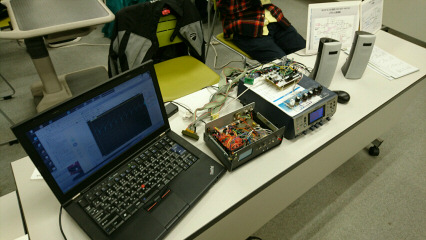

アナログシンセビルダーズサミットに参加してきました。開場前の準備です。

ブースでのデモ風景。MSP430を使ったUSB−MIDIからMC80バスに変換する変換器の出展です。

11月25日

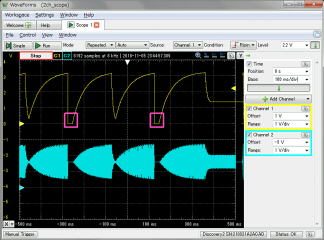

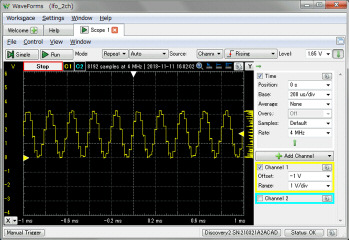

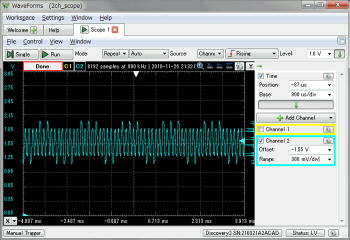

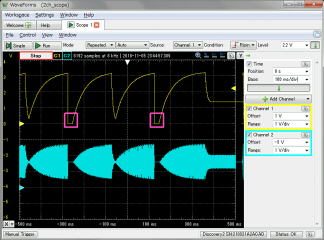

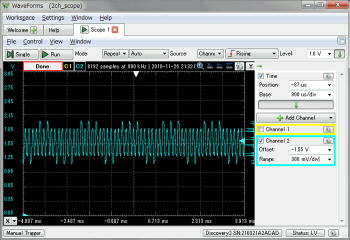

この週末はツーリングとアナログシンセビルダーズサミットが重なったため、ガレージには帰らず、アパートでFPGAデジタルシンセのラダーフィルタに高い音を入力した時の混変調の調査をしました。左の下は低いノコギリ波が混ざっている図です。右は分かやすく拡大したところ、上の黄色はDDS−DCOの方形波を確認用にSPI−DACに出力した波形です。ラダーフィルタの前段でDDS−DCOの出力を48KHzでサンプリングしているためと判明しました。右の上の黄色の波形でも分かるように、入力周波数と48KHzの関係でデューティ比が変わり、ラダーフィルタの出力には低いノコギリ波が加算されています。

方形波で分かりやすい波形を出してみます。

ラダーフィルタのHLSのCシミュレーションで確認してみます。テストベンチの入力波形のデューティ比を少し崩してみます。同じような波形が出ました。ラダーフィルタは15.36MHzで動作しているので、前段でサンプリングする周波数を高くすれば改善されると思います。