TK80/BSの

シンセシステムを復活/拡張したい〜

その32

パラメータ設定器作製、デルタシグマのモニタDAC実装

2018年

2018年

12月2日

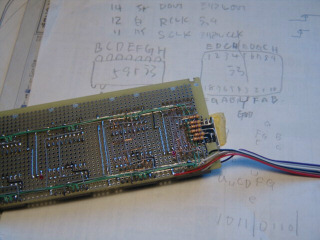

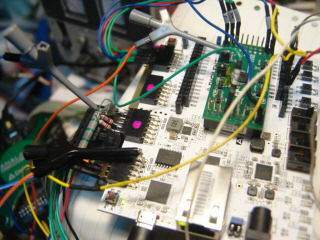

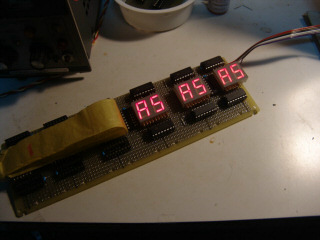

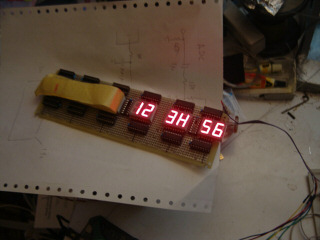

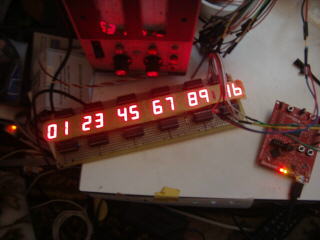

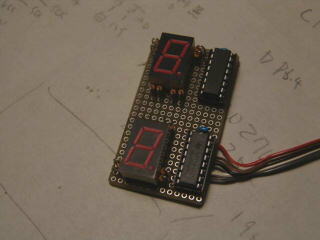

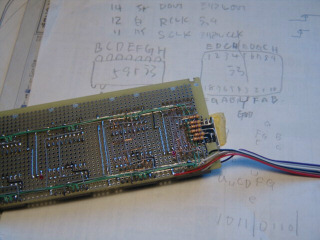

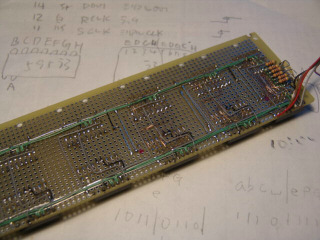

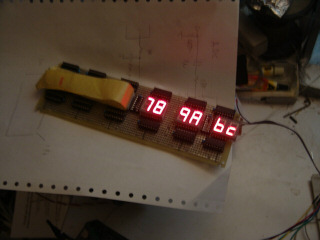

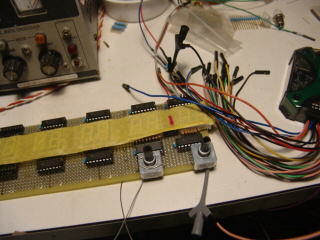

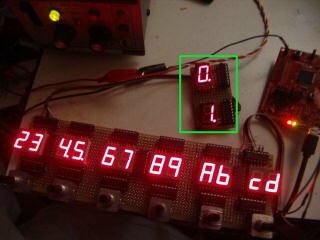

この週末は日曜日のみ作業です。パラメータ設定器のLEDの続きです。3〜4桁目完成しました。

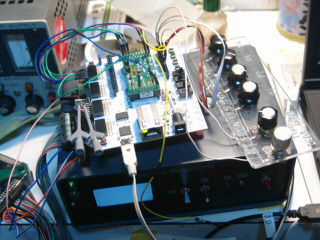

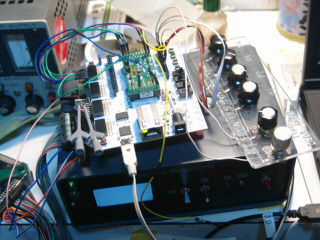

先週の混変調の続きです。48KHzのサンプリングを問題にしている波形の確認に48KHzサンプリングのSPI−DACから出力したのでは分からないので、デルタシグマDACを2ch実装して、モニタ出力として使用します。出力は簡単な一次フィルタを追加します。

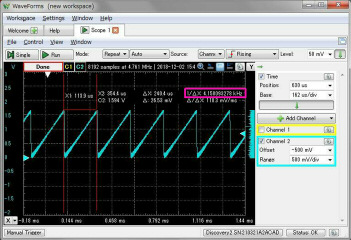

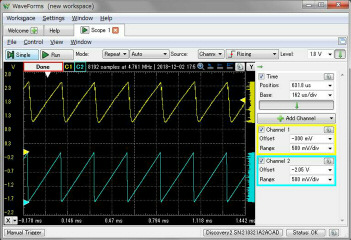

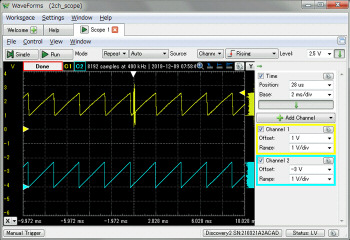

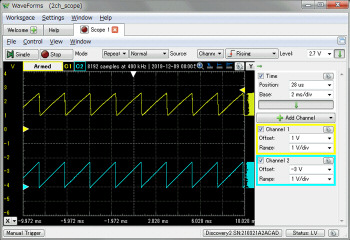

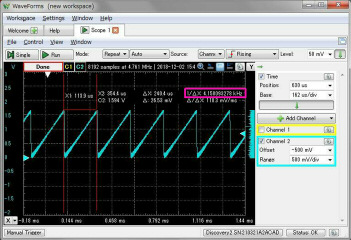

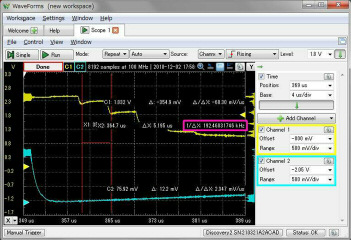

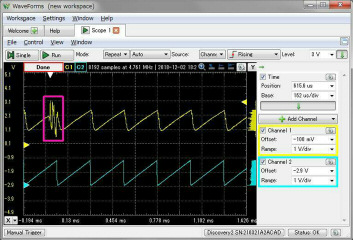

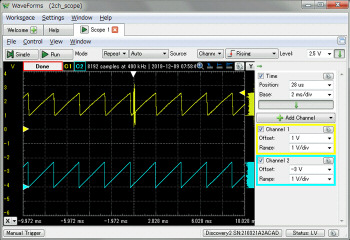

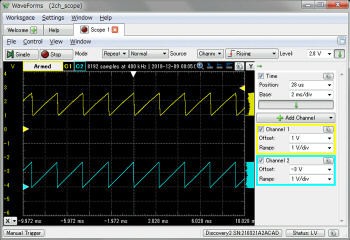

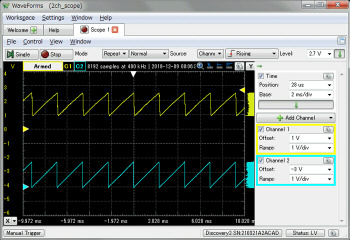

デルタシグマのクロックを15.36MHzにした時のDDS−DCOのノコギリ波です。ノート番号はC8で周波数は4.1KHzです。まあまあでしょうか?

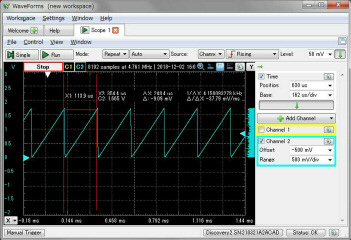

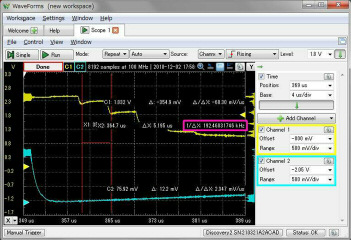

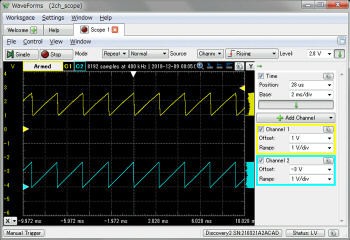

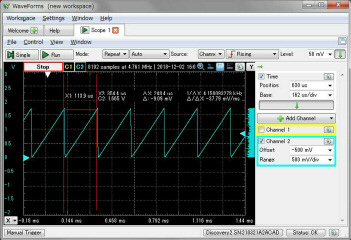

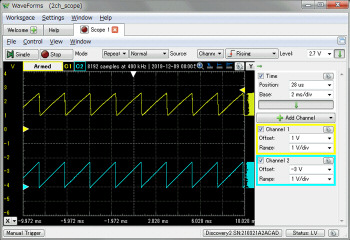

続いてクロックを100MHzにした時のDDS−DCOのノコギリ波です。流石に、100MHzでは非常にきれいに出力できています。

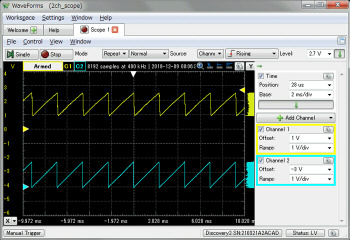

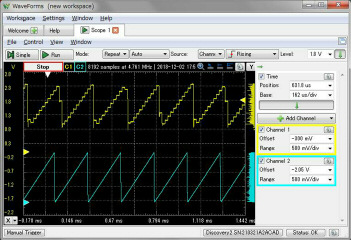

2chを使ってのモニタ出力してみます。上側の黄色は48KHzで読み出したラダーフィルタ出力です。

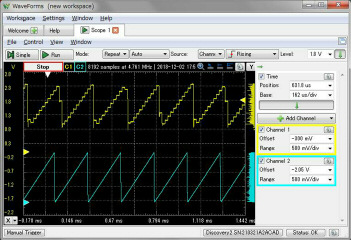

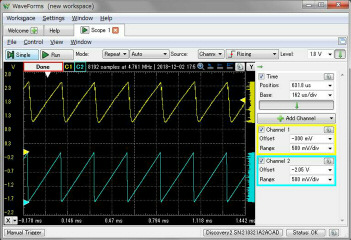

続いて、ラダーフィルタを4倍の192KHzで読み出してみます。混変調はかなり少なくなりました。

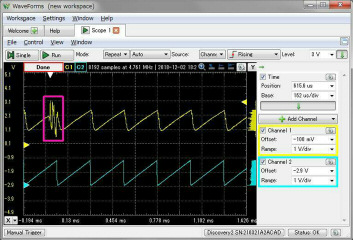

以前はパラメータ設定のプッシュボタンを押している時に偶にしか出なかったランダムなバーストノイズがかなり頻繁に出るようになりました。これは対策が必要です。DDS−DCOの出力は問題無く、ラダーフィルタで出力されているようです。電源をUSBケーブルから、ACアダプタに変更してみましたが、無関係でした。

12月8日

今

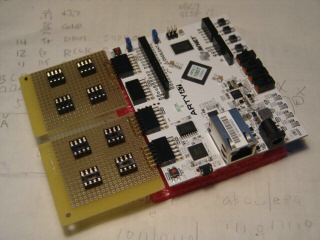

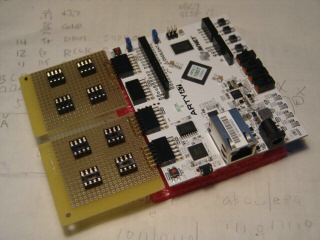

週末はやぼ用と運転免許の更新でガレージに帰れませんでした。アパートで作業します。だいぶ前に購入したARTY100Tのボードに2chのFPGAシンセをイ

ンプリしてみます。DigilentのサイトからボードファイルをダウンロードしてVivadoのディレクトリにコピーします。セッテイングを100Tに

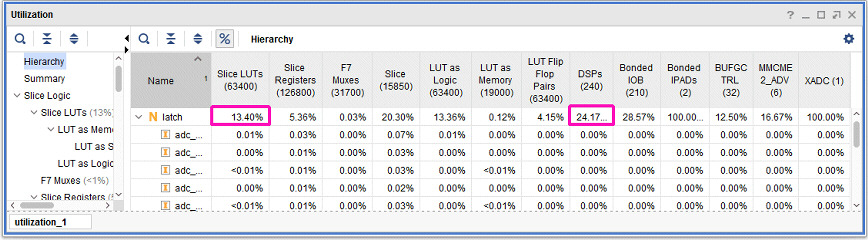

変更後、インプリしてリソースを確認します。音を出すにはボード裏にベースボードと接続するピンヘッダをハンダ付けする必要があり、次回に持ち越しです。

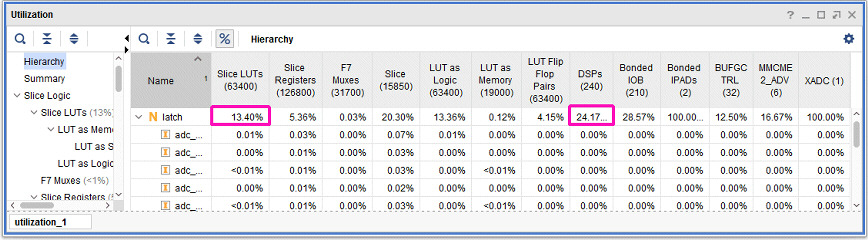

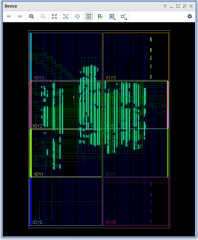

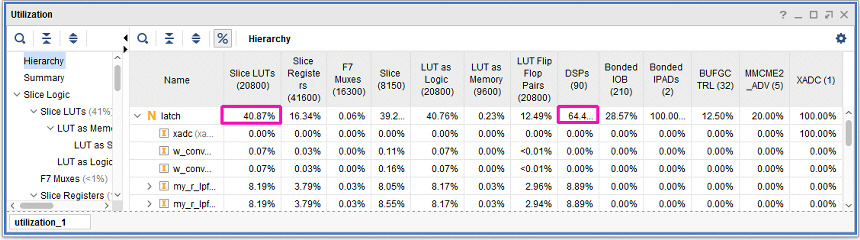

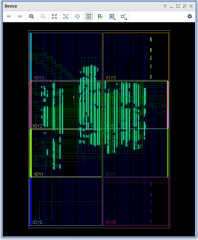

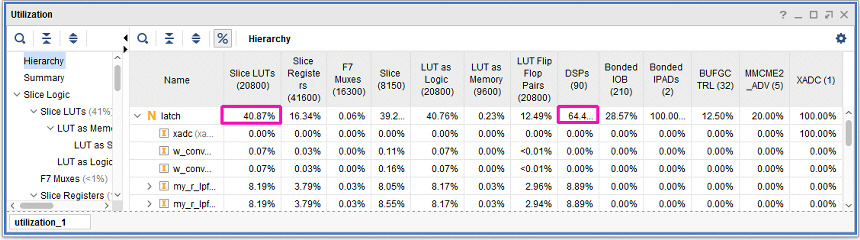

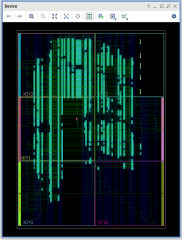

デバイスの図です。35−>100なので、ロジックの容量は約3倍です。入力データのラッチ、DDS、SPI−DAC、SPI−ADCの基本部は8ch分、その他ラダーフィルタ、DCA、EG,LFOは2ch分です。今後、SPI−DAC、SPI−ADCはデルタシグマに変更する予定です。

こちらは比較用の35Tのリソースです。

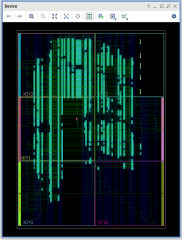

35Tのデバイスの図です。

12月9日

先

週からの続きのラダーフィルタからのノイズの件です。ボードは35Tです。FPGAに直接コンフィギュレーションした時です。右はUSB−MIDI変換の

MSP430とパラレルケーブルで繋がっている時です。MSPの電源は供給しています。右は繋がっていない時です。必ずこの様になるわけではなく、ケーブルが繋がっ

ていても、何度かコンフィギュレーションしているとノイズが出なくなります。

QSPIコンフィギュレーションした時はケーブルとは無関係にノイズは出ないです。実際はQSPIからコンフィギュレーションするので、大きな問題ではないのですが、気になります。

12月15日

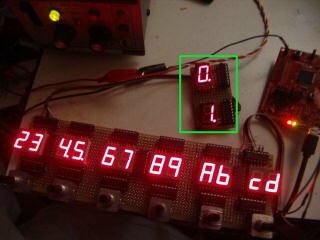

先週の続きのパラメータ設定器の7セグLEDです。6〜5桁目を作製して、パターンジェネレータで点灯させます。12桁の半分まで完成しました。問題なさそうです。

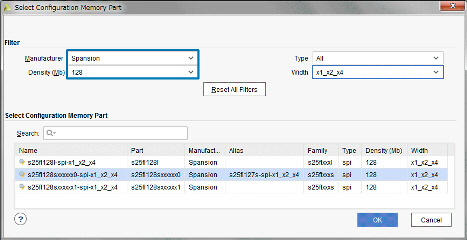

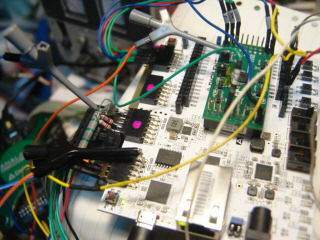

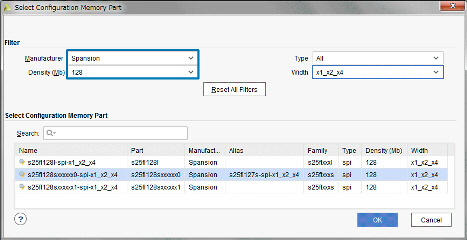

ARTY100TボードのVivadoプロジェクトにQSPIデバイスが未設定だったので追加します。メーカはスパンションです。追加後にBINファイルを書き込んで、電源投入で起動することを確認しました。

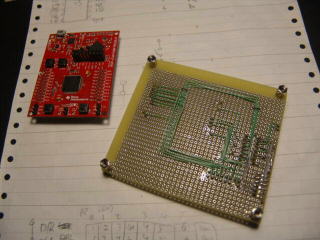

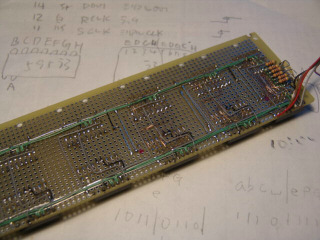

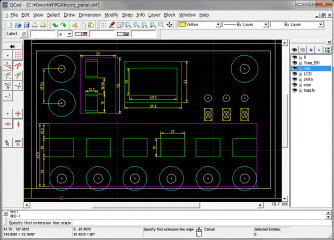

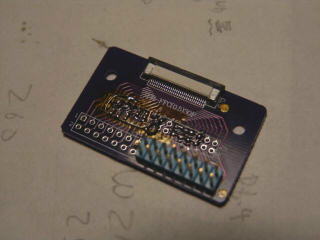

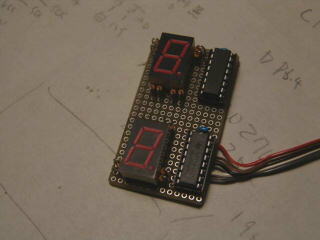

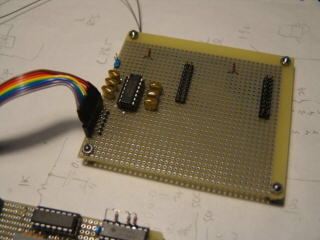

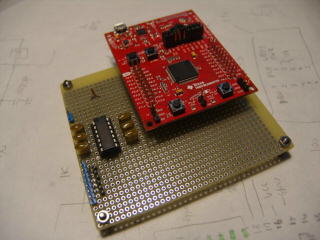

SPIのDAC、ADCはデルタシグマDAC、ADCに変更する予定です。PMODコネクタに接続するボードを作製します。ADCは1chあたり、2ポート、DACは1ポート必要です。直接外部にFPGAの信号を出さないように、オペアンプのバッファを追加します

100Tボードの裏側にピンヘッダをハンダ付けし、ベースボードに接続して音出し確認しました。今後、このボードにロジックを追加していきます。

12月16日

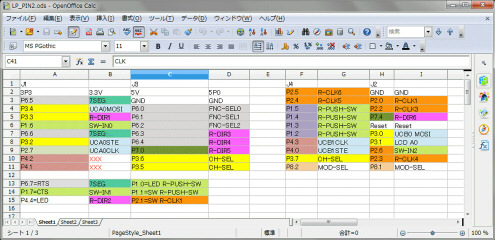

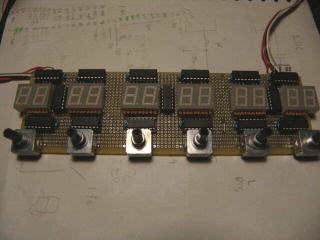

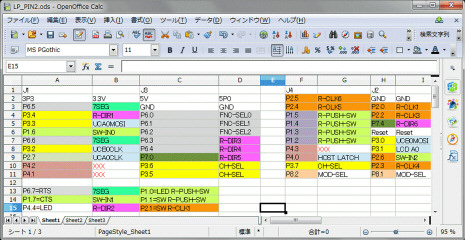

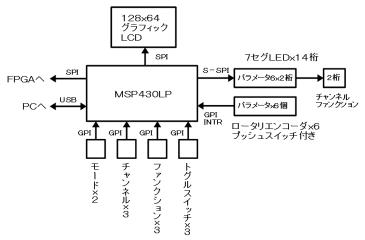

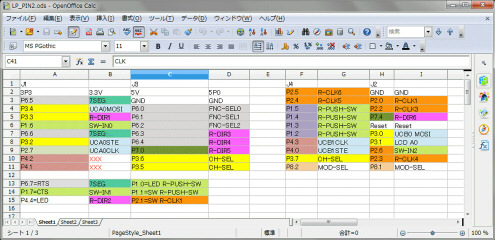

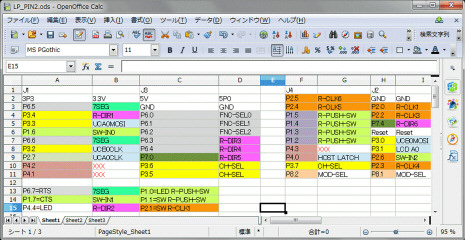

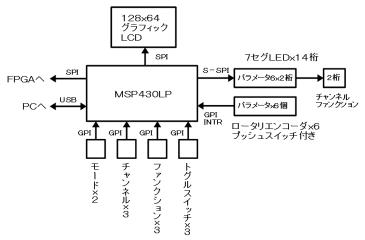

パラメータ設定器のMSP430のピンを機能を決定しました。主なIOはロータリエンコーダ入力、各種トグル/ロータリスイッチの入力、FPGAへのSPI送信、LCDパネルへのSPI送信、7セグLEDへのソフトSPI出力です。

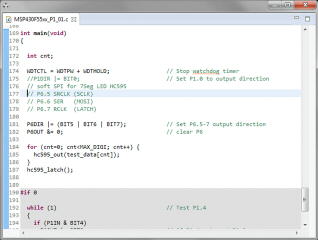

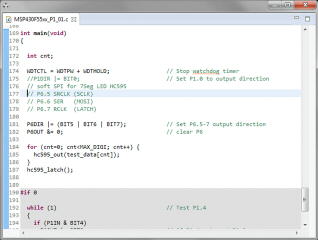

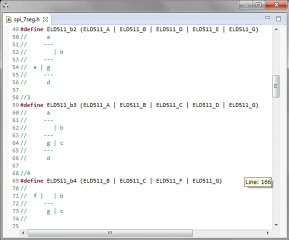

MSP430のGPOで制御するソフトSPIで7セグLEDを点灯させます。

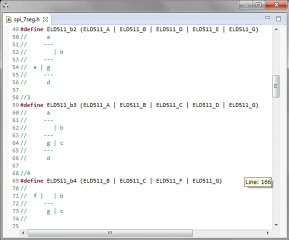

ポート出力のサンプルプロジェクトを変更しP6.5〜7の3ビットを使ったソフトSPIに修正します。DPセグメントの点灯機能は未実装です。

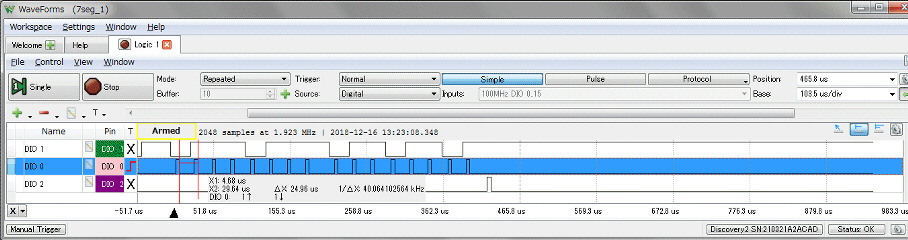

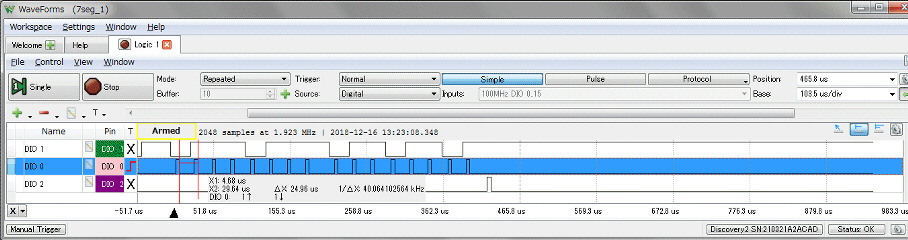

7セグのフォントパターンを定義して、16進数をシリアルに変換してポートに出力します。信号をロジアナで確認します。上からデータ、クロック、ラッチ信号です。

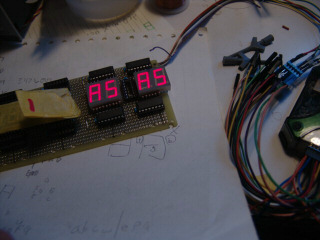

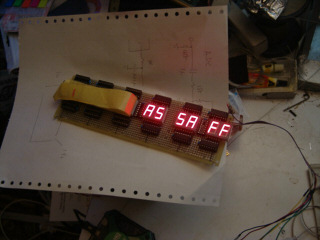

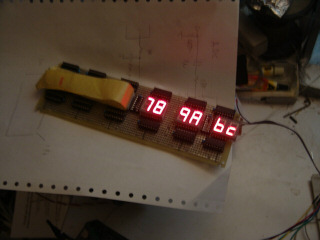

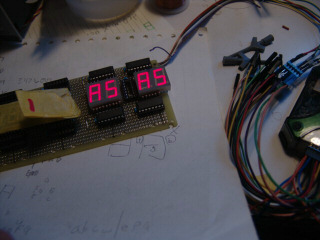

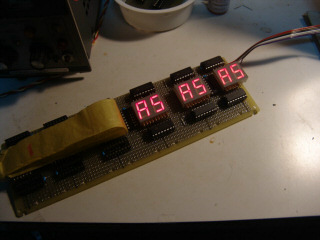

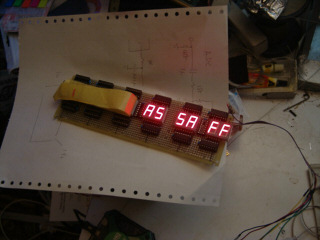

MSP430のプログラムで”A55AFF”を出してみます。良さそうです。

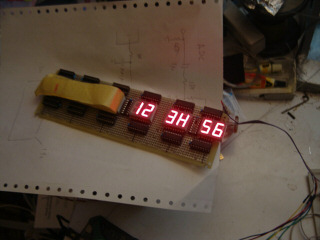

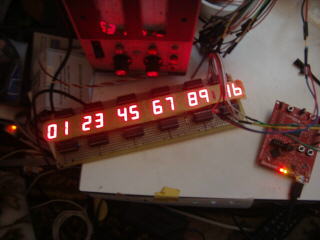

フォントパターンを順番にテストします。”123456”です。’4’が間違っています。

続いて、”789ABC”です。こちらは問題ないようです。

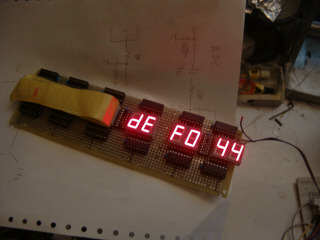

4のフォントパターンを修正しました。

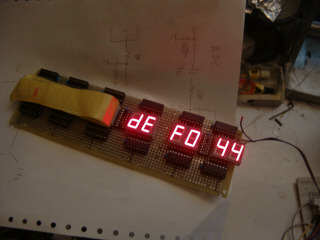

残りの”DEF0”と修正した’4’をテストします。正しくなりました。

12月22日

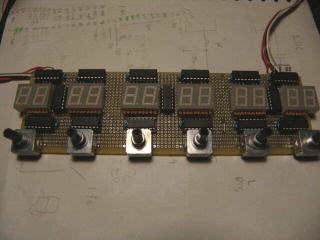

パラメータ設定器の7セグLEDの続きです。いっきに12桁まで作製してテストします。6桁目が間違えています。

配線ミスでした。修正して12桁全てが正常に動作するようになりました。

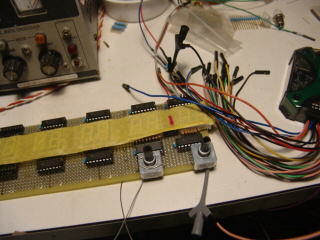

ロータリエンコーダの回路を追加します。HC74に接続してA/B相をディレクションに変換します。MSP430にはA相とディレクションを接続します。

ロータリエンコーダ6個の追加完了しました。このエンコーダはシャフトを押すとプッシュボタンにもなり、これは割り込み信号として、MSP430に接続します。

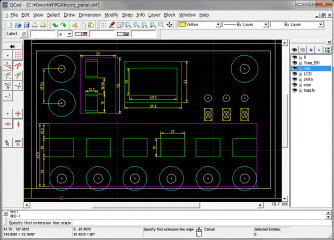

7セグLEDをもう2桁増設します。以前に作成したパネルの配置図から、他の部品と干渉しないように基板の大きさを決定します。

早速、ユニバーサル基板を切り出し、部品を実装して作製しました。上がチャンネル表示と下がファンクション表示です。

12月23日

追加した2桁も含めて全桁をテストを行います。DPセグメントも点灯できるようにしました。テストで1、2、5、6桁目を点灯しています。追加した2桁の輝度がちょっと低かったです。また、2桁目のファンクション表示は実際には数字ではないので、フォントとプログラムの追加が必要です。

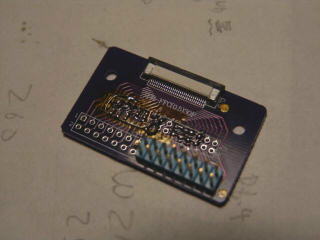

LCDのフレキ変換アダプタにコンデンサとコネクタを実装しました。

秋月からFPAGシンセ用のコンデンサ、抵抗などの部品が到着しました。筐体、電源はマルツから年末に届く予定です。

12月24日

MSP430のSPIとロータリエンコーダのピン設定を少し修正しました。ロータリエンコーダのA相クロックとプッシュスイッチは割り込み入力です。

パラメータ設定器のブロック図を作成しました。

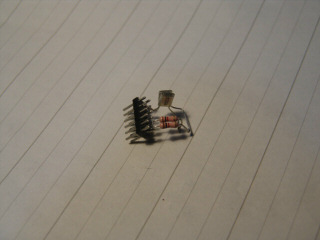

MSP430のベースボードを作製します。ロータリエンコーダのスイッチ用のチャタリング防止回路を作製しました。16ステップアナログシーケンサで使った40106(6入力シュミットインバータ)を使いました。

続いて、ロータリエンコーダのA相クロックとディレクションの配線を追加しました。