TK80/BSの

シンセシステムを復活/拡張したい〜

その33

パラメータ設定器作製

2018年

2018年

12月30日

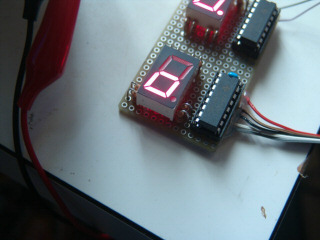

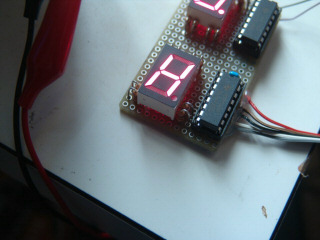

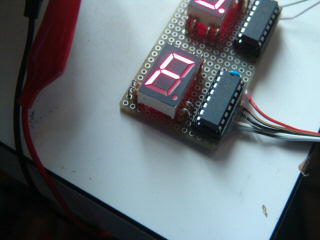

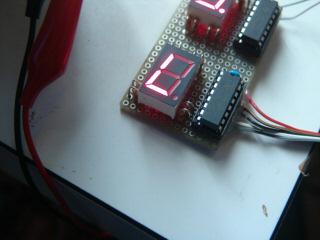

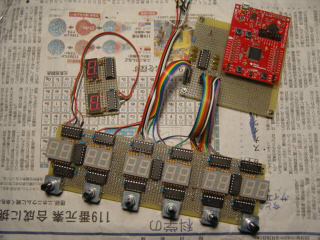

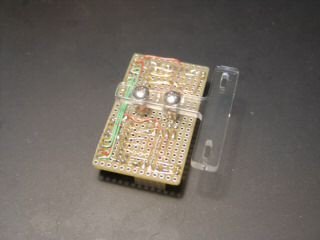

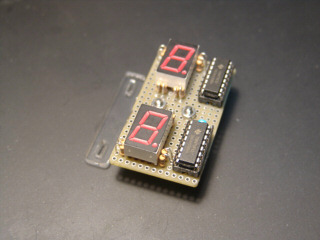

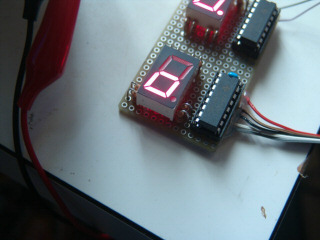

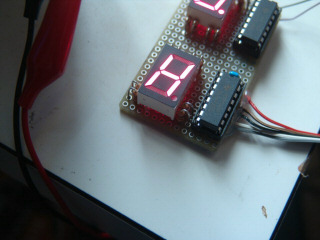

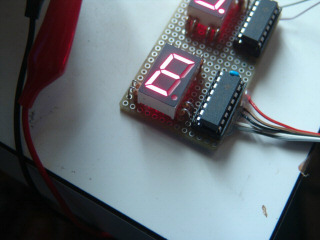

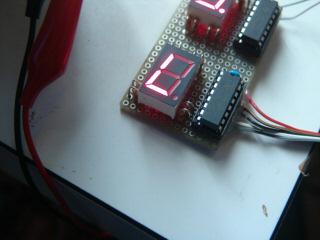

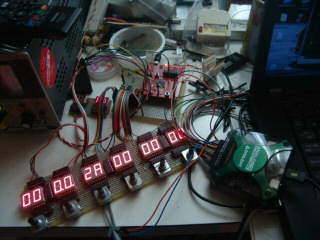

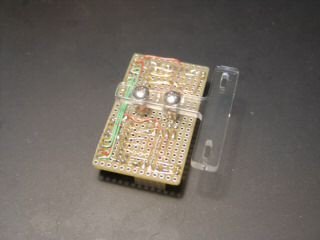

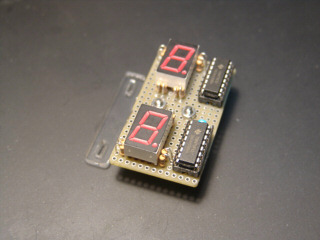

パラメータ設定器のファンクション表示の7セグLEDのテストです。DCOは’o’、MIXは’H’で代用します。

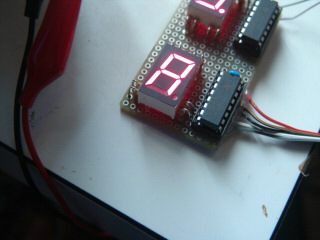

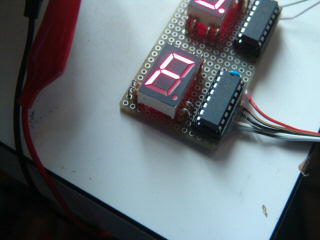

DCFは’F’、DCAは’A’これはそのまま。

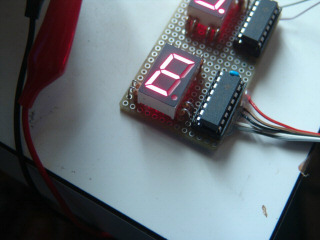

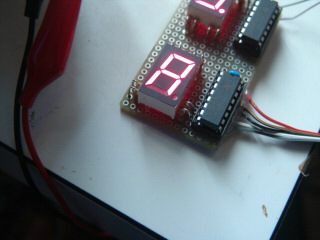

EGは’E’、LFOは’L’これもそのままです。’o’、’H’、’L’が新規フォントです。

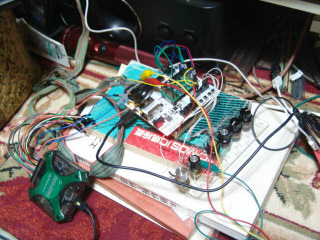

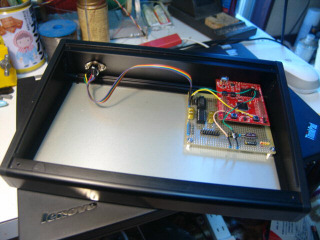

ロータリエンコーダとMSP430のベースボード間の配線を追加します。

FPGAシンセ本体のケースと部品がマルツから届きました。タカチのアルミケースはグレーが廃版で黒に変更になっていました。

12月31日

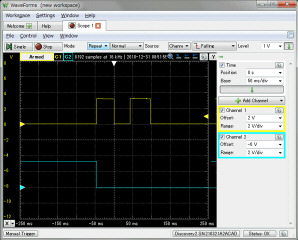

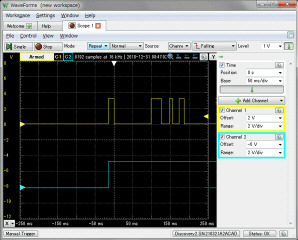

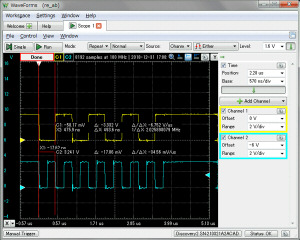

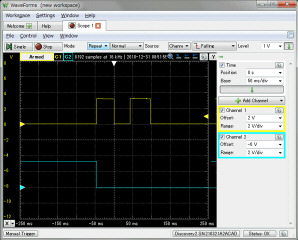

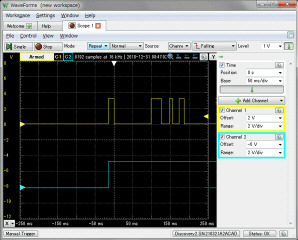

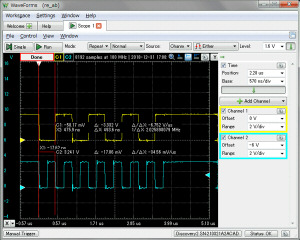

ロータリエンコーダの変換波形です。74HC74にA相、B相を入れ、ディレクション信号を生成します。上の黄線がA相、下の青線がディレクション出力です。A相の立下りで割り込み、その時のディレクションにより、数値をインクリメント、デクリメントします。

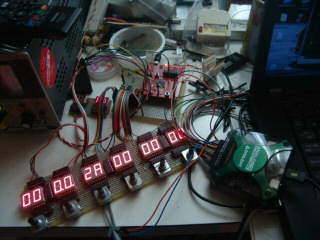

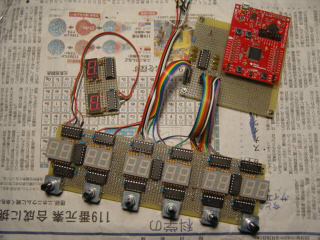

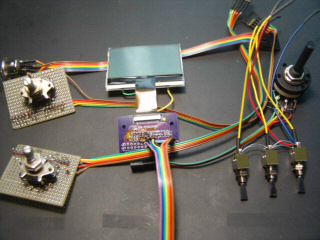

MSP430の割り込みプログラムを作成して、6個のロータリエンコーダの値を7セグLEDに転送し、エンコーダの読み取り、LED表示が正常に動作することを確認しました。

LCD用のSPIコントローラの動作テストを行います。CCSのSPIのサンプルコードを参考にコントローラ名を変えてビルドしてテストします。クロック周波数は約2MHzで1バイト(0x55)出力が正しく動作していることを確認しました。

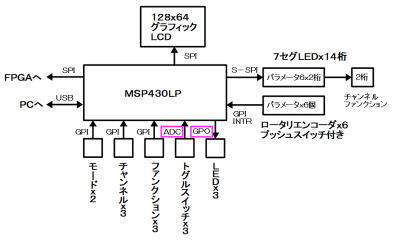

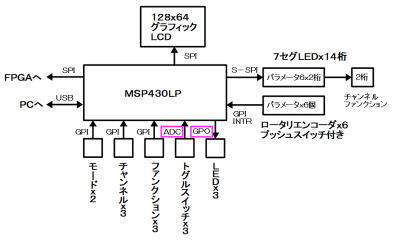

3個あるトグルスイッチは中点付きなので3つの状態を入力する必要があります。GPIに接続していましたが、ADCに変更します。ADCをスキャンモードで入力し、3値に変換できることを確認しました。値は一定周期で自動的に変換され、レジスタを読むだけで値が得られます。トグルスイッチの状態を表示するLEDも追加してブロック図を修正しました。

2019年

1月1日

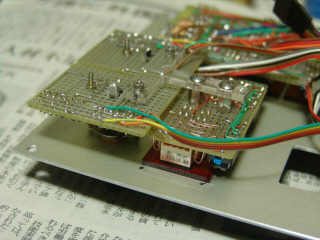

お正月です。FPGAシンセ本体とパラメータ設定器の間を接続する接続ケーブルを作製しました。両端は標準サイズの7ピンのDINコネクタです。SPIのクロックとデータ、ラッチ出力、電源で5本で接続します。

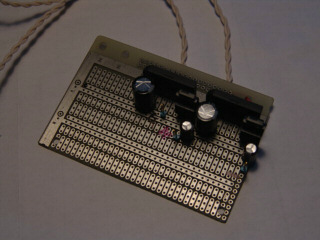

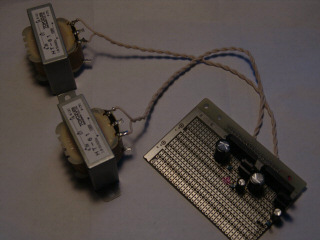

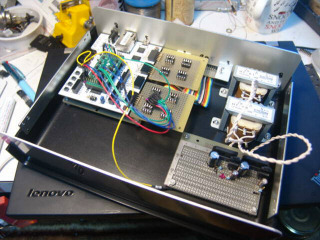

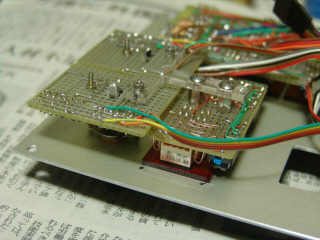

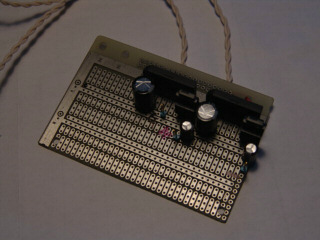

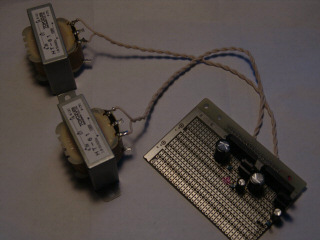

FPAGシンセ本体の電源を作製します。6Vのトランスを2個使用し、3端子レギュレータて+−5Vの電源を作ります。

以前に作成したFPGA−DDSのマイクロブレーズ用に作成したLCDのコントローラの制御コードをそのまま流用し、LCD表示のテスト表示を確認をしました。

1月2日

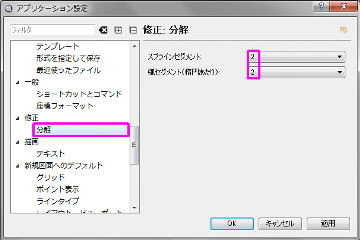

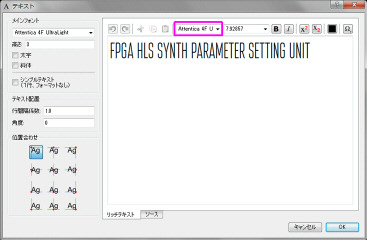

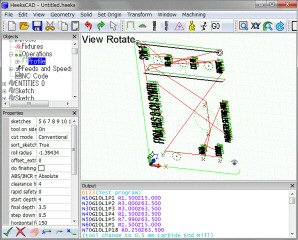

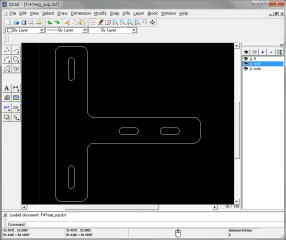

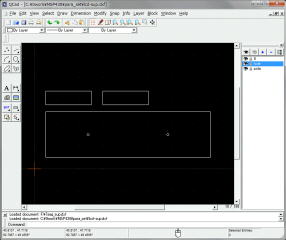

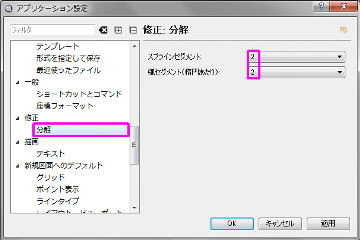

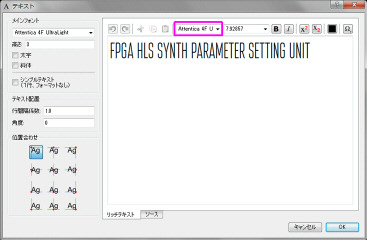

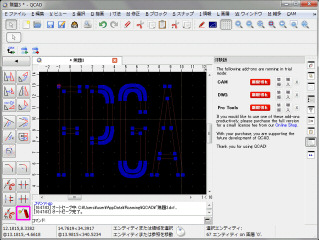

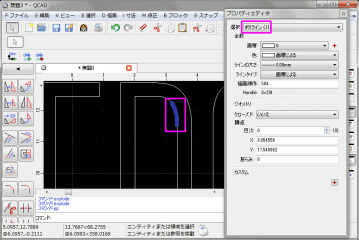

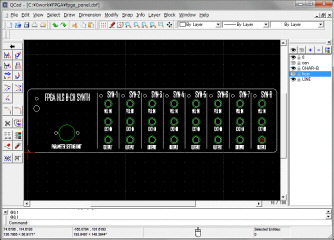

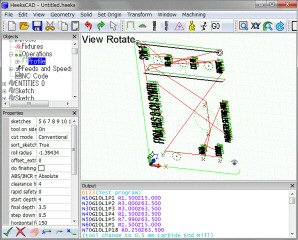

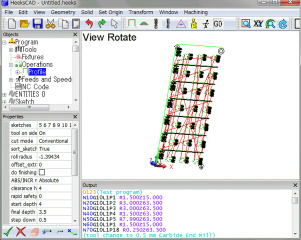

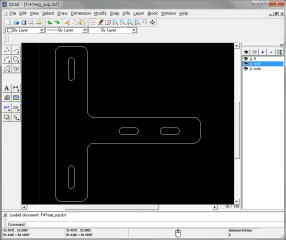

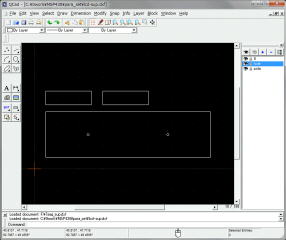

パラメータ設定器のパネルの刻印用の原稿を作成します。慣れているQCAD2を使用しますが、トゥルータイプフォントを使う時はQCAD3を使用します。トゥルータイプフォントを適当な密度のラインに変換する必要があり、忘れないように備忘録?として手順を残しておきます。まず、QCAD3の作業です。アプリケーション設定−>修正−>分解のパラメータ、スプラインセグメントと弧セグメントをそれぞれ2に設定します。その後、パネル刻印で使用している”Attentica”フォントを使って刻印する文字を入力します。

文字を囲って選択し、Explodeで2回分解します。トゥルータイプフォントがスプライン−>ポリラインに分解されます。この状態でdxfファイル(R15)でセーブします。

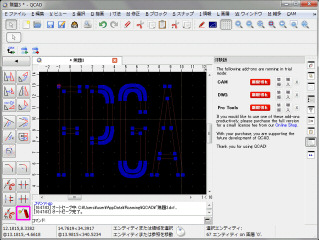

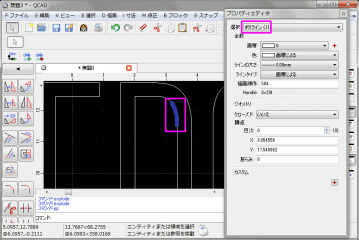

ここからQCAD2の作業です。dxfファイルを開き、文字を囲ってから、Explodeで1回分解します。これでトゥルータイプフォントがレーザ刻印に丁度いい密度の直線になります。

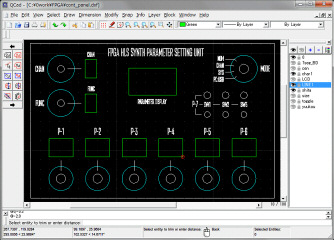

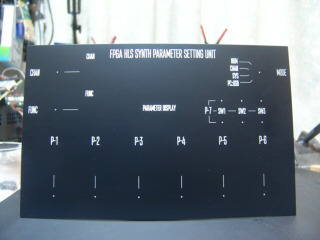

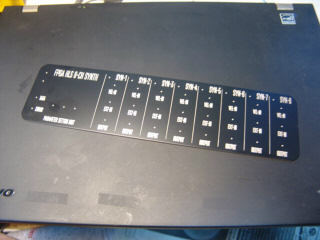

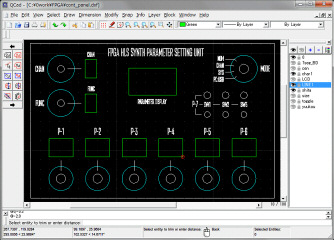

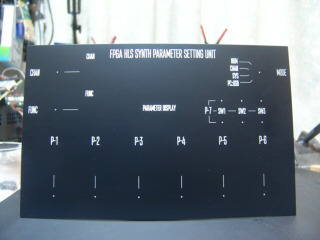

パラーメータ設定器のパネルにレタリングする原稿を上記の方法で作成しました。

1月3日

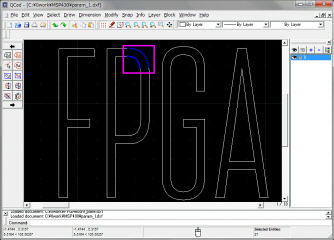

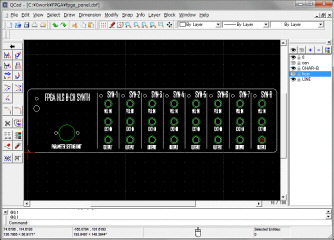

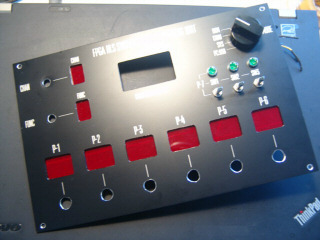

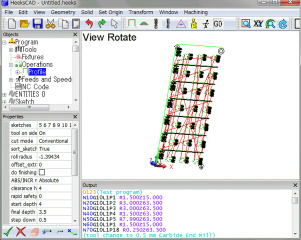

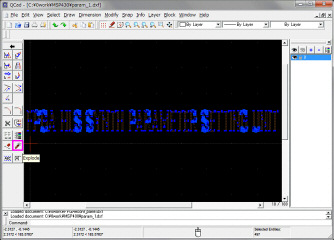

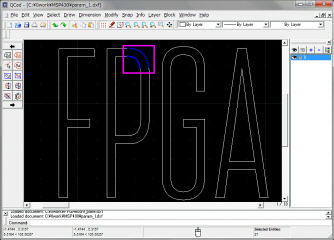

こちらはFPAGシンセ本体のパネルのレタリングです。

1月4日

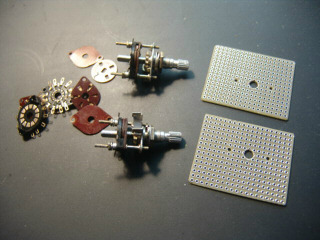

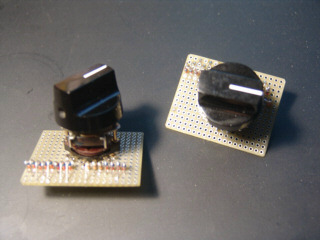

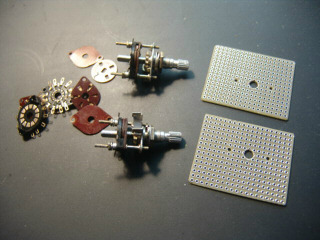

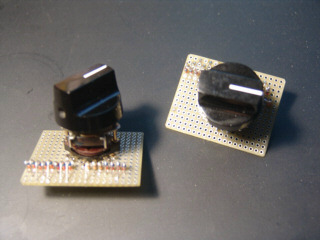

パラーメータ設定器に使用する2回路12接点のロータリスイッチを分解し1回路に改造します。代わりに8ポジションを3ビットに変換するエンコーダ基板を取り付けます。

ダイオードを使用した8to3エンコーダ回路を追加して、チャンネル設定、ファンクション設定用のロータリスイッチが完成しました。

1月5日

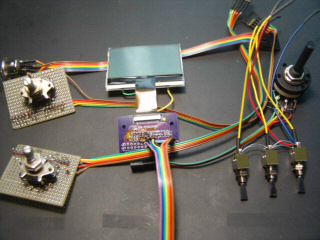

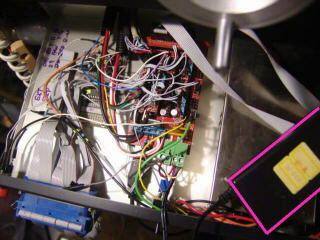

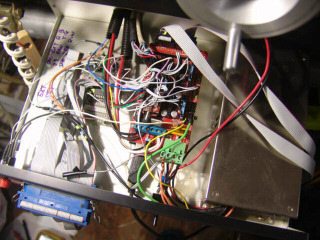

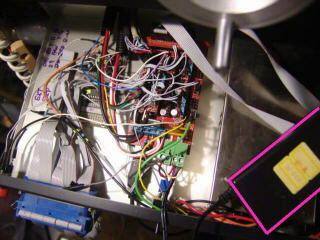

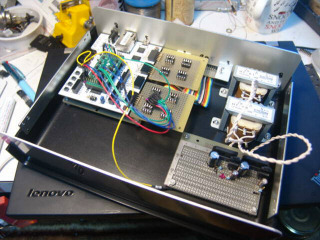

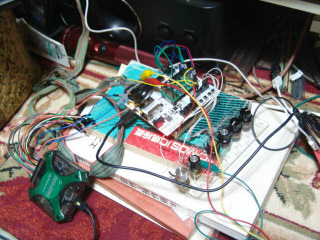

ロータリスイッチ、LCD、トグルスイッチとMSP430間を接続するケーブルを追加配線しました。

パネルにレーザ刻印しますが、レーザ加工機の制御BOX内の電源が壊れていました。マイクロSFX電源を改造してケースに組み込んでいました。5VはPCのUSBから、12Vは外部のACアダプタから供給して臨時対応しました。元々は3Dプリンタの制御用の電源なので、12Vはそこそこ電流が必要ですが、レーザ加工では12Vはほとんど流れません。

キーホルダをテストで作製しました。復活しました。

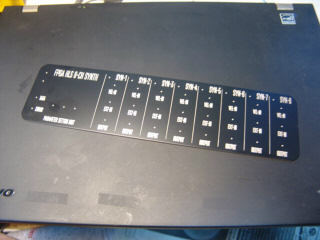

原稿を90度回転して上下を縦長にして刻印します。上下が範囲を超えているので、2回に分けて刻印して完成しました。

1月6日

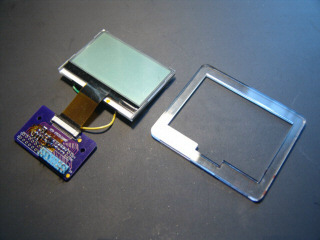

LCDパネルのホルダもレーザ加工で作製しました。

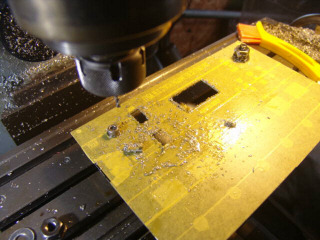

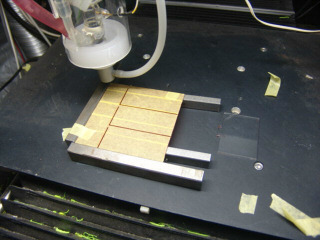

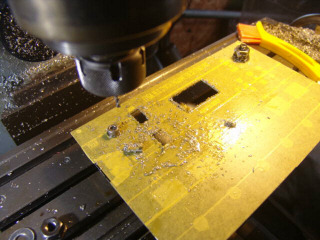

CNCフライスで7セグLED用の角穴を加工します。3mm径のエンドミルが切れないようで、いまいちバリが多かったです。試し切りをすれば良かったです。ヤスリで仕上げてロータリエンコーダ基板を仮止めしてみます。7セグLEDは2mm厚の透明赤アクリルを挟んで固定します。

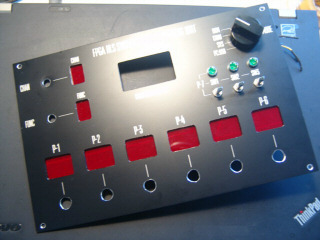

パネルをケースに仮止めしてみます。左側の7セグLEDとLCDの角穴と右側ロータリスイッチはシャフト径が太く、ツマミに入らないので次回、加工予定です。

1月9日

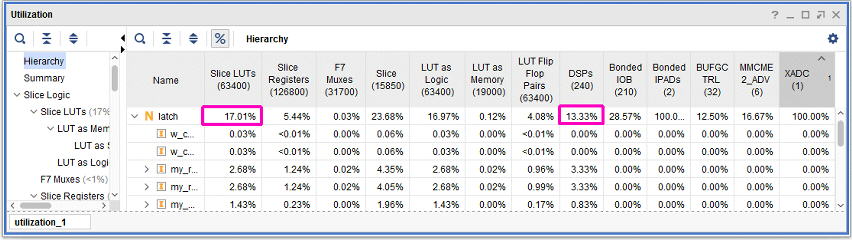

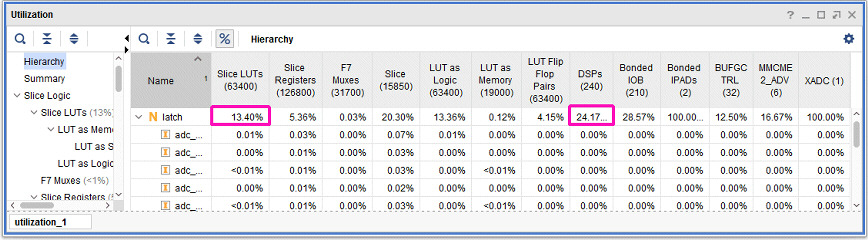

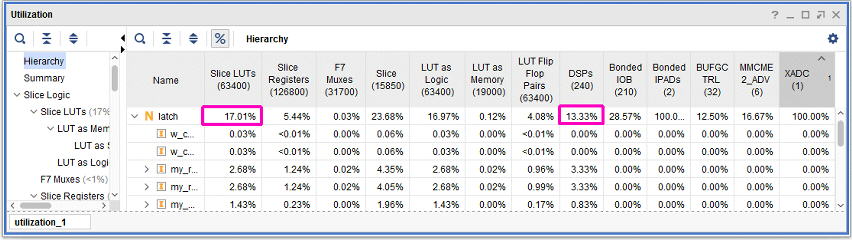

VerilogHDL内でDSP48Eを明示的に使わないようにすることができます。参考にしたのはこことここです。モジュールまたは、乗算計算単位で指定できます。今回はメインとDDSのモジュールに適応しました。結果は58個から32個にDSP48Eを減らすことができました。以下は使用しないように指定してインプリしたリソースです。DSPの代わりにLUTが増えています。インプリしただけなので、動作確認は今週末に行います。

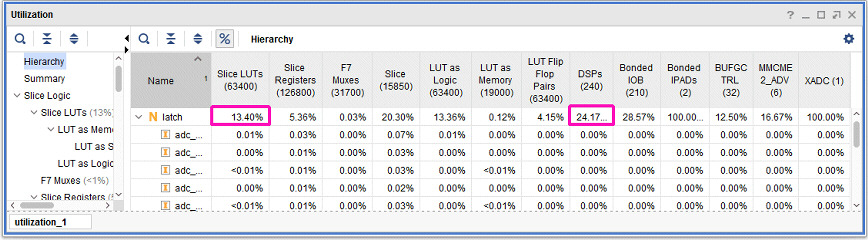

以下は比較用の以前のリソースです。

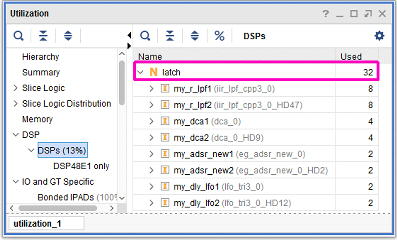

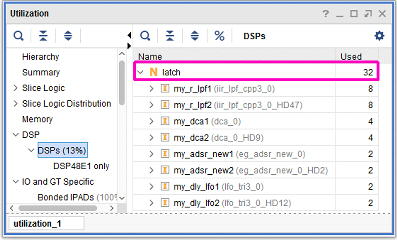

DSPのみ表示してみます。以下、使用しないように指定したDSPのリソースです。32個です。

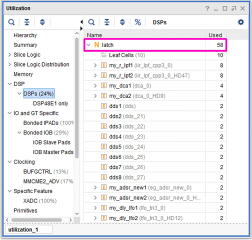

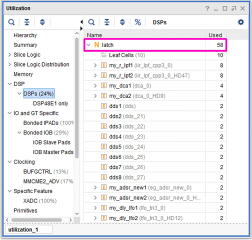

以下は比較用の以前のDSPリソースです。以前は58個でした。

1月12日

残りの7セグLED、LCDの角穴を加工しました。

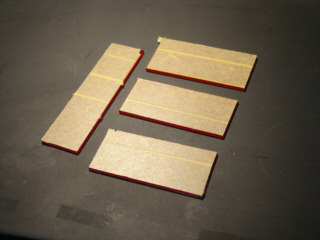

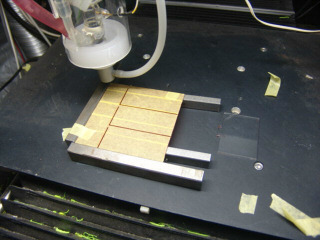

7セグLED用の透明赤アクリルをカットします。

1月13日

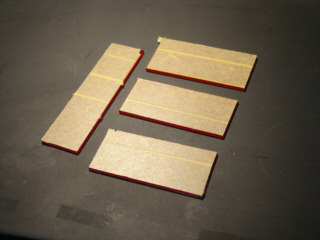

透明赤アクリルを両面テープで固定しました。

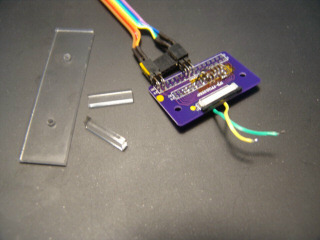

こちらはFPGAシンセ本体のパラレルケーブルの26ピン90度変換コネクタです。基板側は圧接、パネル側はハンダ付けです。筐体内で90度角度を変換します。

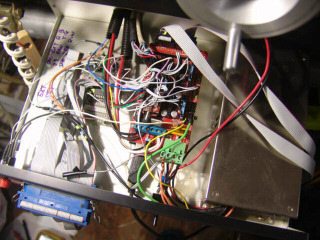

FPGAシンセ本体の筐体のリアパネルにマイクロUSBの角穴、AC100V用丸穴を加工して、部品を仮組みしてみます。まだ、パラメータ設定器からのSPI用バッファとシンセ出力のLEDインジケータ点灯回路が不足しています。

1月14日

パラメータ設定器のリアパネルにもマイクロUSBの角穴とDINコネクタの丸穴の加工をしました。

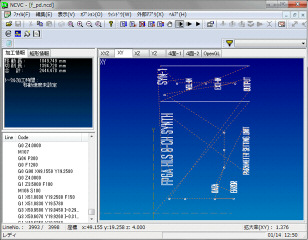

FPGAシンセ本体のパネルのレタリングの原稿を90度回転して、上下2つに分けます。丸穴はセンタポンチ用のマーキングをします。はじめは下側です。

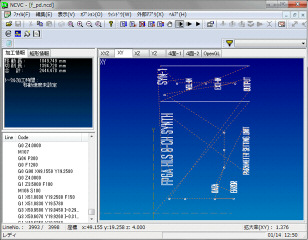

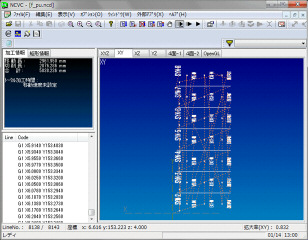

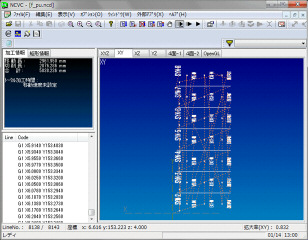

続いて上側です。それぞれ、HeeksCNCでGコードを生成して、レーザ加工用に変換、NCVCで確認します。

レーザ加工機でパネルに刻印します。

ドリルのマーキングにセンタポンチを打って、ボール盤で穴開け加工をします。緑LEDはエポキシ接着剤で固定し、他の部品も取り付けて仮組みしました。3mm径赤LEDの手持ちが無く、アマゾンに発注しておきました。

先週、Verilog内でDSP48Eの使用数を減らしたロジックの動作確認を行います。2chで音出しを行いました。基本動作は問題ないようです。

1月19日

チャンネルとファンクション表示の7セグLEDの固定ステーをアクリルで作製します。

レーザ加工機で3mm厚のアクリルを切り出して基板に固定します。

アマゾンから購入した3mm径の6色LEDが届きました。青と白も入って、60個で398円です。

先週、欠品だったエラーは赤LEDに、電源とDATAは一度、緑を外してから、オレンジと黄色に変更しました。

1月20日

チャンネルとファンクション表示の7セグLEDをアクリルのステーを使って、隣のロータリスイッチに固定します。LCD以外の部品の取り付けが完了しました。

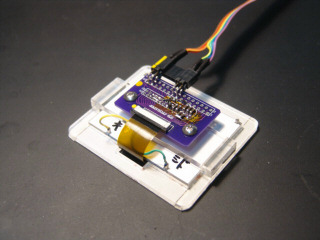

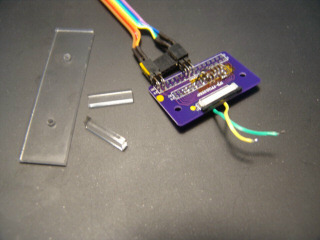

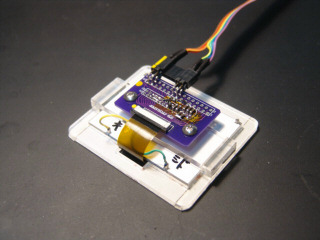

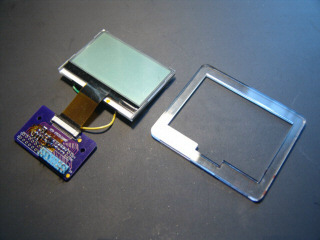

LCDのフレキ変換基板をLCDのホルダに固定するステーも作製します。こちらもレーザ加工機で切り出しました。固定穴は1mmでマーキングして2.5mmのドリルで穴開け後、3mmのタップでネジ切りしました。

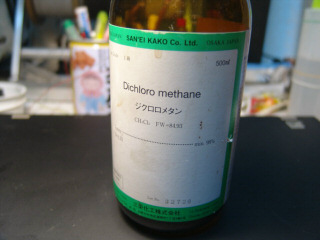

ジクロロメタンでLCDのホルダに切り出した部品を接着します。LCDのホルダは両面テープでパネルに接着しますが、パネルが上を向いているので、そのままでは剥がれる可能性があります。何か固定する方法を考えます。