TK80/BSの

シンセシステムを復活/拡張したい〜

その34

パラメータ設定器、FPAGシンセ作製

2019年

2019年

1月26日

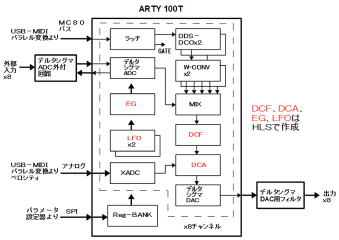

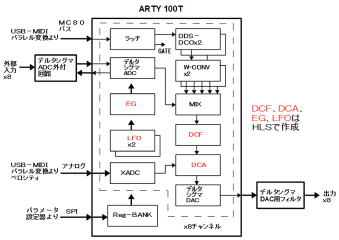

FPGAシンセのブロック図を作成しました。ロジックに余裕があれはDCOとLFOは2個実装する予定です。

先

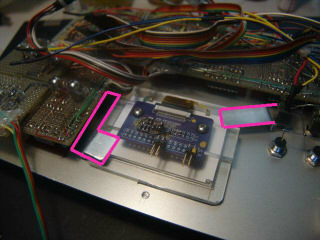

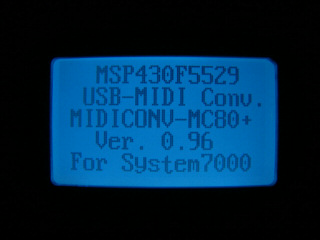

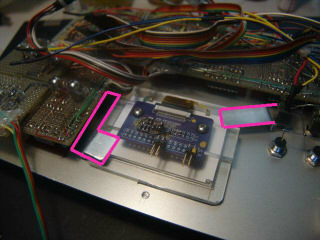

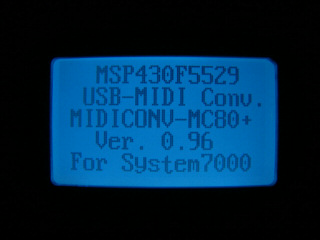

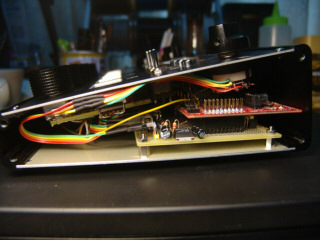

週の続きです。パラメータ設定器のLCDをパネルに固定します。アルミ板でステーを2つ作って固定します。片側はトグルスイッチと共締め、もう片側は両面テープで固定します。テストプログラムを走らせて表示位置を確認します。表示文字はUSB−MIDI変換器のスタート画面です。下側から見るので、少し上側にしました。

秋月からTK80/BS用のLCDモニタを購入しました。NTSCx2チャンネル、HDMIx1チャンネルのTFT10インチです。少し上に表示されますが、表示位置の調整はできないです。グリーンモニタの方が趣きがありますが、焼き付き防止と省電力のためLCDに変更しました。早速、FPGAトーンジェネレータの上に設置しました。

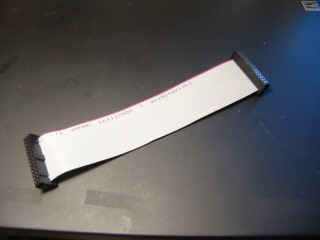

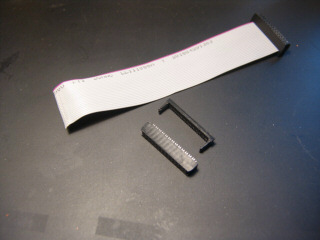

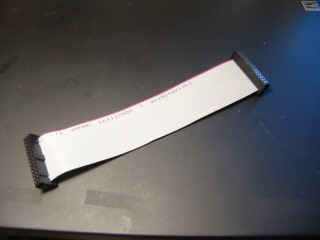

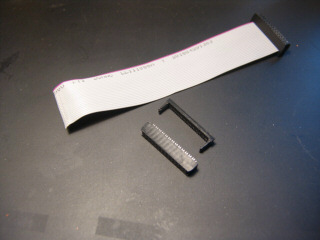

同じく、秋月で購入の26ピンのフラットケーブルです。ほしかったのは圧接コネクタです。コネクタ単体で売っていないので、ケーブルから外して使います。フックの部分が割れないように慎重に分解します。

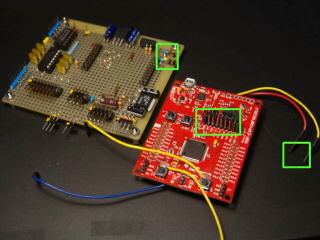

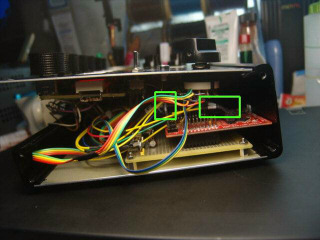

MC80バスの接続ケーブルに上記で外した26ピンコネクタを圧接します。ケーブルを仮接続してみます。下が現在作製中のFPGAシンセです。上に乗っているのは以前に作製したFPGAトーンジェネレータです。

パ

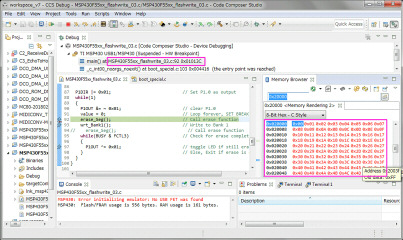

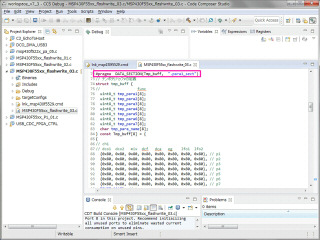

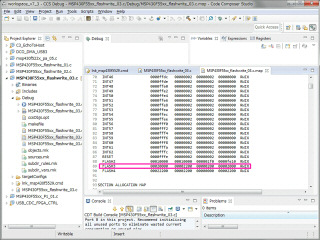

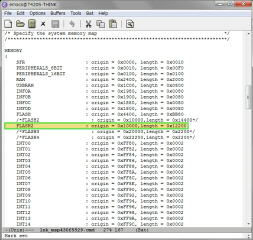

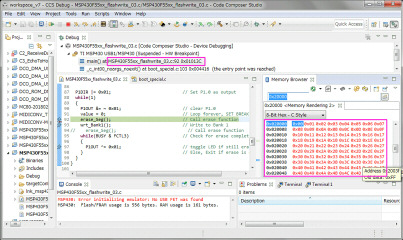

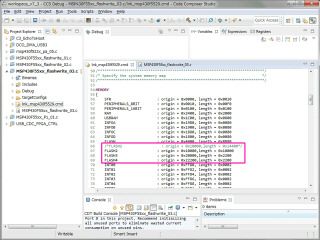

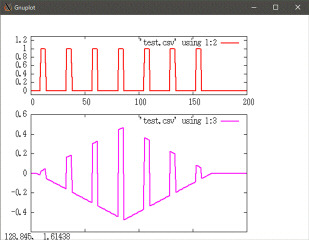

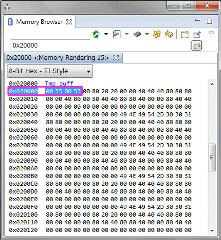

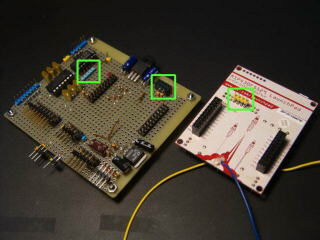

ラメータ設定器で使用しているMSP430のフラッシュメモリのイレーズ/ライトプログラムをサンプルコードから作成してテストしました。左はMSP430のメインフラッシュメモリのマップで

す。MSP430F5529のフラッシュは4バンクに分かれていて、プログラ

ムが動いてないバンクではイレーズしてライトできます。後半の0x20000から後ろをパラメータ保存用として使用します。セグメントは512バイトです。セグメント単位でイレーズして、書き込みができることを確認しました。

1月27日

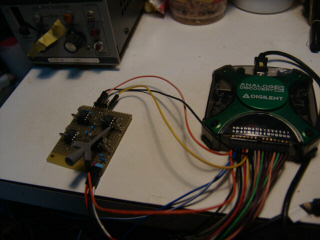

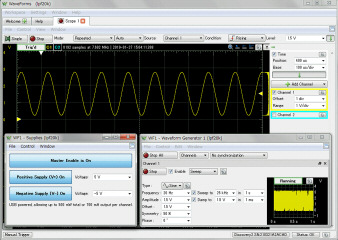

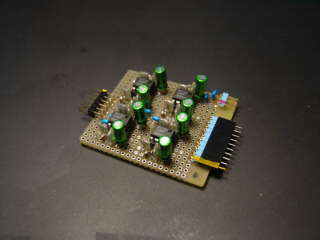

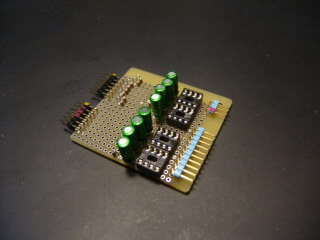

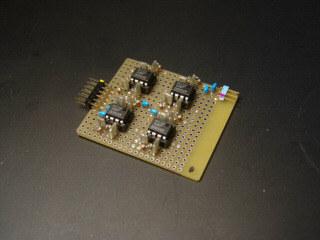

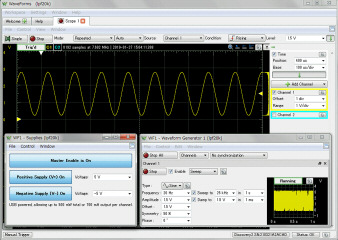

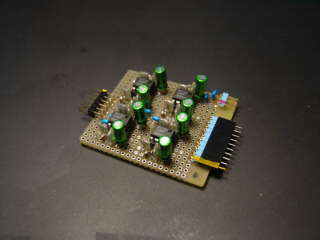

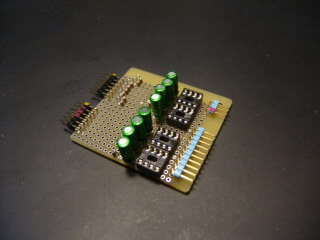

FPGAシンセ本体のデルタシグマDACの出力フィルタを作製しました。

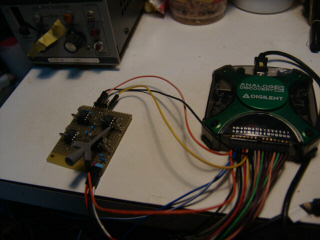

アナログディスカバリで動作確認を行います。1台で電源、波形スイープ出力、オシロになり、便利です。カットオフ周波数は約20KHzに設定しました。動作良好です。

出力のカップリングコンデンサを追加して完成しました。

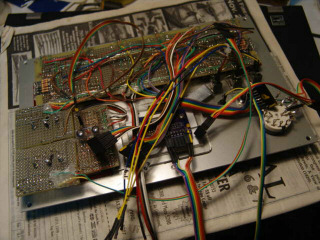

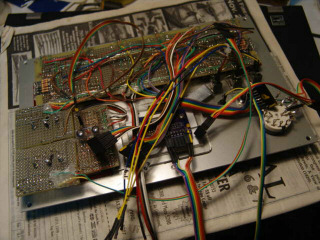

パラメータ設定器のパネルはMSP430間の接続ケーブルがたくさんあります。どうにかケースに収まりました。

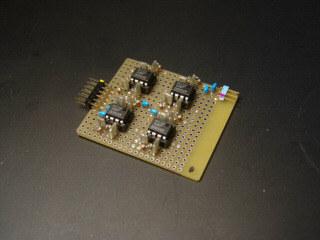

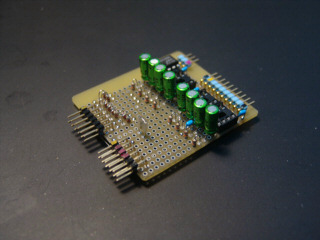

FPGAシンセのデルタシグマADCの外付け回路です。作製を開始しましたが、肝心のコンデンサを買い忘れていたので、マルツに発注しておきました。

1月29日

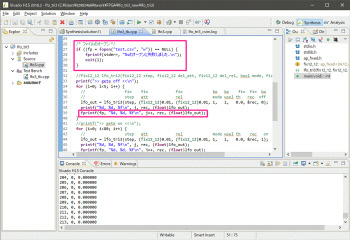

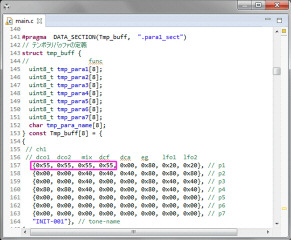

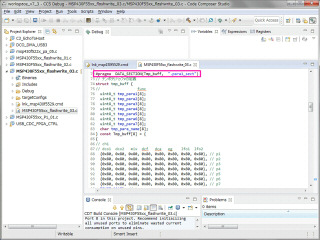

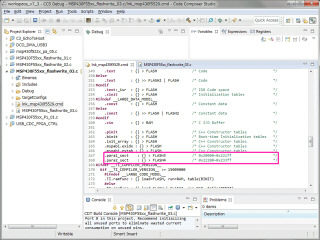

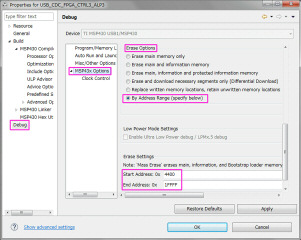

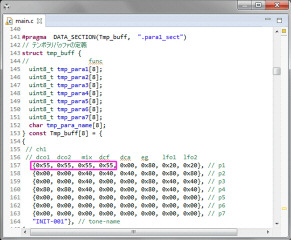

上記で0x20000番地のフラッシュをイレーズして、書き込めることを確認しました。変数をフラッシュの絶対番地に割り付ける方法がここにあり、構造体の配列を明示的に絶対番地に割り付けてみます。ソースは#pragmaで新しく作ったセクションに変数を配置するようにします。

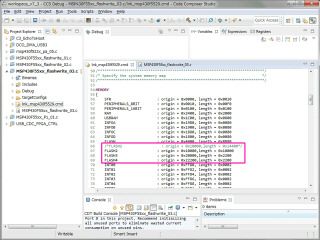

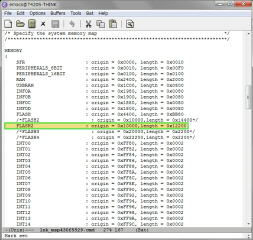

プロジェクト内のcmdファイルに新しいメモリエリアと上記のセクションを追加します。para1_sectとpara2_sectの2つのセクションを追加しました。アドレスが重ならないように注意します。

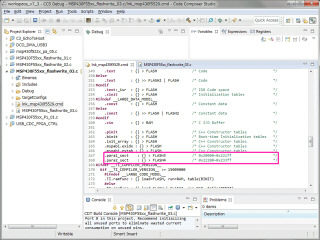

ビルドしてmapファイルを確認します。変数のTmp_buffが0x20000にマップされていること、メモリエリアで指定したFLASH3が0x20000にから0x200分使われていることを確認します。

2月2日

マルツで購入のパッチ用のマイクケーブルとデルタシグマADC用のコンデンサです。コンデンサは間違えて1個しか購入していませんでした。追加で購入しておきました。

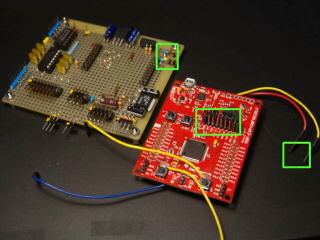

早速、1ch分デルタシグマADCに実装しました。FPGAにデルタシグマADCのロジックを追加開始しました。

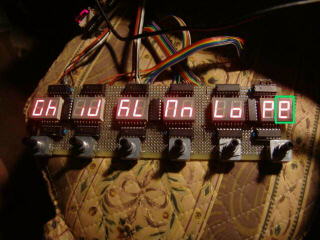

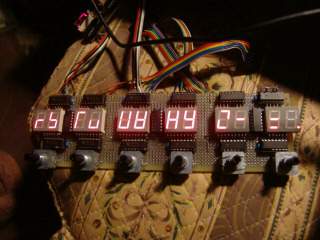

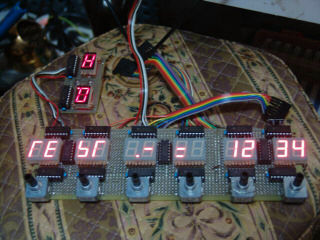

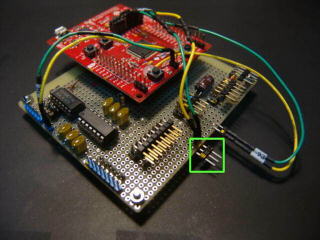

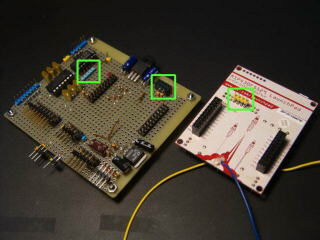

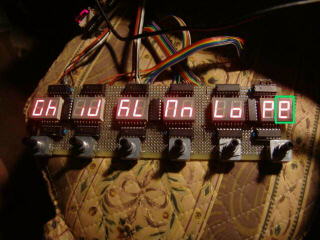

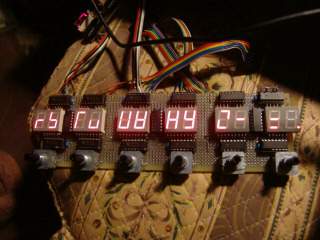

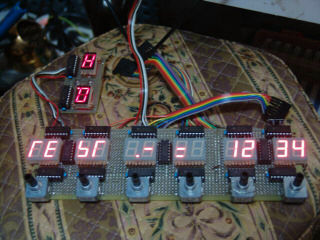

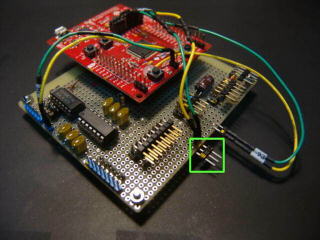

7セグLEDは一応、アルファベットが表示できます。元ネタはここです。フォントを作成して表示してみました。Tはいまいちなので変更しています。左はG〜Qまで、Lが重複しています。右はR〜Zと追加記号の−、=、.です。右の緑枠のQのフォントは分かりにくいので、数字の9に似たフォントに修正します。

文字列を表示する関数を作成して、”TEST.−= 1234”を表示したところです。

2月3日

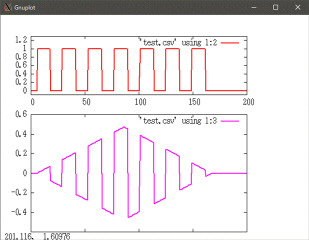

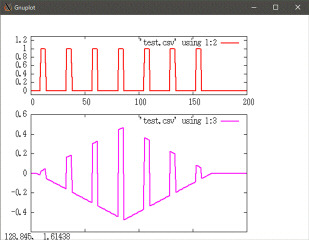

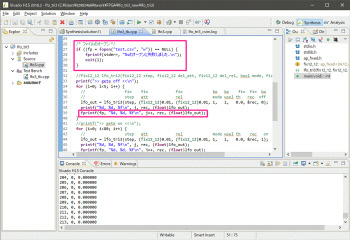

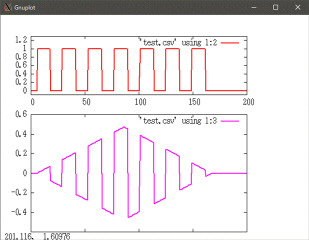

FPGAシンセ本体のHLSで作成したLFOを修正しました。LFO波形の三角波とPW波の選択に追加して、他のEGなどに使うゲート用PWを同時出力します。タイミングはPWと同じですが、レベルは0または1の信号です。三角波とPW波の出力はreturn値(ap_ctrl_chainハンドシェイク)で戻し、ゲート用PWはポインタ渡しで戻しました。今まで、HLSの動作確認はオープンオフィスの表計算で波形確認をしていましたが、操作が面倒なので、GNUPLOTで出力します。HLSのテストベンチは普通のCのプログラムなので、出力結果をCSVファイルに出力します。

GNUPLOTでCSVファイルを読み込み、フィールドを選択して、2つのグラフを上下に配置します。上がゲート用のPWで、下が通常のディレイドLFOのPW波形です。左は閾値が0.0、右は0.3です。ゲート用のPWはシンセ内部でEGなどに接続して使用します。

2月9日

マルツから追加分のデルタシグマADC用のコンデンサが来ました。送料が発生しないように、パッチ用の3.5mmのモノラルプラグも購入しました。黄、白、赤です。

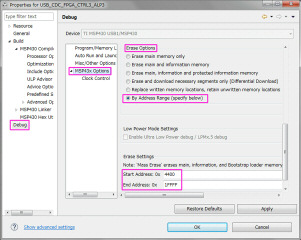

パ

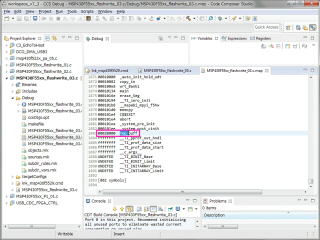

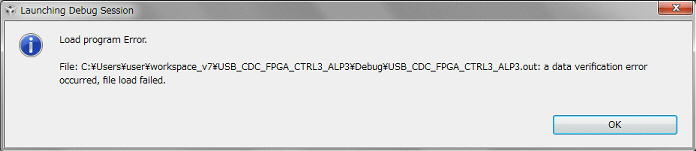

ラメータ設定器の初期化パラメータは電源投入時にフラッシュからRAMに転送して使う予定でした。ここで問題になるのはプログラムの更新時にフラッシュが上書きされてしまうことです。CCSの設定で特定のアドレスに書き込まないようにする設定がないか調べてみましたが、無いようです。ただ、フラッシュをイレーズするエリアの指定ができ

るので、試

してみました。0x20000以降をイレーズしないように設定してみます。

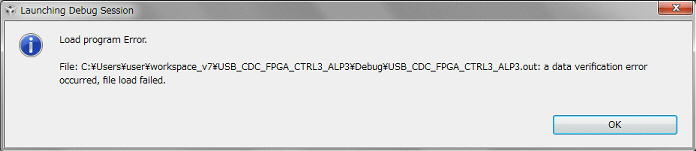

その後、プログラムを書き込むと、以下のようなエラーになりました。フラッシュが書けないというエラーです。これは0x20000以降をイレーズせず、書き込みを行っているからと思われます。フラッシュは1を0にする書き込みしかできないので、エラーになります

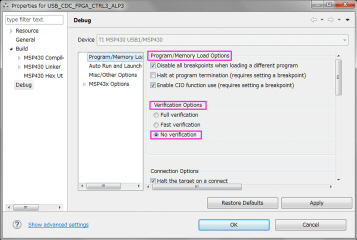

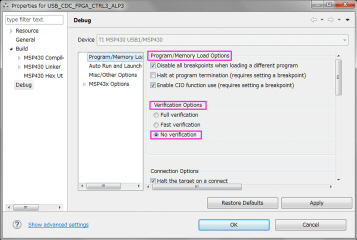

別のプロパティにはべリファイを行わないという設定もありました。この設定を行うとエラーは出なくなります。

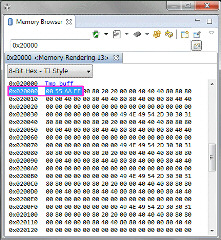

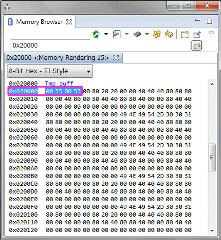

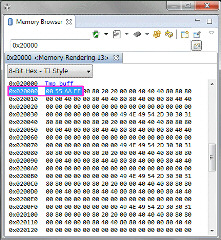

この設定で、パラメータの先頭をx00、0x55、0xaa、0xffにした後で、デバッガでプログラムをロードして0x55、0x55、0x55、0x55を上書きしてみます。

結

果は0x00、0x55、0x00、0x55になりました。イレーズしないで、上書きしていることが分かります。これでは使い勝手が悪いので、方針を変え

て、初期化データをRAMに作り、プログラム内でフラッシュに書き戻すことにします。電源投入時はデフォルトでフラッシュからRAMに転送し、電源投入に特定のスイッチが押されていればフラッシュからRAMへの転送をスキップします。

リンカのcmdファイルで0x22200以降を使用しないように設定します。これで0x22200以降がCCSから使われなくなります。プログラムから使用できる領域は0x2200(17セグメントx512バイト)分で、自由にイレーズ、書き込みがができます。

<フラッシュの扱いの変更のまとめ>

・変更前

cmdファイルで0x20000以降のフラッシュにセクションを登録

このセクションに初期化データを割り付け

その他、チャンネル用メモリなどに使用

電源投入

・フラッシュ−>RAM−>FPGA

・パラメータ変更−>FPGA

・電源断前にプログラムでフラッシュへ書き込み

(問題点:プログラムの更新時に変更したフラッシュが初期化データで上書きされてしまう)

・変更後

cmdファイルで0x22200以降のフラッシュを使わないように設定

プログラムで0x22200以降をテンポラリバッファ、チャンネル用メモリなどに使用

<フラッシュに有効なデータがある時>

電源投入、crt0がRAMを初期化(デフォルト)

・フラッシュ−>RAM(上書き)−>FPGA

・パラメータ変更 -> FPGA

・必要があれば、電源断前にプログラムでフラッシュに書き込み

<フラッシュに有効なデータが無い時>

特定のスイッチ押しながら電源投入、crt0がRAMを初期化

・RAM−>FPGA(フラッシュからRAMへのコピーをスキップ)

・パラメータ変更−>FPGA

・必要があれば、電源断前にプログラムでフラッシュに書き込み

2月10日

3つあるパラメータのスイッチ用のLED信号が未配線だったので追加しました。

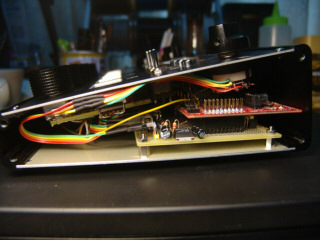

パネルの裏側のケーブルです。パラメータスイッチのLED配線も完了しました。先週はベースボードと接続しない状態で一応、パネルを閉めることができました。

2月11日

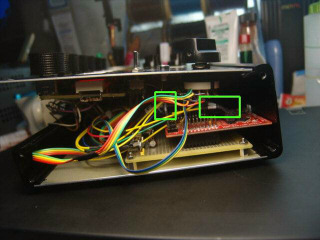

パネルとベースボード間を接続すると、パネルが閉まらないので、サイドパネルを外して確認します。トグルスイッチ、ロータリスイッチ付近がCPUボードの上部ピンから引き出している配線と干渉しています。

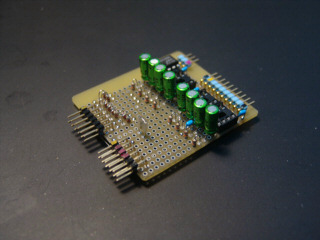

配線を上部ピンから取り出さなくてもいいように、CPUボードとベースボード間にコネクタを追加してベースボード経由で接続します。これで、高さが低くでき、パネルが閉まるようになりました。

CPUボードの電源のショートピンを外して、MSP430側の5Vと3.3Vとデバッガ側の電源を切り離します。7セグ表示の消費電流が約200mAと大きいため、5Vと3.3Vはベースボードから配線します。

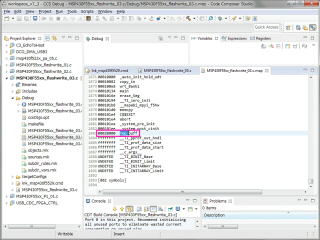

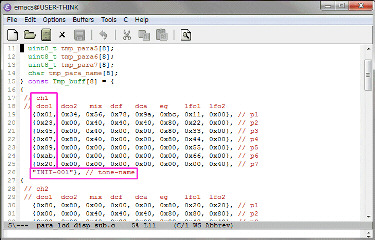

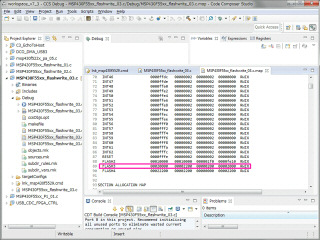

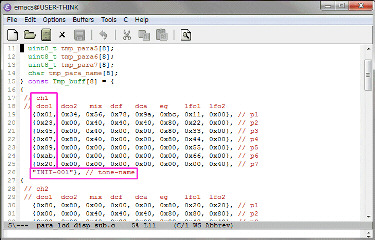

以下は仮入力した1チャンネル分のパラメータです。パラメータはチャンネルあたり64バイト、8チャンネル合計で512バイトです。8つあるファンクションに7つのパラメータがあり、最後のパラメータ7は3ビットのON/OFF情報ですが、1バイトを使います。8*7=56+音色名8文字=64バイトで、切が良いです。赤枠内はDCO1のパラメータと音色名です。これらのパラメータを文字列に変換してLCD表示するプログラムを作成します。

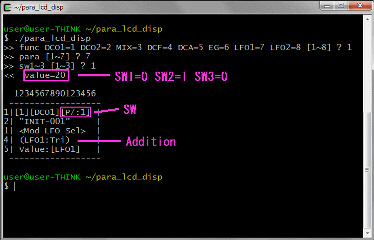

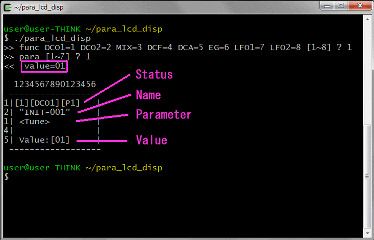

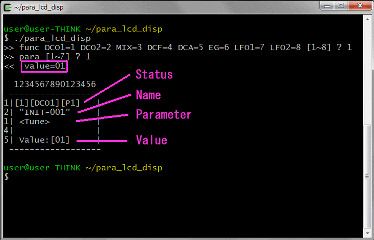

文字列の処理なので、Cygwin上のGCCで作成し、動作確認後にCCSに移行します。LCDは16桁x5行で表示します。下の例は、上からステータス、(チャンネル番号、ファンクション番号、パラメータ番号)、音色名、パラメータ名、設定値を表示しています。

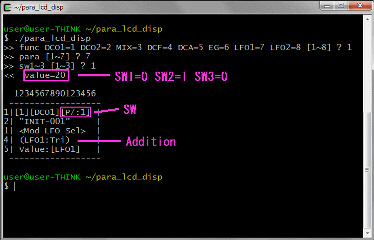

以下はパラメータ7のスイッチ1を選択した時です。補足説明(以下ではLFO番号と出力波形)がある場合は4行目に表示します。Cygwin上では、ほぼ動作するようになりました。