俿俲俉侽乛俛俽偺

僔儞僙僔僗僥儉傪暅妶乛奼挘偟偨偄乣

偦偺俁俆

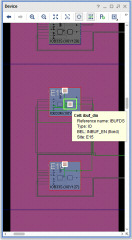

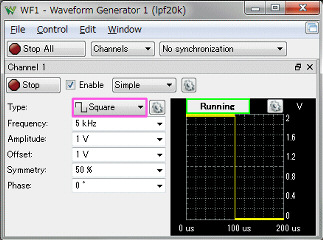

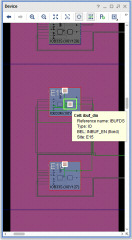

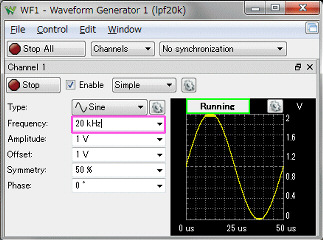

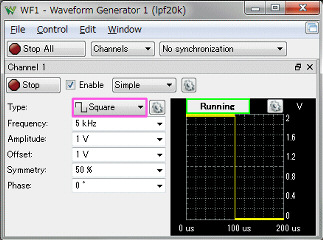

俥俹俙俧僔儞僙丄僷儔儊乕僞愝掕婍偺嶌惢

俀侽侾俋擭

俀侽侾俋擭

俀寧侾俇擔

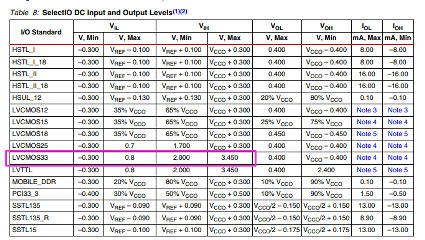

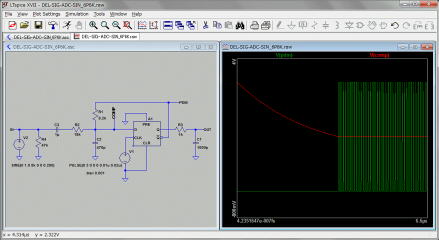

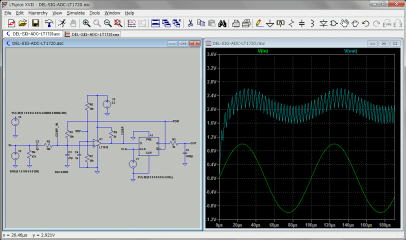

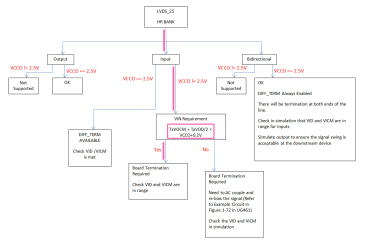

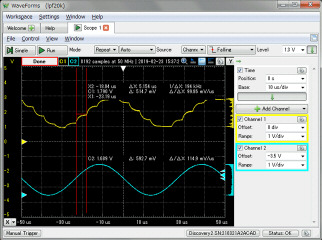

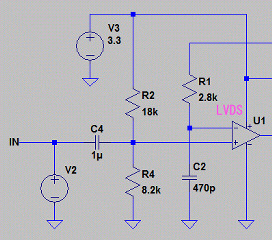

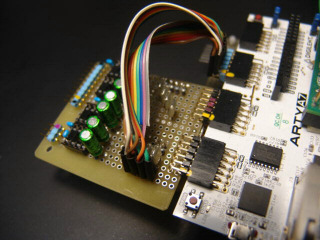

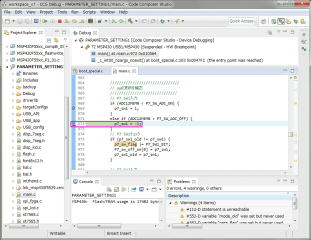

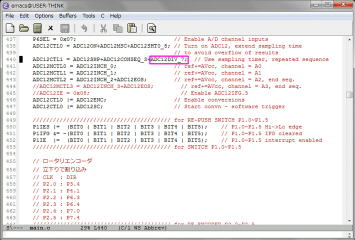

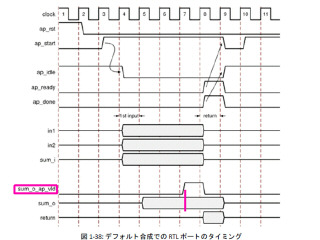

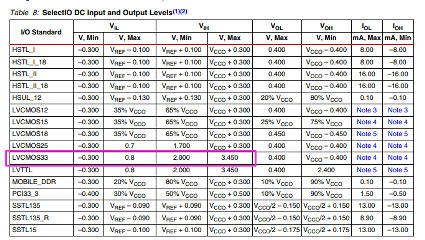

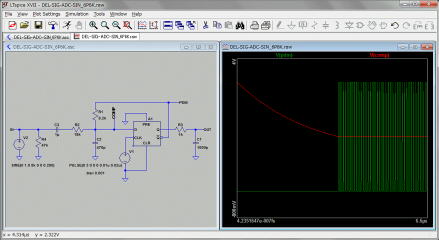

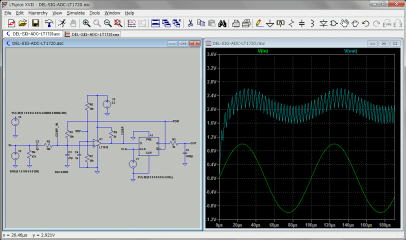

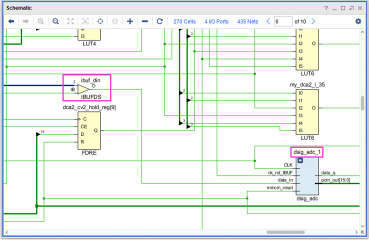

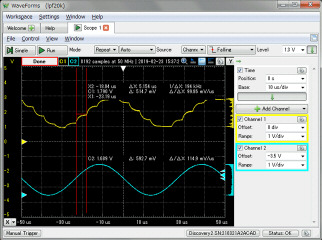

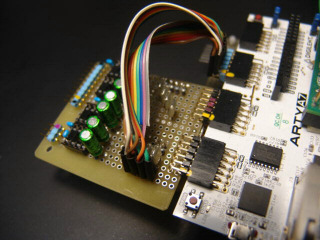

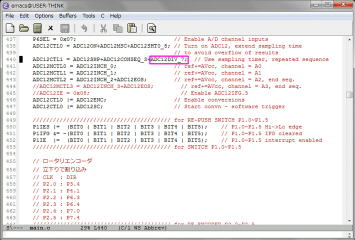

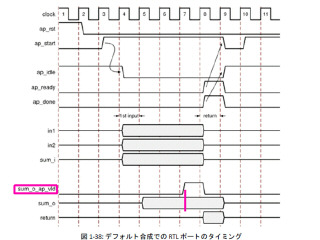

僨儖僞僔僌儅俙俢俠偺摦嶌妋擣傪峴偄傑偡丅偙偙傪嶲峫偵夞楬傪嶌惉偟傑偟偨偑丄偆傑偔摦嶌偟傑偣傫丅尨場偼俥俹俧俙偺擖椡偑棟憐揑側侾乛俀倁俠俠偺僐儞僷儗乕僞偱偼側偄偐傜偱偡丅塃偼僓僀儕儞僋僗偺俈僔儕乕僘偺擖椡摿惈偱偡丅捠忢偺俁丏俁倁偺俠亅俵俷俽儗儀儖偲摨條偱侽丏俉乣俀丏侽倁娫偼摦嶌偑曐忈偝傟傑偣傫丅

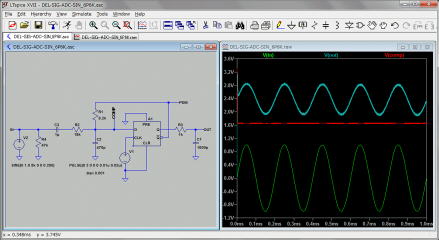

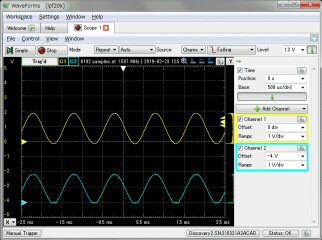

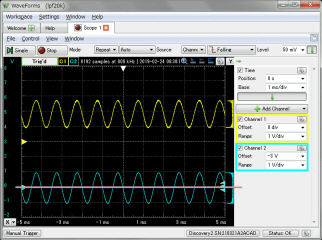

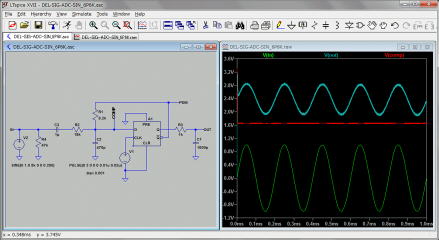

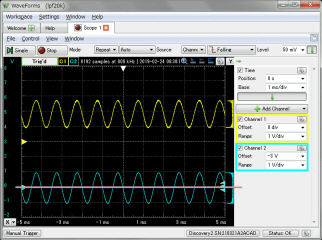

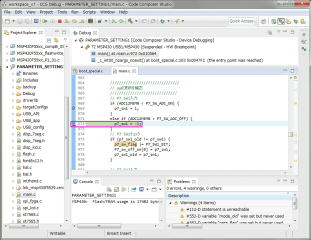

傕偟丄僨僕僞儖擖椡偑棟憐揑側侾乛俀倁俠俠偺僐儞僷儗乕僞側傜惓偟偔摦嶌偡傞偙偲傪俴倲倱倫倝們倕偱妋擣偟偰偍偒傑偡丅夞楬拞偺俢亅俥俥偼鑷抣傪揹尮偺侾乛俀偺侾丏俇俆倁偵愝掕偟偰偁傝丄僋儘僢僋偼俆侽俵俫倸偱偡丅擖椡俽俬俶攇偑僨儖僞僔僌儅俙俢俠偱俹俢俵怣崋偵側傝丄偦偺屻丄僷僢僔僽僼傿儖僞偱尦偺俽俬俶攇偵栠偭偰偄傞偙偲偑妋擣偱偒傑偟偨丅塃偺攇宍偼壓偐傜丄擖椡丄僐儞僷儗乕僞擖椡乮俢亅俥俥偺俢抂巕乯丄弌椡偱偡丅

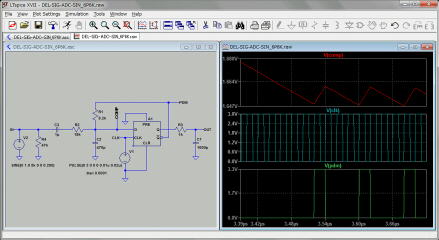

攇宍偺愭摢晅嬤偺僐儞僷儗乕僞擖椡偲俹俢俵弌椡偺攇宍傪奼戝偟偰傒傑偡丅

偝傜偵奼戝偟偰丄暿僌儔僼偵偟偰僐儞僷儗乕僞擖椡偲俆侽俵俫倸僋儘僢僋偺娭學傪妋擣偟傑偡丅僐儞僷儗乕僞擖椡偺僲僐僊儕忬偺攇宍偼僋儘僢僋偺敿暘偺惉暘乮俀俆俵俫倸乯偑偁傝丄侾丏俇俆倁偱僐儞僷儗乕僩偝傟偰偄傑偡丅奜晹偵僐儞僷儗乕僞傪愝偗傞応崌偵偼俀俆俵俫倸掱搙偺怣崋偑埖偊傞崅懍僐儞僷儗乕僞偑昁梫偱偡丅

俀寧侾俈擔

俴倲倱倫倝們倕偵搊榐偝傟偰偄傞傾僫儘僌僐儞僷儗乕僞傪俢亅俥俥偺庤慜偵愙懕偟偰傒傑偡丅儔僀僽儔儕偐傜丄崅懍僐儞僷儗乕僞俴俿侾俈俀侽傪慖傫偱傒傑偟偨丅

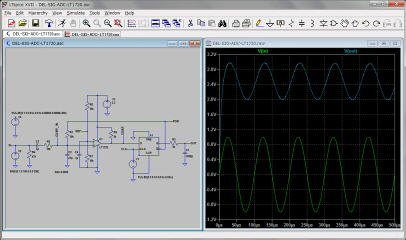

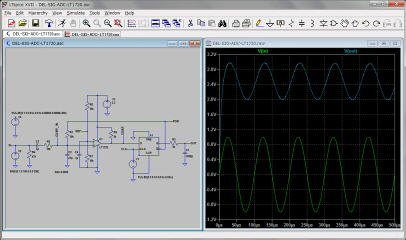

攇宍傪奼戝偟偰奺僞僀儈儞僌傪妋擣偟傑偡丅忋婰偺棟憐揑側俢亅俥俥偲摨條偺摦嶌偟偰偄傑偡丅

帋偟偵丄暿偺拞掅懍僐儞僷儗乕僞俴俿侾侽俉侾傪巊梡偡傞偲丄埲壓偺傛偆偵側傝傑偟偨丅僨儖僞僔僌儅俙俢俠偵晅偄偰偼傕偆彮偟挷嵏傪宲懕偟傑偡丅

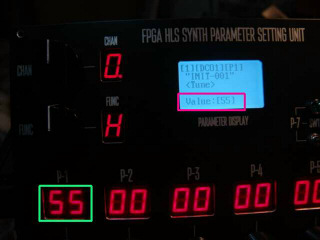

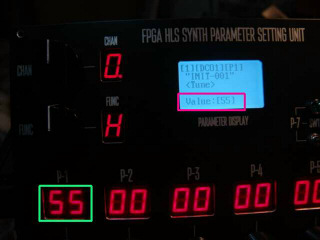

僷儔儊乕僞愝掕婍偺曽傪恑傔傑偡丅僷僱儖嵍懁偺俀偮偺僠儍儞僱儖偲僼傽儞僋僔儑儞偺儘乕僞儕僗僀僢僠偺億僕僔儑儞偑俵俽俹係俁侽偐傜惓偟偔撉傔傞偙偲傪妋擣偟傑偟偨丅

懕偄偰丄塃偵偁傞儌乕僪偺愗傝懼偊僗僀僢僠偱偡丅偙傟偼摦嶌晄椙偱丄撉傔偰偄傑偣傫丅俹俉丏侾偲俉丏俀傪巊梡偟丄係偮偺億僕僔儑儞偑撉傔傞偼偢偱偡偑丄忢帪侽侽偱偡丅俵俽俹係俁侽俥俆俆俀俋偺俹俉偼侽乣俀偺俁價僢僩偱丄俉丏侾偲俉丏俀偺傒僐僱僋僞偵愙懕偝傟偰偄傑偡丅僨僶僢僈偱俹俉偺惂屼儗僕僗僞傪妋擣偟傑偟偨偑丄擖椡億乕僩偵愝掕偝傟偰偍傝丄億乕僩儅僢僺儞僌傕柍偔丄彮側偔偲傕儀乕僗儃乕僪傑偱僗僀僢僠怣崋偑峴偭偰偄傞偙偲傪妋擣偟傑偟偨丅晄嬶崌偺尨場偼晄柧偱偡丅

俀寧俀侾擔

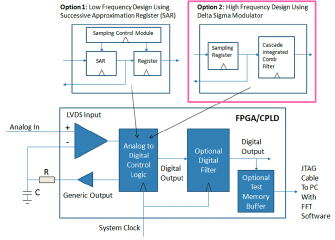

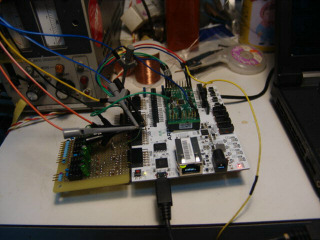

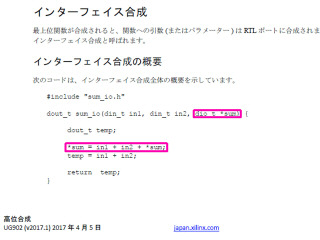

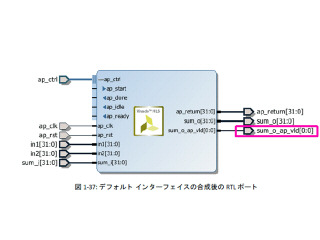

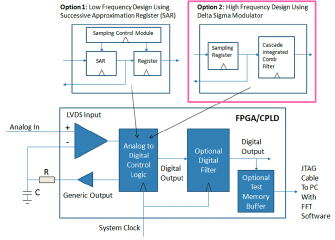

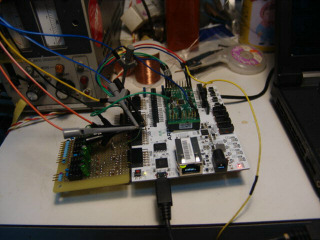

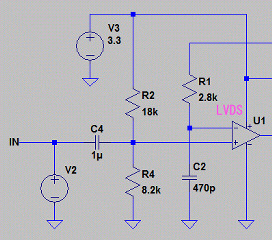

俴倎倲倲倝們倕偺帒椏乮俹俢俥乯偵俠俹俴俢乛俥俹俧俙偵僨儖僞僔僌儅俙俢俠傪幚憰偡傞忣曬偑偁傝傑偟偨丅僐儞僷儗乕僞偺戙懼偊偲偟偰俴倁俢俽儗僔乕僶傪巊偭偰偄傑偡丅

忋婰偲摨偠崅懍僐儞僷儗乕僞俴俿侾俈俀侽偱僔儈儏儗乕僔儑儞偟偰傒傑偡丅惓偟偔摦嶌偟偰偄傑偡丅僐儞僷儗乕僞偺戙傢傝偵俴倁俢俽儗僔乕僶偑巊偊傟偽丄奜晅偗晹昳俠俼丄侾屄偮偯偱僨儖僞僔僌儅俙俢俠偑幚憰偱偒傑偡丅

俴倁俢俽儗僔乕僶傪婰弎偡傞曽朄傪挷傋傑偡丅偼偠傔偵惂栺僼傽僀儖偱偡丅偙偙偵俴倁俢俽丵俁俁偼巊梡偱偒側偄偲偺忣曬偑偁傝傑偡丅倁俠俠俷偼俁丏俁倁偺傑傑丄俴倁俢俽丵俀俆傪巊梡偡傞傛偆偱偡丅儗僔乕僶偺擖椡偑摨憡揹埑亄嵎摦揹埑乛俀亙倁俠俠俷亄侽丏俀偺斖埻側傜椙偄偲偄偆偙偲偱偡丅傕偪傠傫丄恾拞偺僞乕儈僱僞偼庢傝晅偗傑偣傫丅

倃倃倃丏倶倓們偺婰弎偱偡丅

set_property -dict {PACKAGE_PIN xx IOSTANDARD LVDS_25} [get_ports xxx_in1_p]

set_property -dict {PACKAGE_PIN xx IOSTANDARD LVDS_25} [get_ports xxx_in1_n]

師偵倁倕倰倝倢倧倗偺儘僕僢僋撪偵俴倁俢俽偺儗僔乕僶傪婰弎偡傞曽朄偑偙偙偵偁傝傑偟偨丅

module xxx(

.

.

// 儌僕儏乕儖偺擖弌椡怣崋偺婰弎

input xxx_in1_p, // 嵎摦僾儔僗擖椡

input xxx_in1_n, // 嵎摦儅僀僫僗椡

output xxx_out_q1, // 俢亅俥俥偺俻弌椡

.

.

);

// 俴倁俢俽擖椡僶僢僼傽偺婰弎

IBUFDS ibuf_din (.O(xxx_in1),.I(xxx_in1_p),.IB(xxx_in1_n));

俀寧俀俁擔

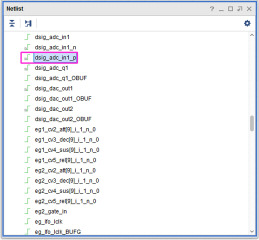

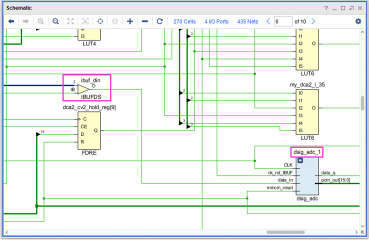

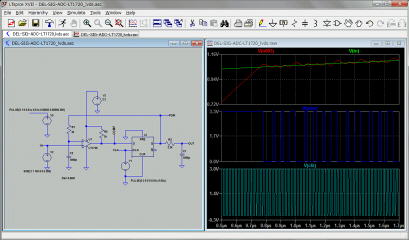

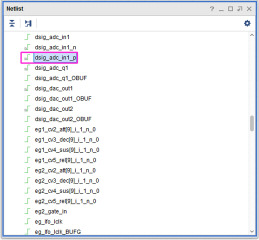

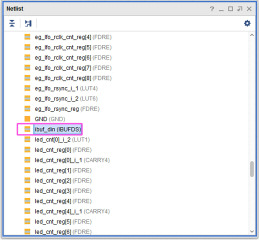

忋婰偺愝掕偱僀儞僾儕偟偰傒傑偡丅俬俛倀俥俢俽乮嵎摦儗僔乕僶乯偑偪傖傫偲巊傢傟偰偄傞偐夞楬恾偱妋擣偟傑偡丅惓偟偔丄俬俛倀俥俢俽偑巊傢傟丄僨儖僞僔僌儅俙俢俠偵愙懕偝傟偰偄傑偡丅

懕偄偰丄僨僶僀僗恾偱偡丅嵎摦擖椡偺僺儞偼俤侾俆偲俤侾俇偱偡偑丄俤侾俆偺僷僢僪偺拞偵偁傞嵎摦儗僔乕僶偑巊傢傟偰偄傑偡丅嵎摦側偺偱懳徧偺埵抲偵偁傞偺偐偲巚偄傑偟偨偑丄俤侾俆偺曽偵曃偭偰偄傑偟偨丅攝慄挿偺堘偄偼栤戣側傜側偄偔傜偄彫偝偄偺偱偟傚偆丅

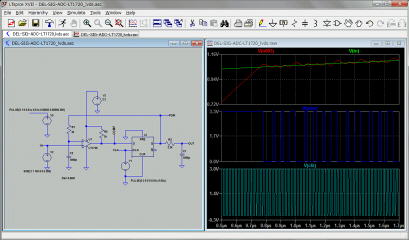

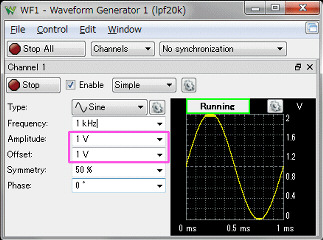

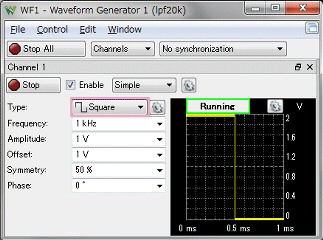

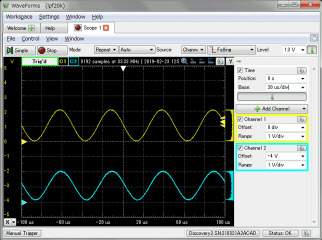

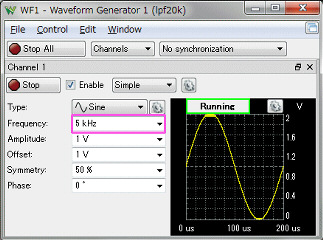

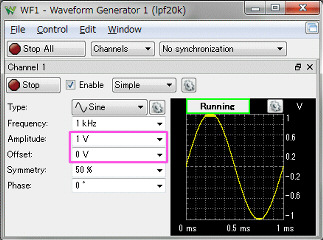

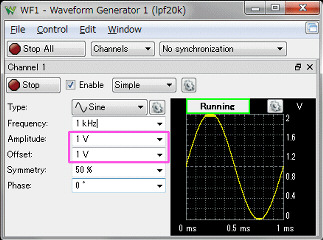

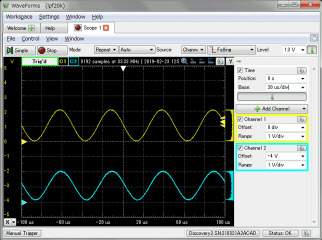

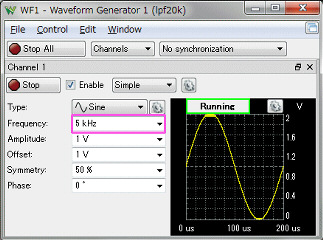

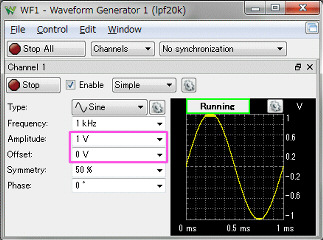

偲傝偁偊偢丄侾僠儍儞僱儖偺傒偱摦嶌妋擣偟傑偡丅奜晹夞楬傪彮偟廋惓偟傑偡丅僨儖僞僔僌儅俙俢俠偺僒儞僾儕儞僌廃攇悢偼侾侽侽俵俫倸偱偡丅

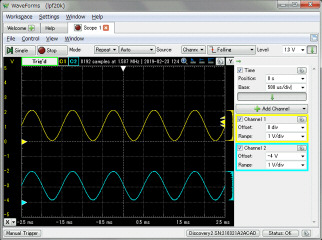

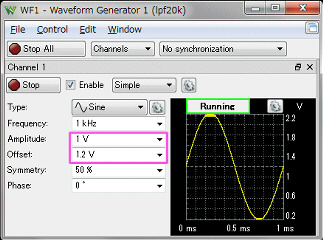

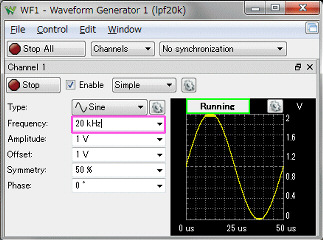

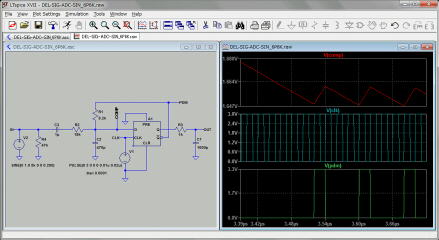

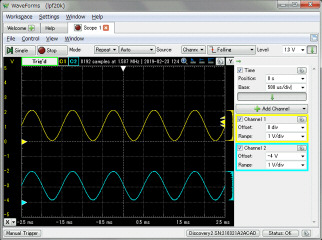

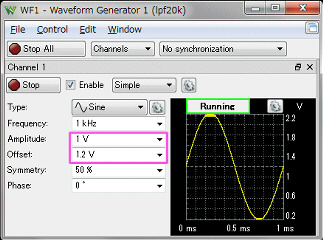

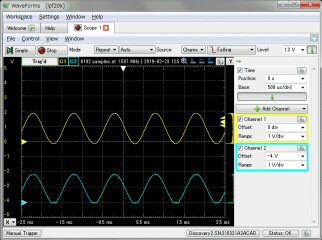

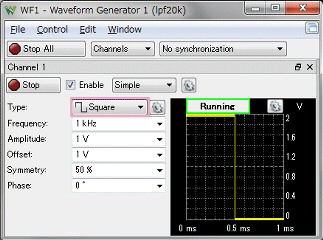

偼偠傔偵丄俽俬俶攇丄侾俲俫倸丄怳暆侾倁丄僆僼僙僢僩侾倁偱偡丅忋丗僨儖僞僔僌儅擖椡丄壓丗俹俢俵偺傑傑弌椡偟偰僷僢僔僽僼傿儖僞愙懕丅惓偟偔丄俥俹俧俙偱侾價僢僩偺俹俢俵偵曄姺偱偒偰偄傞偙傪妋擣偟傑偟偨丅

擖椡偺揹埑斖埻傪妋擣偟傑偡丅俽俬俶攇丄侾俲俫倸丄怳暆侾倁丄僆僼僙僢僩侾丏俀倁偱偡丅忋丗僨儖僞僔僌儅擖椡丄壓丗俹俢俵偺傑傑弌椡偟偰僷僢僔僽僼傿儖僞愙懕丅忋懁偺捈慄惈偑埆偔側偭偰偄傑偡丅

懕偄偰丄俽俬俶攇丄侾俲俫倸丄怳暆侾倁丄僆僼僙僢僩侽丏俉倁偱偡丅忋丗僨儖僞僔僌儅擖椡丄壓丗俹俢俵偺傑傑弌椡偟偰僷僢僔僽僼傿儖僞愙懕丅壓懁偱僋儕僢僾偟偰偄傑偡丅偙偺偙偲偐傜丄擖椡揹埑偼僆僼僙僢僩侾倁丄怳暆侾倁偔傜偄偑擖椡斖埻偺傛偆偱偡丅

揹埑斖埻偑暘偐偭偨偲偙傠偱丄曽宍攇傪擖椡偟偰傒傑偡丅侾俲俫倸丄怳暆侾倁丄僆僼僙僢僩侾倁偱偡丅壓丗僨儖僞僔僌儅擖椡丄忋丗俹俢俵偺傑傑弌椡偟偰僷僢僔僽僼傿儖僞愙懕丅曽宍攇傕惓偟偔弌椡偝傟偰偄傑偡丅

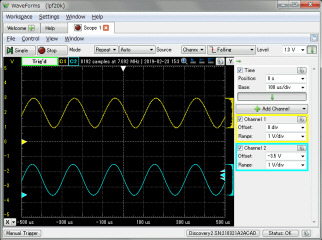

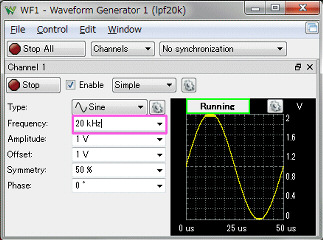

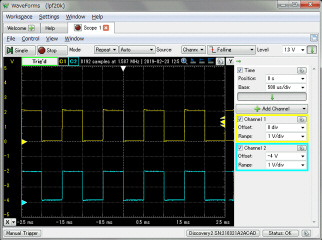

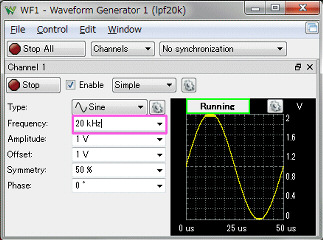

懕偄偰丄廃攇悢傪崅偔偟偰傒傑偡丅俽俬俶攇丄俀侽俲俫倸丄怳暆侾倁丄僆僼僙僢僩侾倁偱偡丅壓丗僨儖僞僔僌儅擖椡丄忋丗俹俢俵偺傑傑弌椡偟偰僷僢僔僽僼傿儖僞愙懕丅惓偟偔弌椡偝傟偰偄傑偡丅

偙偙傑偱丄俹俢俵傪偦偺傑傑弌椡偟偰偄傑偟偨偑丄俥俹俧俙撪偱巊偆偵偼僗僩儗乕僩俹俠俵偵曄姺偡傞昁梫偑偁傝傑偡丅侾俋俀俲俫倸僒儞僾儖偺俹俠俵偵曄姺偟偰傒傑偡丅儘僕僢僋偼娙扨偱丄

侾侽侽俵乛侾俋俀俲俫倸亖俆俀侽丏俉俁側偺偱丄僨儖僞僔僌儅偺俆俀侾僒儞僾儖娫傪傾僢僾僟僂儞僇僂儞僞偱僇僂儞僩偟傑偡丅拞娫抣偱弶婜壔偟丄俹俢俵偑侾側傜傾僢僾丄侽側傜僟僂儞僇僂儞僩偟偰丄侾僒儞僾儖偺侾侽價僢僩俹俠俵偲偟傑偡丅柍壒偺帪丄嵟崅懍偱侽偲侾偑岎斣偟傑偡丅偙偺帪傾僢僾僟僂儞僇僂儞僞偺抣偼弶婜抣偵栠傝丄拞娫抣偵側傝傑偡丅俆俀侾亖侾侽價僢僩庛偱偡丅侾師僨儖僞僔僌儅偱侾侽侽俵俫倸偱僒儞僾儕儞僌偟偰傕侾俋俀俲俫倸偺俹俠俵偵曄姺偡傞偲侾侽價僢僩偺掅偄暘夝擻偲側傝傑偡丅

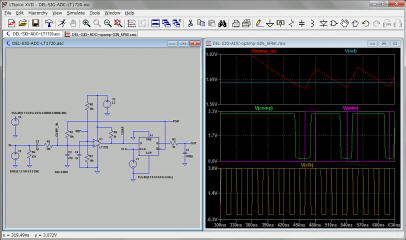

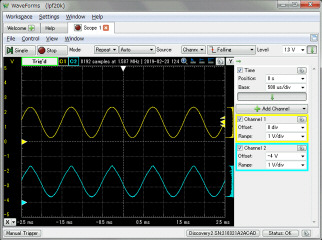

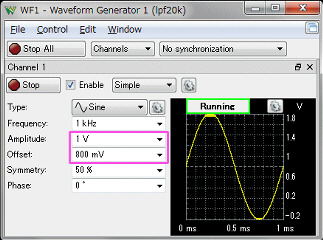

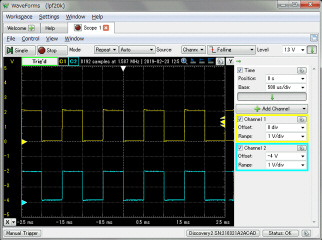

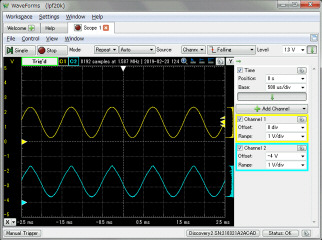

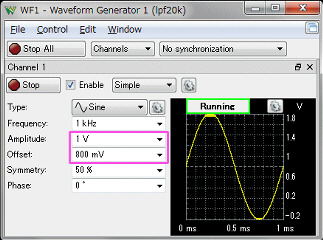

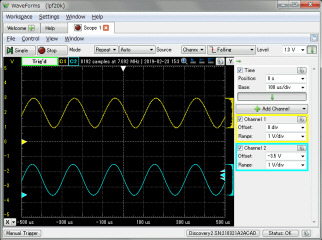

俽俬俶攇丄俆俲俫倸丄怳暆侾倁丄僆僼僙僢僩侾倁偱偡丅壓丗僨儖僞僔僌儅擖椡丄忋丗俹俢俵傪侾俋俀俲俫倸僒儞僾儖偺俹俠俵偵曄姺偟偰偐傜丄僨儖僞僔僌儅俢俙俠偱弌椡偟偰忋婰偲摨偠僷僢僔僽僼傿儖僞愙懕丅惓偟偔丄俹俠俵偵曄姺偝傟偰偄傑偡丅偙偺傾僫儘僌擖椡偼媽俢俠俷乮俉價僢僩乯傪愙懕偡傞梊掕側偺偱俋價僢僩偁傟偽廫暘偱偡丅

廃攇悢傪崅偔偟偰傒傑偡丅俽俬俶攇丄俀侽俲俫倸丄怳暆侾倁丄僆僼僙僢僩侾倁偱偡丅壓丗僨儖僞僔僌儅擖椡丄忋丗俹俢俵傪俹俠俵偵曄姺偟偰僨儖僞僔僌儅俢俙俠偱弌椡偟偰僷僢僔僽僼傿儖僞愙懕丅帪娫幉傪奼戝偟偰侾俋俀俲俫倸偺僒儞僾儖傪妋擣偟傑偡丅惓偟偔丄侾俋俀俲俫倸偱弌椡偝傟偰傑偡丅

懕偄偰丄曽宍攇偱偡丅俆俲俫倸丄怳暆侾倁丄僆僼僙僢僩侾倁偱偡丅壓丗僨儖僞僔僌儅擖椡丄忋丗俹俢俵傪俹俠俵偵曄姺偟偰僨儖僞僔僌儅俢俙俠偱弌椡偟偰僷僢僔僽僼傿儖僞愙懕丅栤戣柍偄偱偡丅

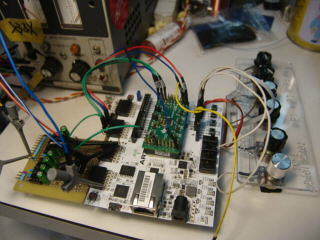

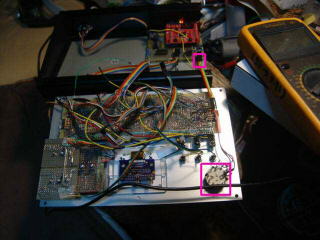

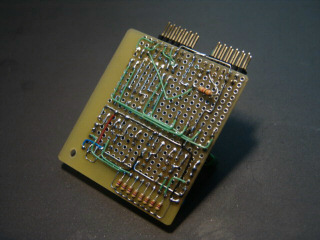

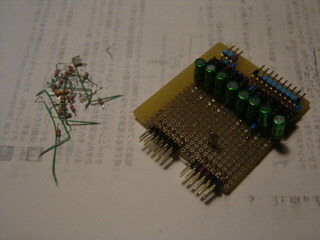

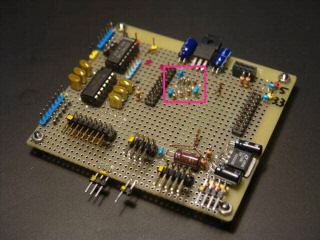

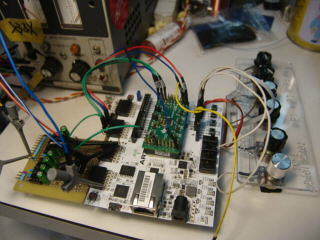

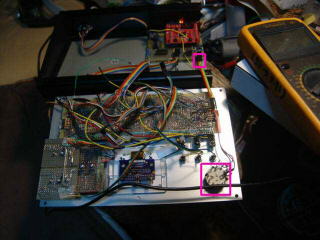

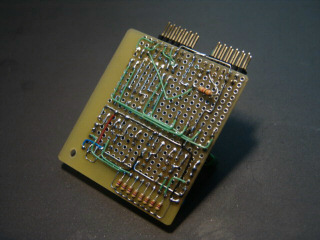

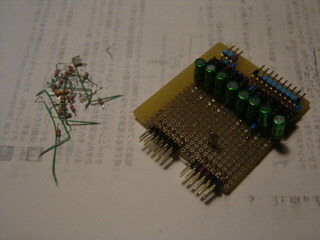

僨儖僞僔僌儅俙俢俠偑摦嶌偑妋擣偱偒偨偺偱丄奜晹夞楬傪俉們倛梡偵廋惓偟傑偡丅慜抜偺儃儖僥乕僕僼僅儘傾偲僇僢僾儕儞僌僐儞僨儞僒傪巆偟偰丄掞峈偲僐儞僨儞僒傪庢傝奜偟傑偟偨丅

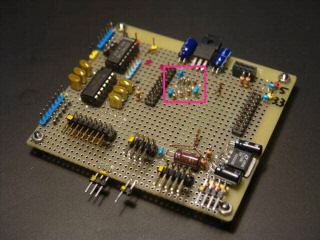

僆僼僙僢僩掞峈傪捛壛偟偰丄僆僼僙僢僩柍偟偱怣崋偑擖椡偱偒傞傛偆偵偟傑偡丅埲壓偼俴倲倱倫倝們倕偱嶌惉偟偨夞楬恾偱偡丅慜抜偺儃儖僥乕僕僼僅儘傾偼徣棯偟偰偄傑偡丅

僨儖僞僔僌儅俙俢俠傪俉僠儍儞僱儖偵偡傞偵偼丄嵎摦擖椡侾俇僺儞丄弌椡億乕僩俉僺儞偺崌寁俀係僺儞偑昁梫偱偡丅尰忬偺奜晹夞偼俹俵俷俢僐僱僋僞偑俀屄乮侾俇僺儞乯偟偐側偄偺偱丄働乕僽儖偱愙懕偟偰丄侾屄憹傗偟傑偟偨丅

僇僢僾儕儞僌僐儞僨儞僒偲僆僼僙僢僩掞峈傪捛壛偟偨偺偱丄僆僼僙僢僩柍偟偱摦嶌妋擣偟傑偡丅俽俬俶攇丄侾俲俫倸丄怳暆侾倁丄僆僼僙僢僩侽倁偱偡丅壓丗僨儖僞僔僌儅擖椡丄忋丗俹俢俵傪俹俠俵偵曄姺偟偰僨儖僞僔僌儅俢俙俠弌椡偟偰僷僢僔僽僼傿儖僞愙懕丅栤戣柍偄偱偡丅

僉儍僲儞偺儌僶僀儖僾儕儞僞傪偔傟傞偲偺偙偲偱丄戭攝偱憲偭偰傪傕傜偄傑偟偨丅倂倝値俈偱偼惓幃僒億乕僩偟偰偄側偄傛偆偱偡偑丄僱僢僩偵宷偘傞偲帺摦偱僪儔僀僶偑僀儞僗僩乕儖偝傟傑偟偨丅壗夞偐僿僢僪僋儕乕僯儞僌偟偰丄僥僗僩報帤偱偒傑偟偨丅梡巻偼侾枃偯偮庤嵎偟偱偡丅僶僢僥儕傕傑偩惗偒偰偄傞傛偆偱偡丅

俀寧俀係擔

俥俹俧俙

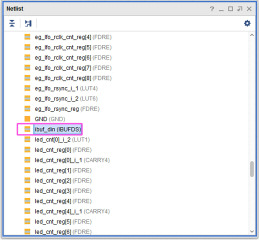

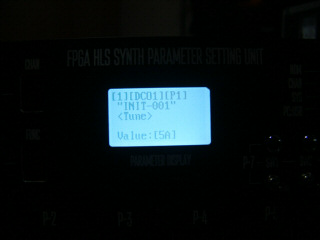

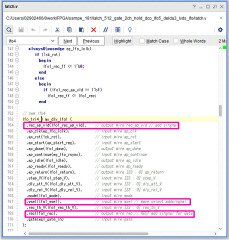

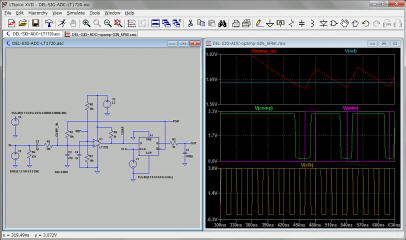

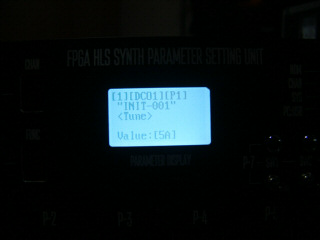

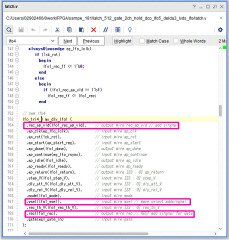

僔儞僙杮懱偺僨儖僞僔僌儅俙俢俠偑摦嶌偟偨偺偱丄僷儔儊乕僞愝掕婍偺曽傪恑傔傑偡丅愭廡丄儌乕僪愝掕儘乕僞儕僗僀僢僠偺億乕僩偑撉傔側偐偭偨晄嬶崌偱偡

偑丄嵞搙妋擣偟偨偲偙傠丄栤戣側偔摦嶌偟傑偟偨丅掆巭拞偱傕俠俠俽偺儗僕僗僞僂僀儞僪偑惓偟偔峏怴偝傟側偄偙偲偑偁傞傛偆偱丄楢懕峏怴儃僞儞偺戙傢傝偵丄僽儗僀僋億

僀儞僩傪偐偗偰幚峴屻偵僽儗僀僋偡傟偽丄儗僕僗僞僂僀儞僪偑峏怴偝傟傑偟偨丅

俠倷倗倵倝値忋偱僨僶僢僌偟偰嶌惉偟偨丄俴俠俢昞帵偺僐乕僪傕俵俽俹係俁侽偵堏峴偟偰丄幚婡偱婎杮摦嶌偺妋擣偟傑偟偨丅

俈僙僌偵昞帵偡傞傾儖僼傽儀僢僩偺乫俻乫偲乫俋乫偺僼僅儞僩傪曄峏偟傑偟偨丅乭俻倀俬俿丏亅亖丂侾俀俁俋乭偲昞帵偝偣偰傒傑偟偨丅

儘乕僞儕僄儞僐乕僟抣傪俈僙僌偲俴俠俢偵昞帵偝偣偰傒傑偡丅儘乕僞儕僄儞僐乕僟抣偼僾僢僔儏儃僞儞傪墴偟側偑傜夞揮偝偣傞偲丄亄亅侽倶侾侽偱憗夞偟偱偒傑偡丅儘乕僞儕僄儞僐乕僟偺僾僢僔儏儃僞儞偼暿偺巊偄曽傪梊掕偟偰偄傑偡丅僾僢僔儏儃僞儞偺俀廳墴偟乮偨偲偊偽俹俇傪墴偟側偑傜俹侾傪墴偡偲侾僠儍儞僱儖傪敪壒偡傞丄俹俆傪墴偟側偑傜俹俇傪墴偡偲壒怓柤偺僄僨傿僢僩儌乕僪偵擖傞側偳乯偱僐儅儞僪傪慗堏偝偣傞梊掕偱偡丅

俁寧俀擔

僷儔儊乕僞愝掕婍偺儊僀儞儖乕僾撪偺僾儘僌儔儉傪嶌惉偟傑偡丅儘乕僞儕僄儞僐乕僟丄僩僌儖僗僀僢僠偺抣傪昞帵偟偰丄俥俹俧俙杮懱偵憲怣偡傞晹暘偱偡丅愭廡傕傜偭偨僾儕儞僞偵僾儘僌儔儉偺僗働儖僩儞傪報嶞偟偰僼儘乕傪妋擣偟傑偡丅峫偊偑傑偲傑傜側偄帪偼報嶞偡傞偲嶌嬈偑恑傒傗偡偄偱偡丅

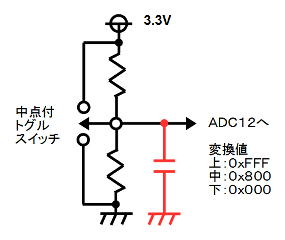

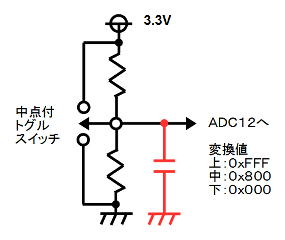

僷儔儊乕僞俈偼俷俶乛俷俥俥偺僩僌儖僗僀僢僠偑俁屄偁傝傑偡丅僗僀僢僠偼拞揰晅偒偱丄俵俽俹係俁侽偵撪憼偺俙俢俠侾俀傪巊偭偰抣傪撉傒崬傒傑偡丅僨僶僢僌拞偵僗僀僢僠傪憖嶌偟側偔偰傕丄恾偟側偄抣偵側傞帪偑偁傝傑偡丅壓偼僗僀僢僠偺憖嶌傪峴傢側偄偺偵丄彑庤偵僗僀僢僠偁傝偺張棟偱僽儗僀僋偟偨偲偙傠偱偡丅僷僱儖傗儘乕僞儕僄儞僐乕僟傪怗傞偲岆摦嶌偡傞応崌偑懡偄偱偡丅

僩僌儖僗僀僢僠偺夞楬偼嵍恾偱丄僐儞僨儞僒傪捛壛偟偰僲僀僘懳嶔偟傑偟偨丅

俁寧俁擔

擮偺偨傔丄俙俢俠侾俀偺僒儞僾儕儞僌廃攇悢傕掅偔愝掕偟傑偟偨丅俙俢俠偼僩僌儖僗僀僢僠偺抣傪撉傓偩偗側偺偱丄僋儘僢僋偺暘廃傪嵟戝偟傑偟偨丅偝傜偵丄忋壓敾掕偺鑷抣傪峀偘傑偟偨丅偙偺廡枛偺俀擔娫傪巊偭偰僾儘僌儔儉乛僨僶僢僌偟傑偟偨偑丄巚偭偰偄偨傛傝擄偟偔儊僀儞儖乕僾偺張棟偼姰惉偟傑偣傫偱偟偨丅

俁寧俇擔

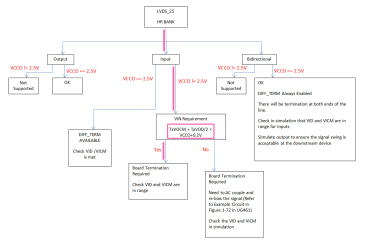

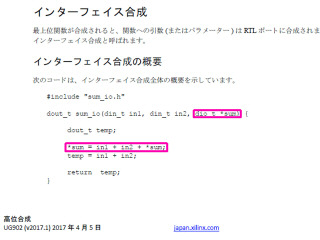

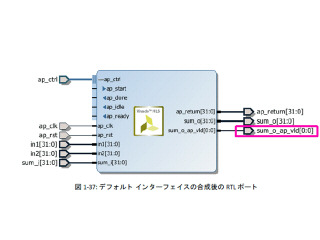

彮偟慜偵俥俹俧俙僔儞僙杮懱偺俴俥俷傪廋惓偟傑偟偨丅俤俧偺側偳偵巊偊傞傛偆偵僎乕僩愱梡偺俹倂攇傪捛壛偟傑偟偨丅偙偺怣崋偼俫俴俽偺億僀儞僞搉偟偱婰弎偟偰偁傝丄俬俹傪慻傒崬傫偩偲偙傠丄倰倕們丵倎倫丵倴倢倓偲偄偆惂屼怣崋偑憹偊偰偄傑偟偨丅僓僀儕儞僋僗偺崅埵崌惉偺僪僉儏儊儞僩偵崱夞偲摨偠億僀儞僞搉偟偺椺偑偁傝傑偟偨丅

偙偺椺偱傕丄倶倶偵懳偟偰倶倶丵倎倫丵倴倢倓怣崋偑捛壛偝傟傑偡丅偙傟偼倶倶怣崋偑桳岠偱偁傞偙偲傪帵偟傑偡丅

僞僀儈儞僌恾偱妋擣偡傞偲丄倶倶怣崋傪偙偺倶倶丵倎倫丵倴倢倓怣崋偱儔僢僠偡傟偽椙偝偦偆偱偡丅

憗懍丄儔僢僠晹傪捛壛偟偰丄崌惉丄僀儞僾儕偟偰傒傑偟偨丅幚婡偑側偄偺偱摦嶌妋擣偼崱廡枛偵峴偄傑偡丅

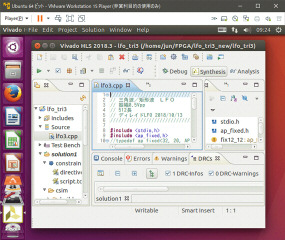

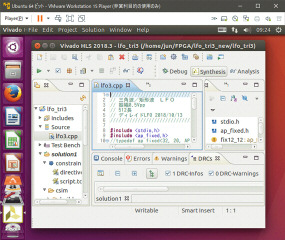

倁倝倴倎倓倧偺怺偄僨傿儗僋僩儕峔憿傗丄懠偺僆乕僾儞俬俹偺僣乕儖傪峫椂偡傞偲丄奐敪娐嫬偼俴倝値倳倶偺曽偑偄偄偱偡丅埲壓丄倁倝倴倎倓倧傪倁俵倵倎倰倕 俹倢倎倷倕倰忋偺倀倐倳値倲倳 侾俇丏侽係 俴俿俽偱俫俴俽傪摦嶌偝偨偲偙傠偱偡丅偙偙傪嶲峫偵夛幮偺倂倝値侾侽偺俹俠偱摦嶌妋擣偟傑偟偨丅偨偩偟丄僜乕僗僐乕僪拞偺擔杮岅僐儊儞僩傪暥帤壔偗柍偟偱昞帵偡傞偵偼倀俿俥亅俉偵曄姺偡傞昁梫偑偁傝傑偡丅倕倣倎們倎倱偑偁傟偽娙扨偵暥帤僐乕僪偺曄姺偑偱偒傑偡丅

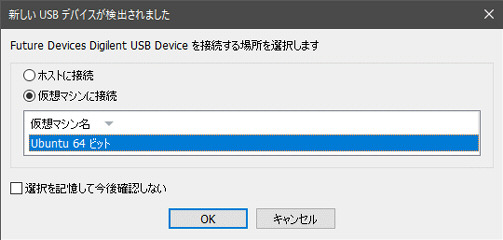

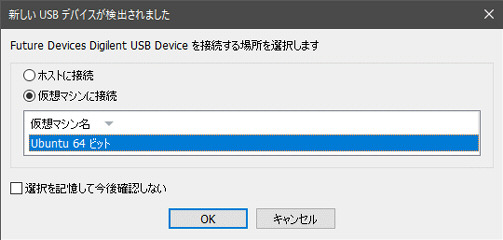

寽擮帠崁偺僟僂儞儘乕僪梡偺倀俽俛僪儔僀僶偼俙俼俿倄儃乕僪傪愙懕偡傞偲丄埲壓偺傛偆偵億僢僾傾僢僾偑弌傑偡丅

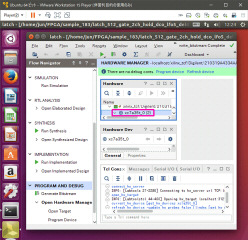

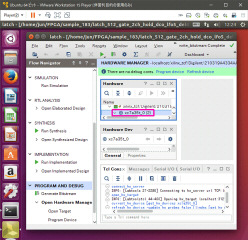

倀俽俛僪儔僀僶傪倁俵倵倎倰倕懁偵愗傝懼偊偨屻丄倁倝倴倎倓倧偺僴乕僪僂僃傾儅僱乕僕儍傪婲摦偡傞偲俙俼俿倄儃乕僪偑擣幆偝傟傑偟偨丅俀們倛俥俹俧俙僔儞僙偺儘僕僢僋傪僟僂儞儘乕僪偱偒傞偙偲傪妋擣偟傑偟偨丅懠偵俽俢俲偲俢倧們俶倴倝傕摦嶌偟傑偟偨丅