TK80/BSの

シンセシステムを復活/拡張したい〜

その36

FPAGシンセ、パラメータ設定器の作製

2019年

2019年

3月9日

ヤフーのポイントの期限が来るので、ヤフオクで購入したトグルスイッチです。中点付き6Pです。8chアナログ/デジタルシンセのVCAの改造に使う予定です。

2個のレバーの動きが悪いので、分解して組み立て直しました。直りました。

3月10日

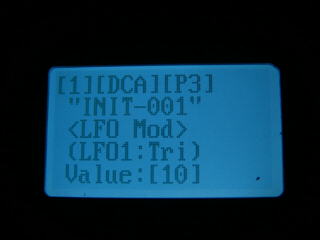

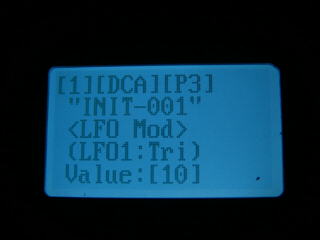

先週からの続きです。パラメータ設定器の表示部の基本部分がほぼ完成ました。ロータリスイッチの設定、ロータリエンコーダとトグルスイッチのパラメータを7セグLEDとLCDに表示するメインループ部です。まだ、表示のみで、FPGAにデータ送信はしていません。

ローチパッド上のMSP430の電源はデバッガ側と切り離したため、デバッガ側の電源が入っていないと、常時リセットが掛かって起動しません。いちいちボード上のショートバーを設定するのは面倒なので、デバッガ信号のSBW_TST、SBW_RSTを上記の6Pスイッチで切り離なせるようにしました。これでデバッガ側の電源入っていなくても起動するようになりました。

久しぶりのFPGAシンセの本体です。ゲート用信号を追加したLFOの動作確認を行う予定でしたが、波形変換ロジックの動作か未確認だったため、先にこれを確認します。

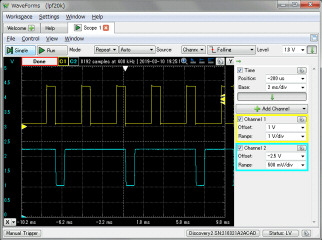

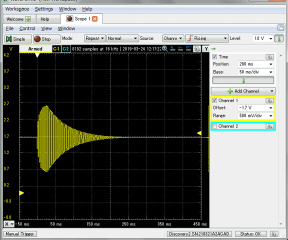

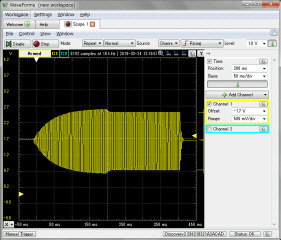

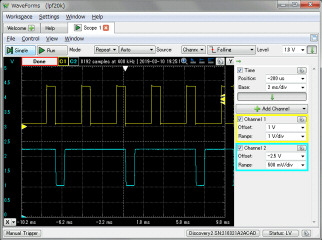

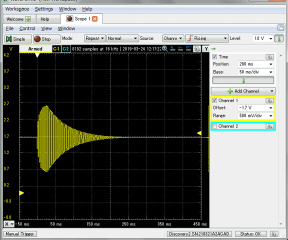

波形変換ロジックはDDS−DCOが出力した512倍クロックから、ノコギリ波とPW、基本周波数の1/2と2倍のデューティ50%、または25%の矩形波を生成します。初めにデューティ50%です。左下がPW波、上が2倍の矩形波です。右下がPW波、上が1/2倍の矩形波です。また、PW波は閾値によってデューティが変わることを確認しました。

続いて、デューティ25%です。左下がPW波、上が2倍の矩形波です。右下がPW波、上が1/2倍の矩形波です。

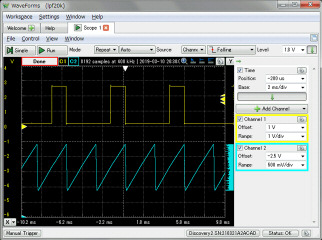

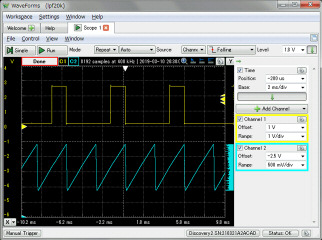

続いてノコギリ波とデューティ25%の矩形波です。

3月15日

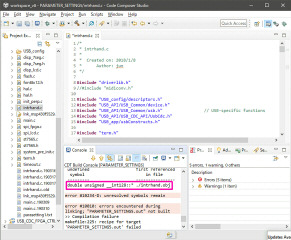

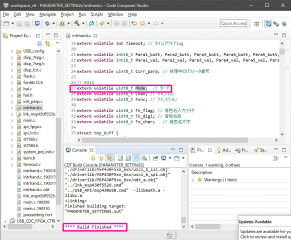

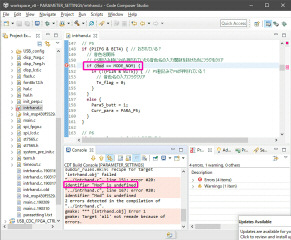

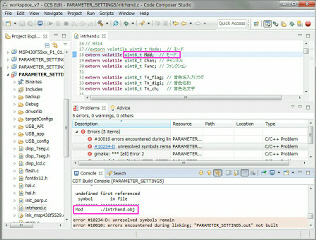

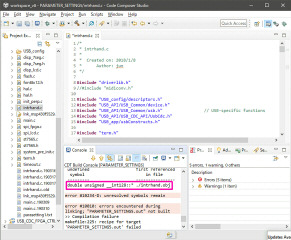

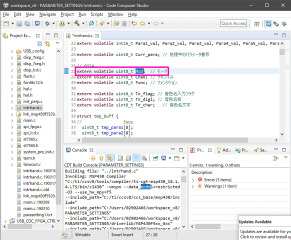

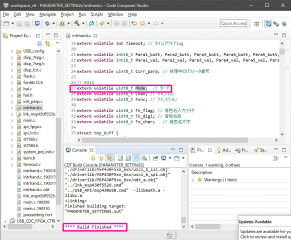

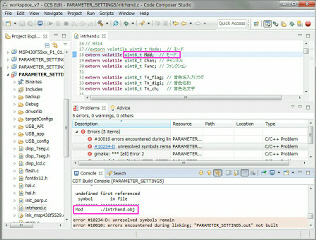

会社のPCにはCCS

のVer.8.3が入っています。パラメータ設定器のプログラムをビルドしてみました。リンク時に割り込みハンドラ内に解決できないシンボルがあ

るというエラーが出ます。プログラムを作っていると、良く遭遇するエラーですが、エラーのシンボル名が”__int128::*”と表示されていて、コード内にこのシンボルは無く、エラーを探すこともできないため、非常に困りました。

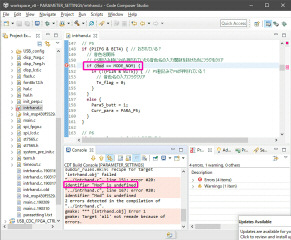

コードを少しづつ削って原因のシンボルを見つけました。問題のシンボルは割り込みハンドラの”Mod”でした。メインプログラムで”Mode”と宣言されていて、割り込みハンドラの上部で間違えて”extern Mod”となっていました。

これを修正したところ、正常にビルドできました。

因みに、上部で”extern Mode”とし、プログラム内で”Mod”を使った時は”Mod”がエラー表示されます。

3月16日

上記と同じプロジェクトをガレージのCCSのVer.7.3でビルドすると、普通に”Mod”がエラーと表示されます。Ver.8.3の不具合のようです。

3月17日

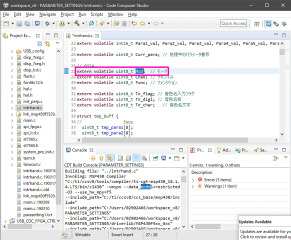

ロータリエンコーダのプッシュボタンの2重押しで、チャンネルのパラメータに付いている8文字長の音色名をエディットするプログラムを作成します。6個あるロータリエンコーダの内、右側のP5を押しながらP6を押すとエディットモードに入り、P6を押しながらP5を押すとエディットモードを抜けます。エディット自体の操作もP5とP6のエンコーダを使います。P5で桁を選択し、P6で文字をインクリメント、デクリメントして選択する方法です。エディットは面倒で時間も掛かりますが、フルキーボードが無い時には、この方法しかありません。音色名は7セグLEDに表示するため、使用できる文字を0〜9とアルファベットのA〜Z、記号−、.、=とスペースに限定しました。この場合、文字コードが連続しないため、プログラム内で次に使える文字までスキップさせる必要があります。

土曜の午後と日曜の丸1日使って、音色名エディットが動くようになりました(笑)。画像をクリックすると、64Mバイトの動画ダウンロードします。7セグが明るいので見にくいですが、LCDの2行目にも音色名を表示しています。操作感はエンコーダのクリックが軽いため、プッシュボタンの2重押し時に1クリック分動いてしまうことがあり、いまいちです。使用しているエンコーダは1回転あたり、50パルスですが、半分の25パルスの方が良かったです。また、変更対象の桁マーカに’.’を使っていますが、文字としても’.’が入力できるので、分別できません。

3月23日

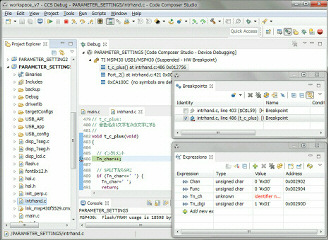

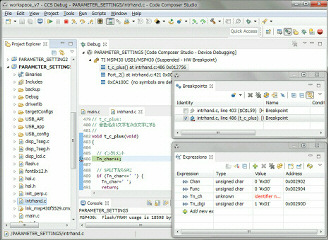

パラメータ設定器の続きです。ユーザインターフェースの細かい不具合を修正し、RAM上の8ch分のパラメータ(512バイト)をフラッシュにセーブするプログラム、逆にフラッシュからRAMにリストアするプログラムを追加しました。また、電源投入時にP1のロータリエンコーダが押されていた場合はフラッシュから8ch分のパラメータをRAMにコピーするのをスキップできるようにしました。これで、RAMに初期化された値を残すか、フラッシュにセーブした値を上書きするか選択できるようになりました。

3月24日

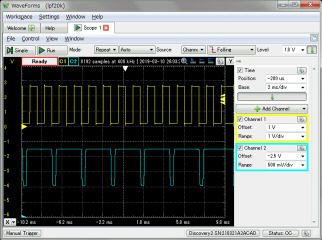

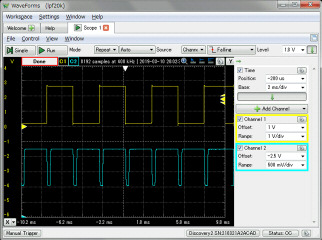

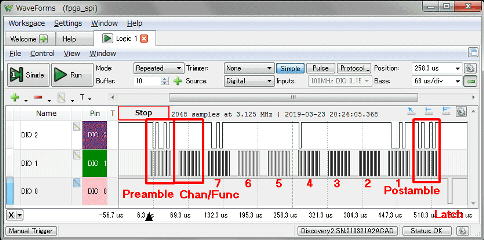

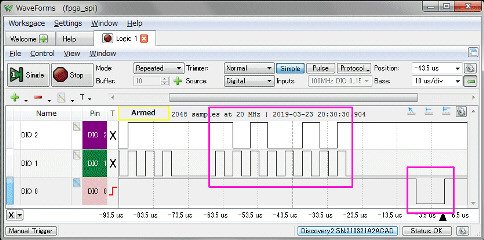

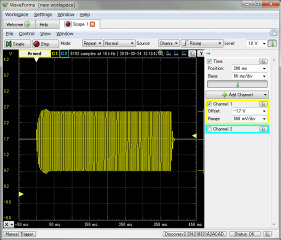

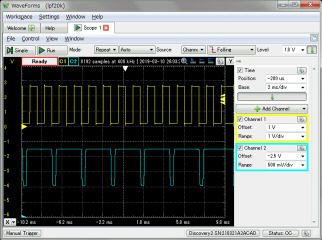

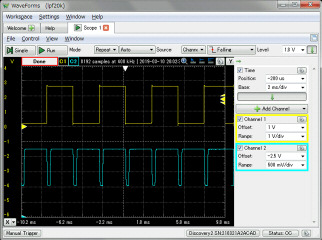

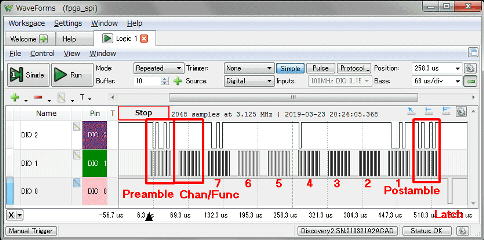

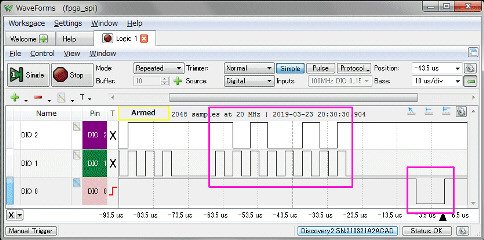

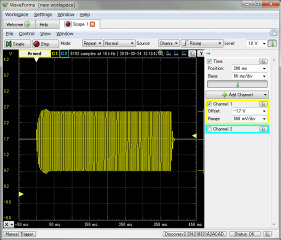

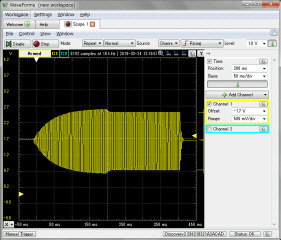

パラメータ設定器からSPIでFPGAにパラメータを送信するプログラムを追加します。電源投入時は8ch分の8ファンクションのパラメータ(8*8*7)=448バイト)を送信し、その後、パラメータが変更されるたびにチャンネルとファンクションで設定されるパラメータ(P7〜P1)の7バイトを送信します。実際に送信するデータは先頭にプリアンブル、チャンネル/ファンクションコード、後ろにポストアンブルの3バイトを足した合計10バイトです。その後、SPIとは別信号のラッチパルスを送って、FPGA内のSPIロジックからパラメータ記憶用のレジスタバンクに書き込み指示します。下はSPI信号とラッチパルスの波形です。HCT14を介して接続しているので信号は反転しています。

SPIのクロックはパラメータ設定器とFPGAシンセ間をケーブル接続するのて、LCDのSPIより落として、約200KHzに設定しました。10バイト+ラッチパルスを約550uSecで送信します。

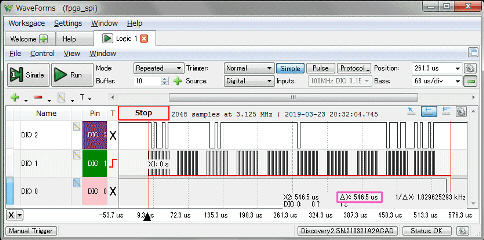

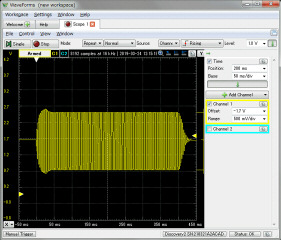

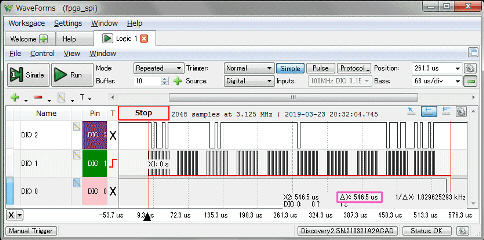

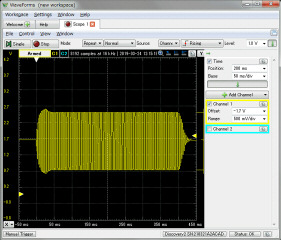

後ろ側のラッチパルス部分を拡大してみます。ポストアンブルは0x5aです。ラッチパルスはSPIとは非同期のGPOでソフトウェアでタイミングとって出力します。

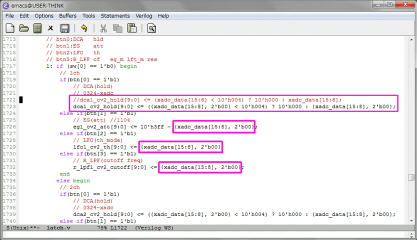

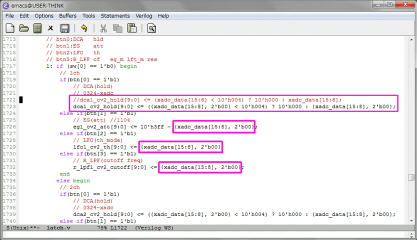

現在、FPGA本体側は2chのシンセサイザが実装されています。パラメータはXADC(FPGA内の12ビットADC)から入力した4個のアナログ値をボード上のスライドスイッチとプッシュボタンで振り分けています。パラメータ設定器から設定できるように準備します。

XADCは12ビットですがノイズ分の2ビットを落として10ビットで使っています。パラメータ設定器からのデータは8ビットなので、10ビットで使用しているXADCのパラメータを8ビットに縮小して動作確認をしました。ただ、この2chシンセサイザは去年の11月に開催されたアナログシンセビルダーズサミットのデモ用の”とあえず動く版”で設定範囲などが最適になっていません。たとえば、EGのリリースがアタックに比べてかなり短いなど、色々と問題があります。パラメータを8ビットに修正した、このロジックを元にして設定範囲を調整します。その後、パラメータ設定器を接続して、パラメータ設定器から設定できるようにします。最終的に8ch化し、ロジックに余裕があればチャンネルあたり、DCOとLFOを2個実装します。設定入力として使用しなくなったXADCはUSB−MIDIパラレル変換器から出力されるベロシティを入力する予定です。ここのブロック図を修正しました。

3月31日

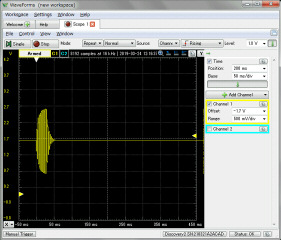

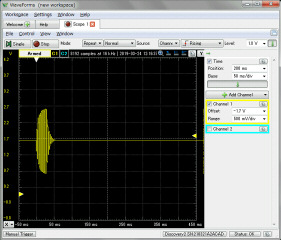

パラメータをすべて10ビットから8ビットへ変更したので、EGの調整範囲の確認を行います。ADSR=0、0、FF、0です。この時エンベロープはゲート信号と同じ矩形になるはずでが、アタックが長く、サスティーンレベルも低いです。

ADSR=0、0、FF、FFです。リリースを最大にしても50mSecくらいしか変化していません。リリースの調整範囲が狭いです。

ADSR=0、0、0、0です。本来は細い矩形になるはずです。アタックが短くなれば改善できそうです。

ADSR=0、FF、0、0です。こちらも、アタックが短くなれば改善できます。

ADSR=FF、0、FF、0です。修正点はアタックの最小時に短く、リリースの調整範囲を大きくして、サスティーンレベルの最大値を合わせます。パラメータは8ビットの整数ですが、EGの各パラメータは整数部12ビット、固定小数点部12ビットです。丁度良い範囲に再調整する必要があります。

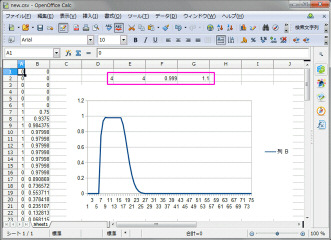

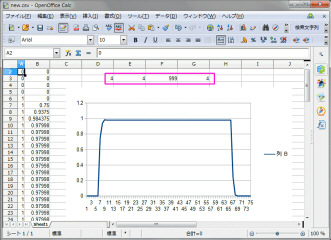

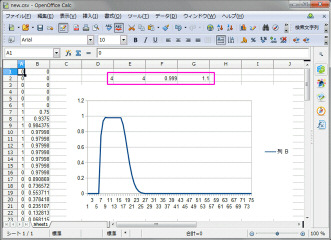

VivadoのHLSに戻ってEGを確認します。ADSR=4.0、4.0、0.999、4.0です。まずまずです。

ADSR=1.1、4.0、0.999、4.0です。アタックは良いようです。

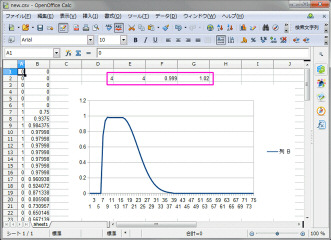

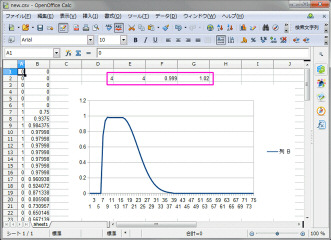

リリースを調整して確認します。1.1にして長くしてみます。ADSR=4.0、4.0、0.999、1.1です。

さらに1.02で、ADSR=4.0、4.0、0.999、1.02です。

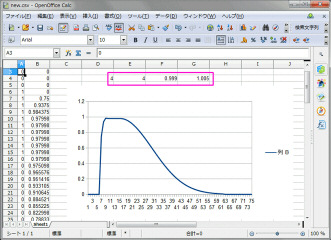

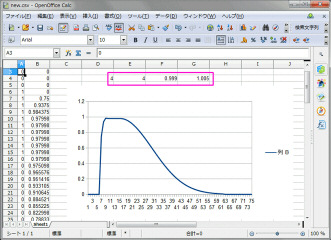

さらに1.005でADSR=4.0、4.0、0.999、1.005です。

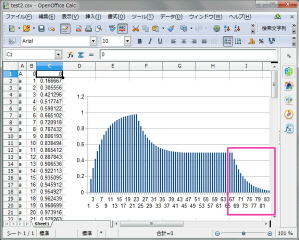

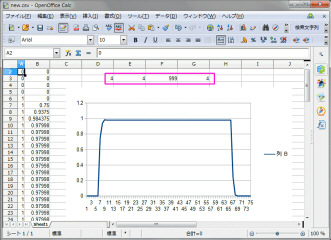

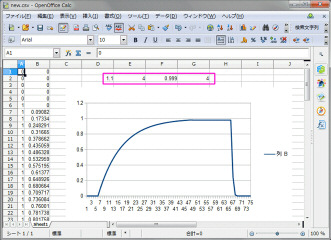

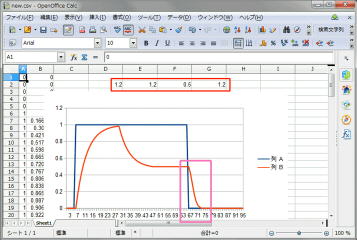

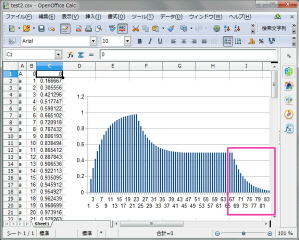

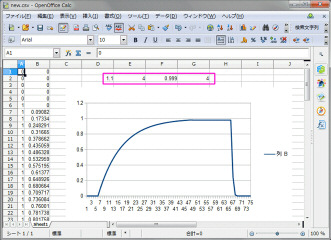

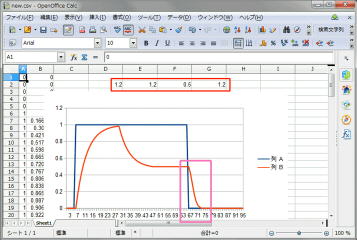

ゲート信号と合わせて、グラフ作成してみます。ADSR=1.2、1.2、0.5、1.2です。アタックとリリースが同じ1.2ですが、6倍くらいの差があります。元々、アタック、ディケイに比べて、リリースが短いことが分かりました。これはパラメータ値を8ビットに変更したのとは無関係な不具合です。

以前にEGの動作確認を行ったときのグラフです。赤枠内を比較すると曲線が違います、以前は正しく動作していたようなので、デグレードしてしまったようです。