TK80/BSの

シンセシステムを復活/拡張したい〜

その40

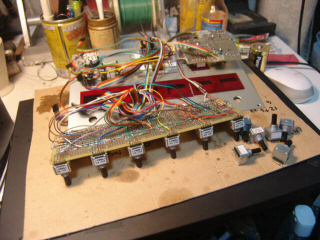

FPAGシンセの8チャンネル化

ケースへの収納

2019年

2019年

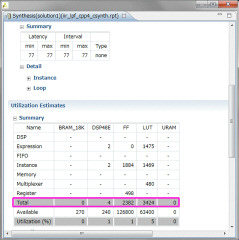

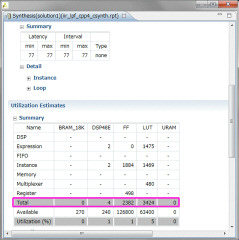

6月26日

HLSで作成したDCFのラダーフィルタiir_lpf_cppはDSPを使う設定で生成したものを組み込むと音が小さくなる不具合が出ました。スライスを減らす目的でDSPを使う設定にしたので、そもそもLUTが減るのか確認してみます。はじめにHLSのレポートを比較してみます。DSPを使わない方です。HLSのレポートではレイテンシが77、DSP使用数4、LUT使用数3424になっています。

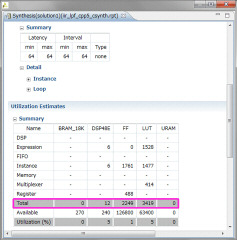

DSPを使う方です。レイテンシが64、DSP使用数12、LUT使用数3419になりました。HLSの段階でDSPを使う設定にしてもLUTはあまり減らないです。当然ですが、シミュレーション結果はどちらも同じです。

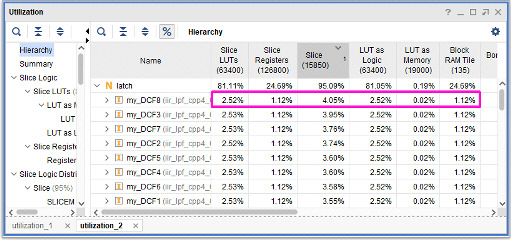

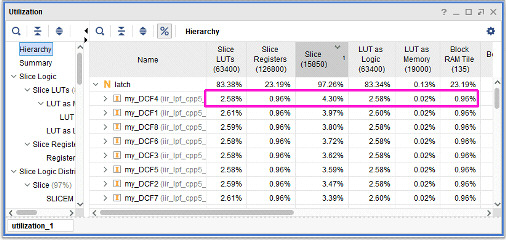

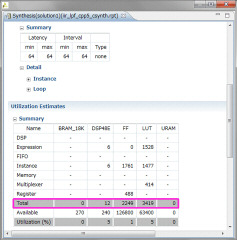

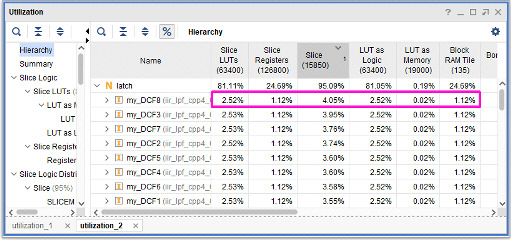

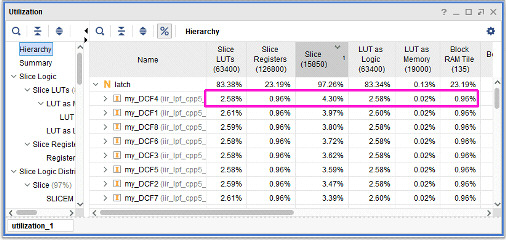

続いて、Vivadoでインプリ後のDSPを使わない方のロジック使用量です。スライスが4.05%(642)です。

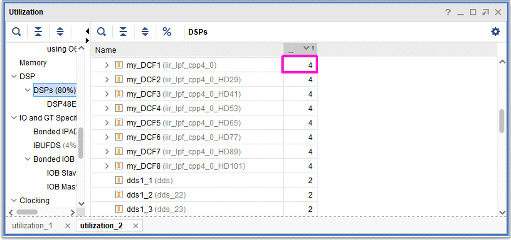

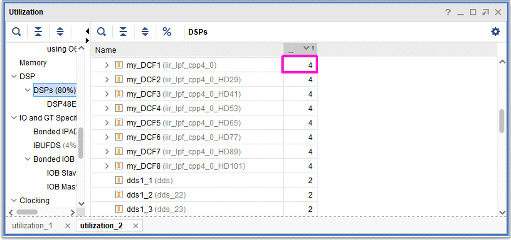

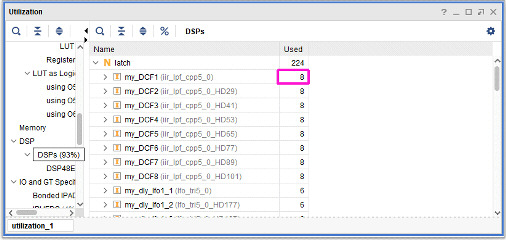

DSPを使わない方のDSPの使用量は4です。

DSPを使う方のインプリ後のロジック使用量です。スライスが4.3%(682)です。

DSPを使う方のDSPの使用量は8です。4つ増えました。インプリ後もDCFではDSPを使う設定にしてもLUTの使用量は減らないようです。LUTが大幅に減らせるのであれば、音が小さくなる原因を調べようと思いましたが、今回はレイテンシが77でも問題ないのでDSPを使わない方を使用します。

6月29日

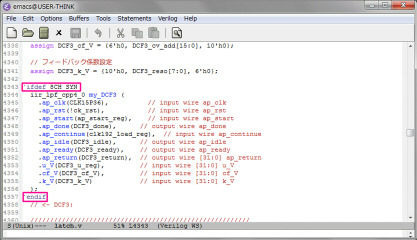

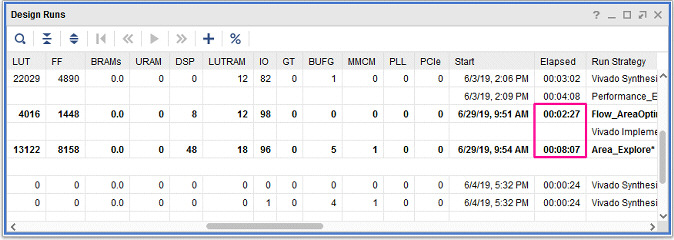

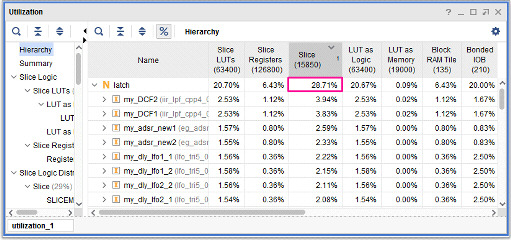

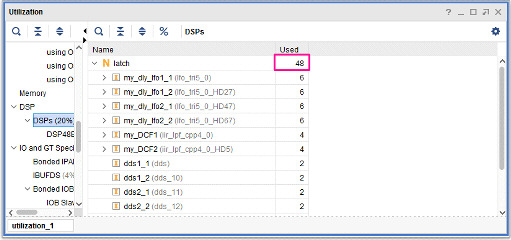

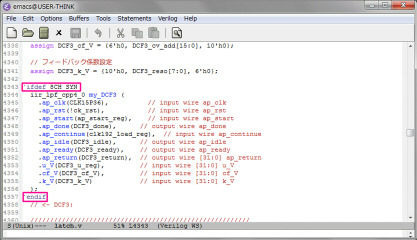

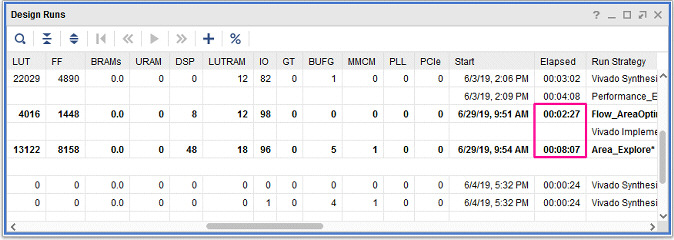

FPGAシンセのロジックはあと少しで完成ですが、DCOのEG周波数変調をマイナス側にした時にボローで不具合が出たため、2チャンネルに戻してコンパイル時間を短縮します。メインのロジックで呼んでいる機能IP(DCF、DCA、EG、LFO、DDS)の内6chを呼ばないようにするだけで、簡単に2チャンネル化できます。以下のように‘ifdef〜‘endifでIPを無効化します。

コンパイル時間は約10分になり、だいぶ早くなります。

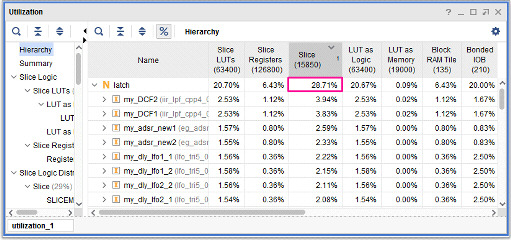

スライス使用量は28.71%です。

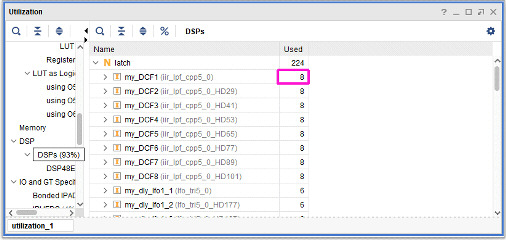

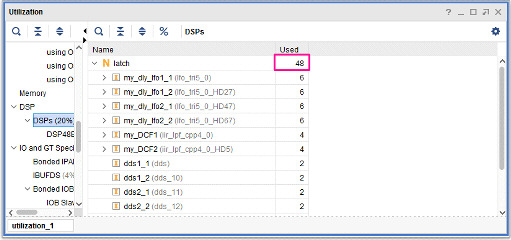

DSPは48個使用しています。

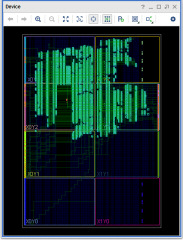

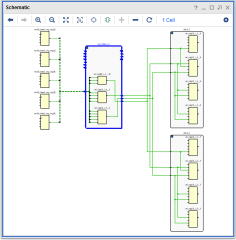

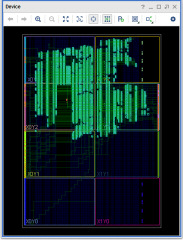

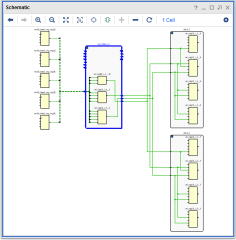

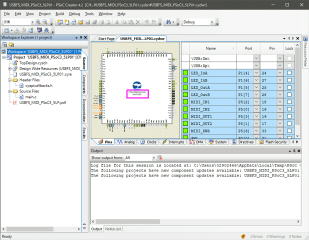

デバイス図です。

FPGAにダウンロードして動作確認しました。動作良好です。

現在FPGAボードの電源はUSBから給電していますが、FPGAボードのDCジャックに変更します。9V電源をアマゾンから購入しました。

6月30日

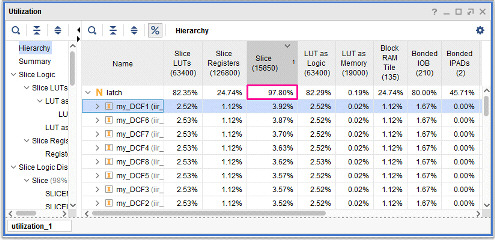

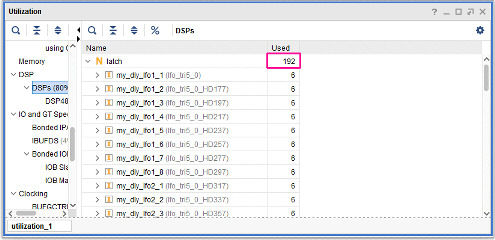

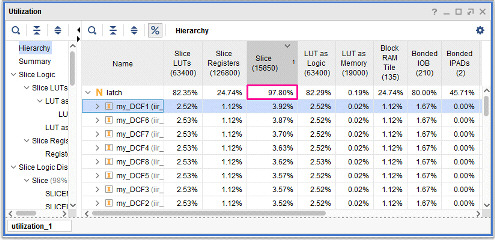

2チャンネル化してコンパイル時間が短くなったので、DCOをマイナス側に変調した時の不具合を調べて修正しました。DCO2にもEGによる周波数変調を実装して8チャンネルに戻しました。スライス使用量は97.8%です。

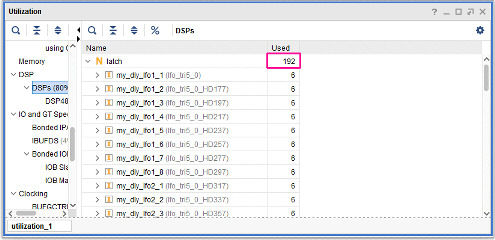

DSPは元と同じ192個です。

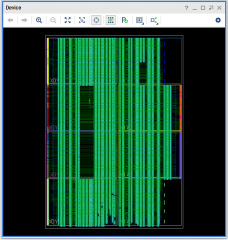

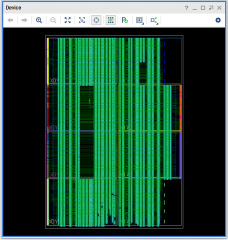

デバイス図です。

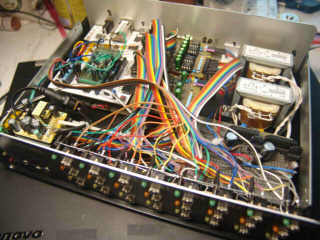

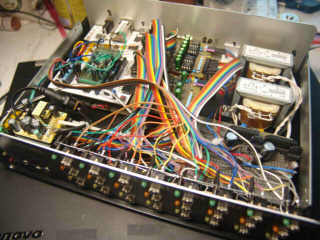

購入した9V電源は分解してステーを介してケース内に収めました。これでロジックをダウンロードする時意外はUSBケーブルを使わなくてよくなりました。

ベロシティ入力用のXADCのアナログ入力のA0〜5と6、7は入力回路が異なるので抵抗を変更し、残っていたベロシティ入力の配線を追加しました。

DCOのマイナス変調不具合でDDSロジックを修正したので、SK−88と合わせて音程を確認しておきます。動作良好です。

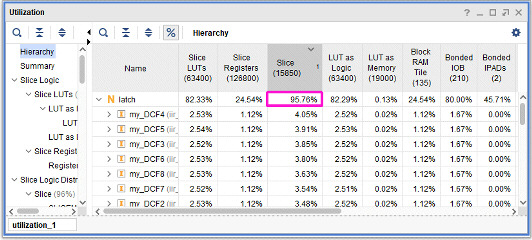

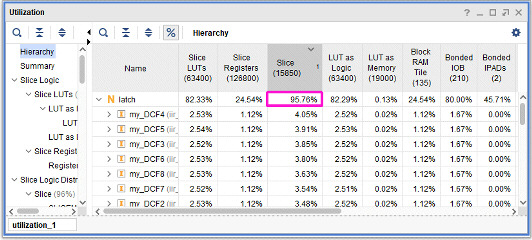

EGの時間パラメータの範囲が偏っているという問題も残っているので、LUTを増やすために、デバッグ用のSPI−DACのロジックを外しました。スライスの使用量は95.7%になりました。

7月6日

先週購入したパラメータ設定器のロータリエンコーダを25パルスに交換しました。ピンが基板の外に出ているため、簡単に交換できました。

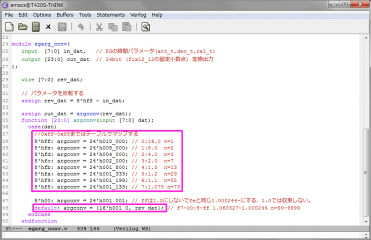

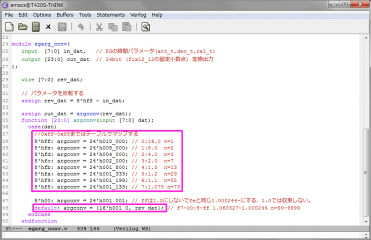

EGの時間パラメータの範囲が偏っているので対策します。EG

のアタック、ディケイ、リリースの各時間パラメータはコンデンサの充放電波形を模しています。現在はパラメータ設定器の00〜FFの値を固定小数点

fix12_12の良さそうなビット位置にリニアに当てはめています。このため可変範囲が狭くなっています。そこで、先頭の数個のみcase文で別の小

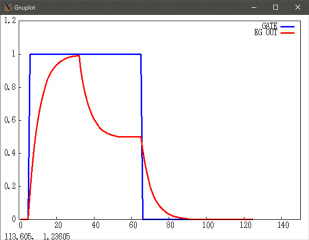

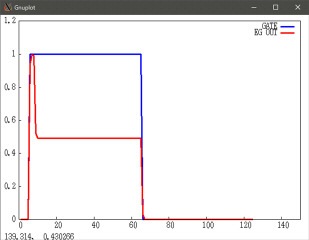

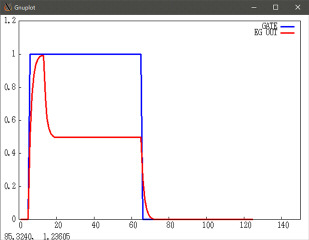

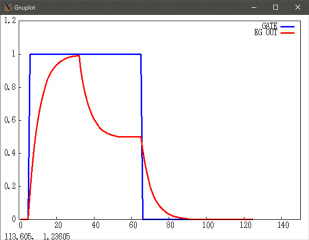

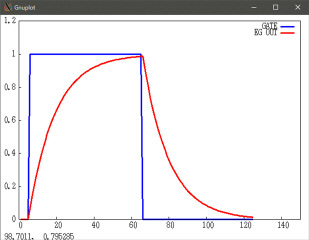

数点値にマッピングするように変更します。HLSのシミュレーション結果のCSVをGnuplotでグラフにして確認します。右が時間パラメータ

を16.0に設定した時です。次が右の2.0です。

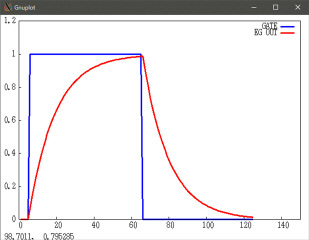

続いて、左から1.2、右が1.075です。サスティーンは全て0.5です。HLSシミュレーションなので1.075の時はアタックが立ち上がる前にゲートがOFFになっています。とりあえず4つをcase文でマップしてみましたが、効果はまずまずで、実際には先頭の8個くらいをマップすれば、かなり良くなりそうです。次回修正してみます。

7月7日

FPGAシンセは完成までもう少しですが、これら8チャンネル出力の接続先がありません。既存のアナログ・デジタルシンセも合わせて使いたいので、ミキサのケー

ブルを繋ぎかえるのはに面倒です。そこで、アナログシンセ側のVCA内にミキサ回路を追加し,VCAとミキサ間のケーブルはそのまま、FPGAシンセの出

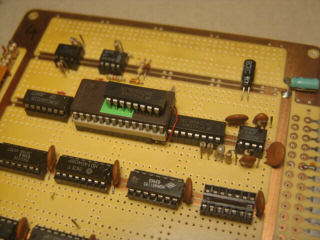

力をVCA出力とミキシングできるように改造します。VCAにはCVのリニア/エクスポネンシャルの切り替えスイッチがあるのですが、エクスポネンシャルは使用頻度が低いため、VCAの電源が入っていない時はこのスイッチを使って、FPGAシンセの出力がミキサに出力されるようにします。小基板に4558を載せて、2チャンネルのミキサを作ります。リニア/エクスポネンシャルの6極スイッチの配線を変更しました。VCAの1チャンネルのみ改造して動作確認しました。

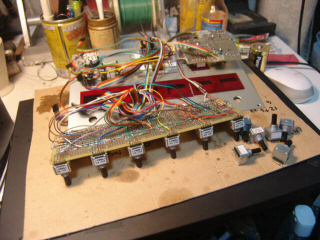

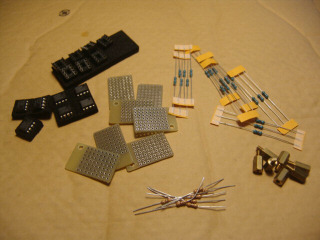

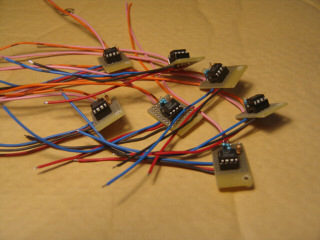

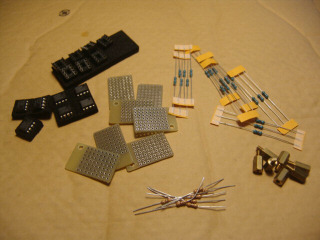

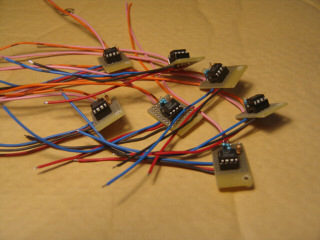

残りの7個を量産します。部品は全て手持ちで間に合いました。

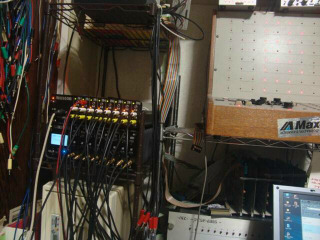

FPGAシンセをFPGAトーンジェネレータの上に設置します。パネルのチャンネル境界の縦線は合わせてあるので、良い感じです。上に乗っているのはTK80/BS用のLCDモニタです。

VCAの2チャンネルも改造して、アナログ・デジタルシンセとFPGAシンセのそれぞれ、2チャンネルで音出して、動作確認しました。FPGAのDCOとトーンジェネレータの音程も合っています。ただ、アナログ・デジタルシンセ側のDCO出力をFPGAシンセの外部入力で入力すると、2チャンネルはきれいなのですが、1チャンネルの入力は少し歪んでいるようです。次回確認します。

残っているVCAも改造します。3個追加したところで、8時近くなり時間切れです。残りは次回に持ち越しです。

7月13日

3連休ですが、土日のみガレージ作業です。マルツから購入したケーブルを使ってFPGAシンセとアナログ/デジタルシンセのVCA間のパッチケーブルを作製します。

左側がFPGAシンセとVCA間の出力用、右側は手持ちのケーブルで作製したFPGAシンセとDCO間の外部入力用です。

下はMSP430のUSB−MIDI変換器と接続するベロシティ入力のケーブルです。

EGの時間パラメータの範囲が偏っている件です。先頭の8個をcase文で16.0、8.0、4.0、2.0、1.5、1.2、1.1、1.075の小

数点値にマッピングしました。良くなりました。

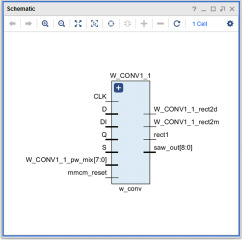

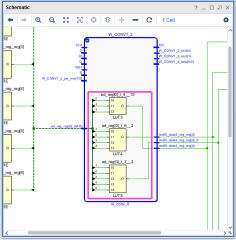

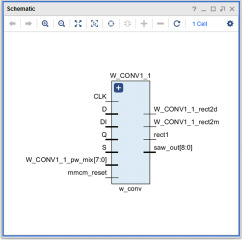

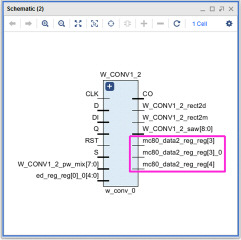

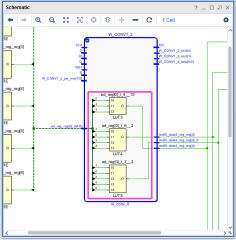

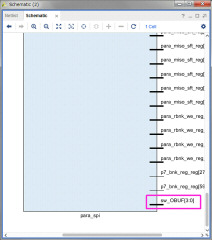

Vivadoのインプリメンテーション後にネットリストから回路図を表示すると、不可解なブロック図が表示されます。下はDDSの512倍クロックからノコギリ波とPW波、2倍と1/2の矩形波を生成するW_CONVモジュールです。左の1チャンネル用の出力信号は良いですが、右の2チャンネル用のブロックから出ているmc80_dataXXはこのモジュールとは無関係の信号のはずです。

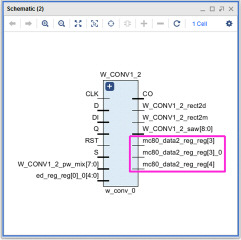

ブロック図の信号線をダブルクリックすると、接続先の回路が展開されます。展開して調べるとmc80_dataXXはW_CONV1_2の中を通っているだけの信号でした。

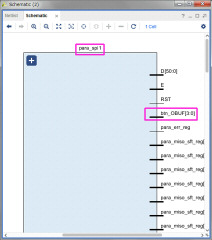

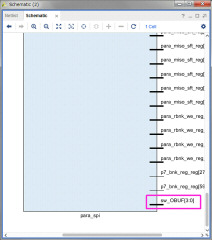

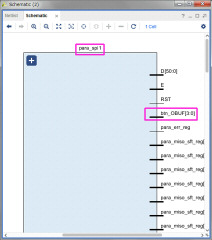

パラメータ設定器からのSPI信号を入力するpara_spiモジュールも無関係と思われる信号が表示されます。btnとswはボード上のプッシュスイッチとスライドスイッチの信号を修正してパネルに接続したLED出力です。展開して調べると、こちらもモジュールの中を通っているだけの信号です。ネットリストのブロック図に表示される信号は本来のモジュールの信号ではない場合もあることが判明しました。

7月14日

作製したパッチケーブルを使ってアナログ/デジタルシンセ、USB−MIDI変換と接続して動作確認しました。外部入力はオフセットが掛かっていて修正が必要です。また、ベロシティ入力の可変範囲が小さいことがわかりました。これは3V入力に1Vを入力していること、ロジックも最適ではありませんでした。こちらも修正が必要です。現在のスライスの使用量が97%を超えているので、調整しきれるか心配です。

7月20日

先週、マルツで購入したPSoC5LPの評価ボードです。USB2.0のフルスピードが内蔵されていて、USB−MIDIのサンプルコードが標準で付いています。コアは32ビットのARM−cortex−M3です。また周辺IOとは別に小さいCPLD(12入力のLUTx2+4つのFFx2)とFIFO付きALUが24個実装されていて、プログラム可能です。今後、MSP430からPSoCに移行予定です。

FPGAシンセは先週のベロシティと外部入力の問題を修正したので、旧アナログ/デジタル混在シンセに接続して動作確認します。

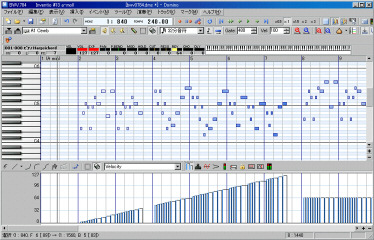

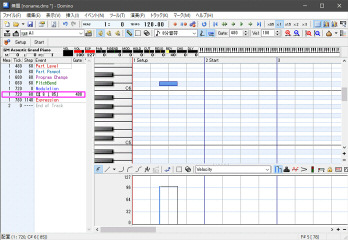

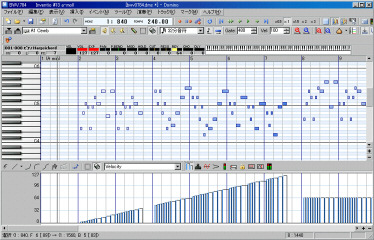

はじめにベロシティ制御です。Domino内でベロシティを付けて動作確認しました。丁度良いレベルでコントロールできるようになり、動作良好です。

次

は旧シンセのDCO出力をデルタシグマADCでDCF手前にミキシングする外部入力です。FPGAシンセ側の問題は直ったのですが、旧シンセのDCO4の出力

波形が不安定です。ROMのデータを読み出すDACとアドレスカウンタの4040を交換しました。旧DCOは1チャンネル分を筐体から取り出すことができないため面倒で

す。

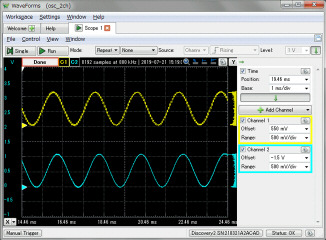

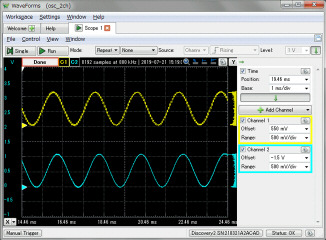

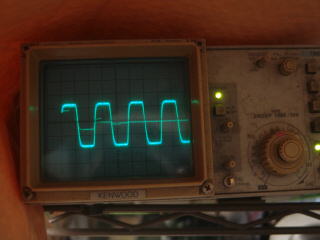

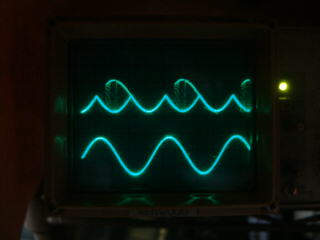

壊れていたのは4040でした。交換して不安定さは無くなりましたが、まだ波形がおかしいです。上の波形がDCO4で下が正常なDCOです。ROMのアドレスかデータのどちらかの最下位ビットが入れ違っているかもしれません。これは次回に確認しにします。

7月21日

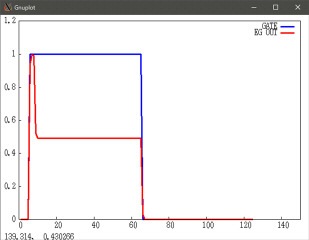

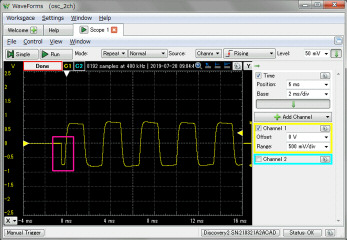

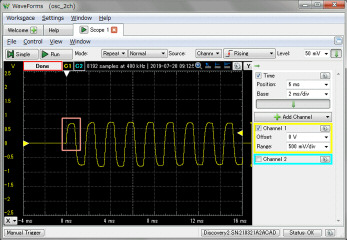

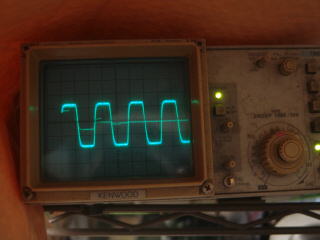

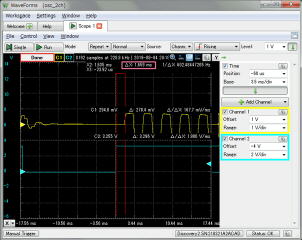

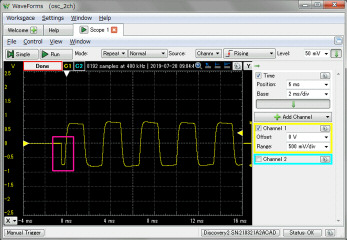

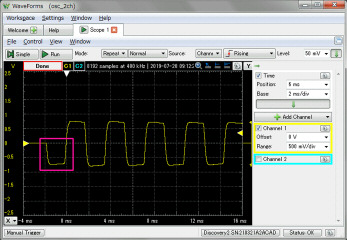

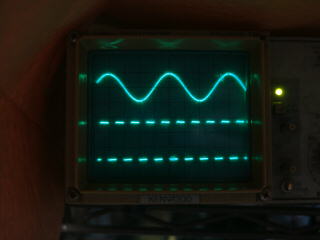

別の問題です。エンベロープジェネレータのアタックとリリース時間が短い時にプチ音が気になります。ゲートとDCOの出力は非同期なので、細いパルスが出る場合があります。下は細いパルスが出ています。このときプチ音が出ます。

対策としてはじめに試したのはDCAのゼロクロス出力です。アタック時にゼロクロスした後で出力するようにします。アタック時は解決できました。

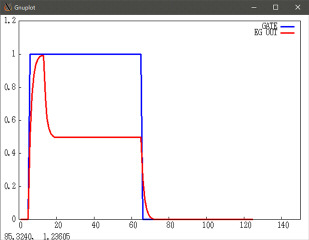

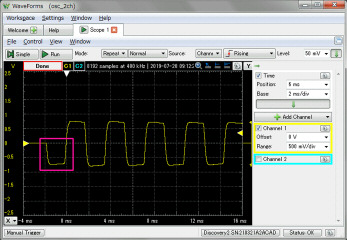

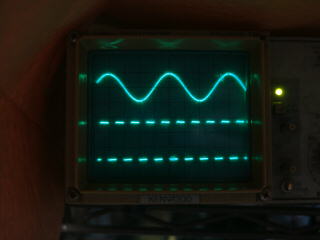

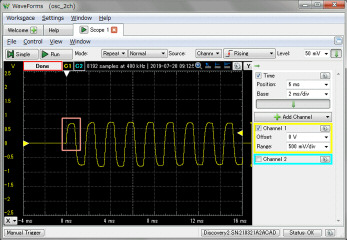

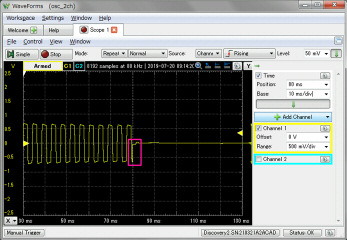

リリース時はゼロクロスが機能しません。左はリリースが短い時、右はリリースが長く、アタックと繋がっている時です。DDSでも対策が出来そうです。ゲートONの時とノート番号が変更になった時に、DDSのアドレスカウンタを0クリアする方法です。これは次回試してみます。

7月27日

プチ音の続きです。DDSに対策をしたのですが、アナログディスカバリを会社に置き忘れたため、アナログオシロで調べますが、単発で見られないので良く分かりません。次回に持ち越します。

旧DCOの4チャンネルが不調の件です。4040を交換して直ったと思ったのですが、直っていませんでした。DCO専用のバスエクステンダで筐体の外に出して調べます。正常です。

筐

体に戻すと不調になります。これで原因が分かりました。筐体に入れる時はDCOの出力にケーブルを接続します。DCOの出力は次段のVCFの前にあるミキサに入力されますが、筐体が別なので、電源を入れていま

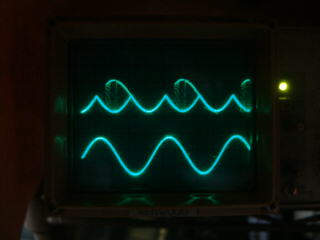

せんでした。この時は波形が崩れます。上がDCO4、下は正常なチャンネルです。双方ともミキサの電源は入っていません。ミキサに使用しているオペアンプの

特性と思われます。もしかしたら4チャンネルのオペアンプの入力段が壊れているのかもしれません。先週、原因だと思ったROMテーブルを読み出す4040は壊れていませんでした。VCF/VCA/EG部に電源が入っていれば不具合はありません。

7月28日

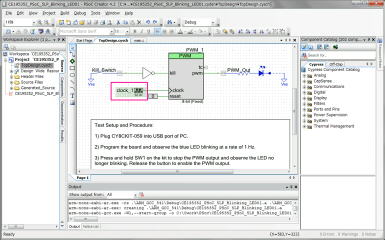

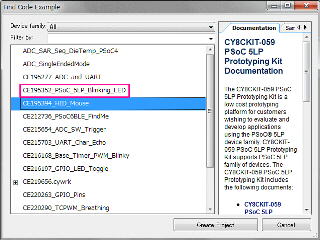

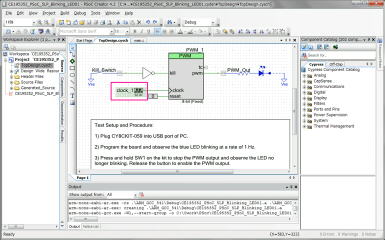

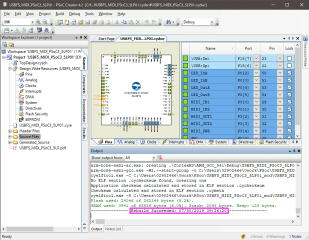

PSoC5LPの続きです。開発環境をUSBメモリに入れて持ってきたので、サンプルプログラムをビルドしてみます。元々入っているLチカ(PWM駆動)が入っていますが、点滅速度を変更してみます。サンプルコードのBlanking_LED1を開いて、PWMに入る50Hzのクロックを変更してみます。

再ビルドして、書き込むと点滅速度が変わりました。

7月29日

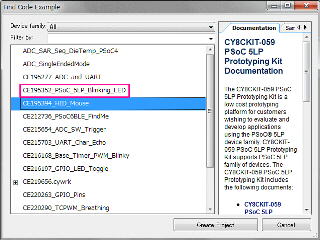

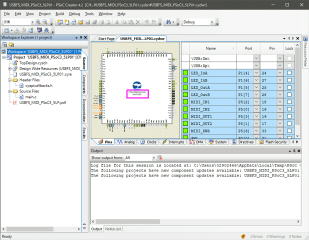

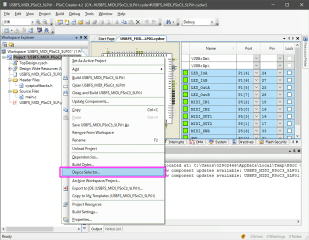

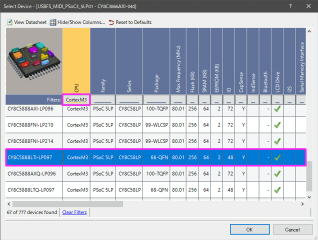

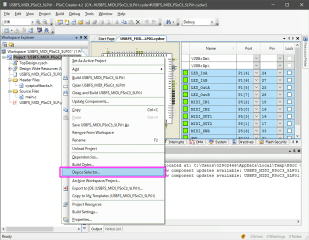

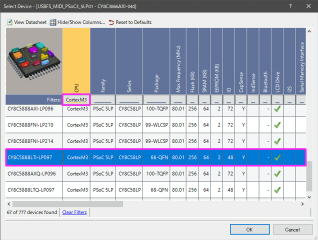

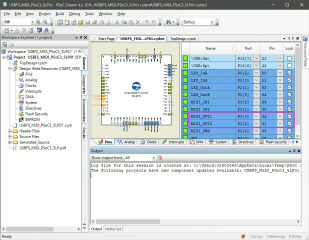

PSoC5LPの続きです。会社のPCでUSB−MIDIのサンプルコードをビルドしてみます。サンプルコードのデフォルトは100ピンのCY8C3866用です。プロジェクトで右クリックからデバイス選択を選んで、ウインドを出します。

CortexのM3のCY8C5888LTI−LP097を選びます。

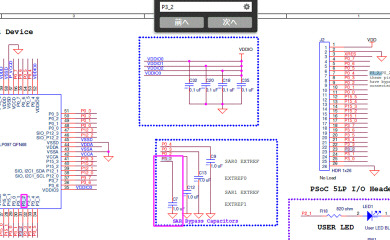

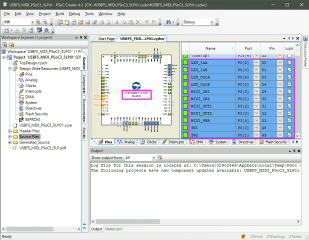

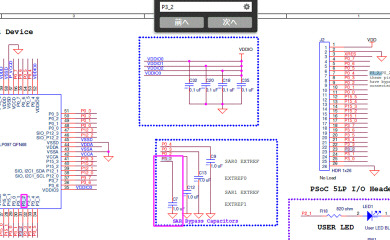

パッケージが68ピンの5888変更されます。回路図を見ながら、何にも繋がってないポートにLEDとUARTを割り当てます。

その後、クリーン/ビルドして、書き込みます。マイクロUSB側をPCに挿してデバイスマネージャのオーディオデバイスにMIDIデバイスが認識されることを確認しました。MSP430の時はCDCのサンプル

コードからMIDIデバイスとして認識させるまで3週間くらい掛かりました(笑)。このPSoCでは一瞬でできました。

8月1日

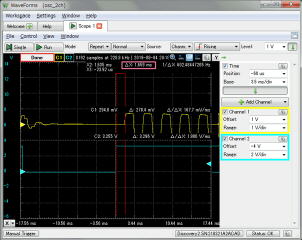

PSoC5LPの続きです。会社の休み時間に動作確認をしてみます。ピンアサインでUARTのMIDI出力1をたまたま、P3.2に設定したのですが、出力波形が変なので回路図を確認すると1uFのコンデンサが付いていました。SAR−ADC用コンデンサのようです。

とりあえず、MIDI出力の1と2のピンを入れ替えて、MIDI出力1をP3.3に設定し直して、再ビルドして書き込みます。

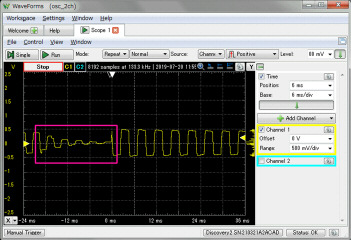

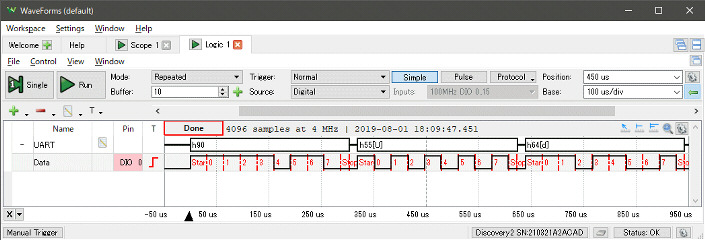

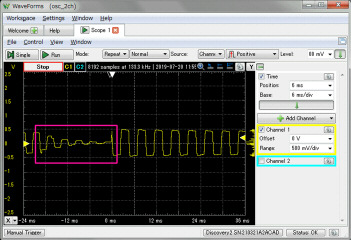

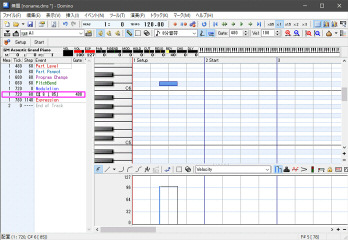

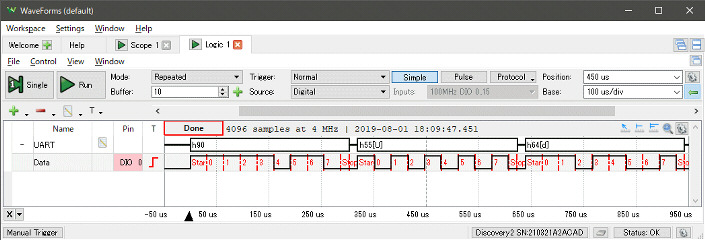

Dominoを立ち上げて、出力先をPSoCのUSB−MIDIに設定し、イベントを出力します。分かりやすいようにノートナンバ85(0x55)を出します。

アナログディスカバリのUARTプロトコルアナライザでP3.3を測定します。波形が反転しているので、アナライザ側でも反転します。ボーレートは自動で31.25Kbpsになります。ノートオン:0x90、ノート:0x55、ベロシティ:0x64が出力されノートナンバは0x55が出ています。正しく動作しているようです。週末にガレージに持って帰ってMIDIデバイスに接続してみます。

8月3日

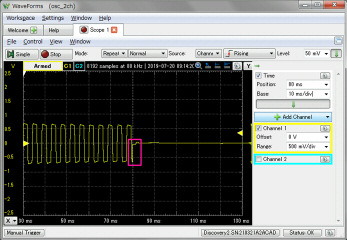

プチ音の続きです。アナログディスカバリで確認します。EG用のゲート信号を使って、DDSのアドレスカウンタをクリアするロジックはアタックが最短でも約1mSec以上の遅延があり、波形の先頭から出力することができないことが分かりました。もう少し調査してみます。

8月4日

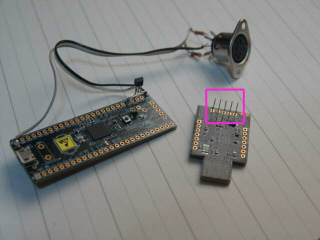

PSoC5LPの続きです。DINコネクタをUART1に接続して動作確認しました。SC88に接続して問題ないことを確認しました。ボードはデバッガ部を切り離しました。

デバッガ部にはマック8のコンスルーピンをハンダ付けして、ボードに接続できるようにしました。スルーホール径0.8mm用ですが、プラスチックのハウジングを外せば1.0mm径にも使えます。