TK80/BSの

シンセシステムを復活/拡張したい〜

その42

パラメータ設定器の調整、動作確認

SBC8080ボード

2019年

2019年

9月7日

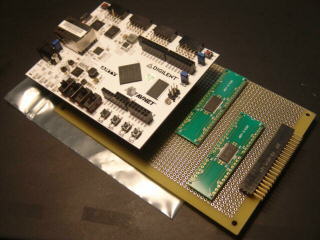

2台目のARTY−A7(100T)です。別に欲しい部品があったので、マルツより少し高いでが、秋月で購入しました。次期プロジェクトのウェーブテーブル用です。当初、ウェーブテーブルDCOのみをARTY(35T)を実装して、アナログで出力する予定でしたが、DCF、DCA、EG、LFOも実装する予定です。

ユニバーサル基板も購入しておきました。

12VのスイッチングレギュレータのACアダプタです。旧アナログ・デジタルシンセ用です。以前にディレイド・モジュレータを追加して、少し電源容量が足らないようなので、この電源で強化します。

ACアダプタのケースは取り外し、動作確認しておきました。

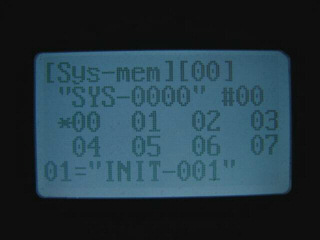

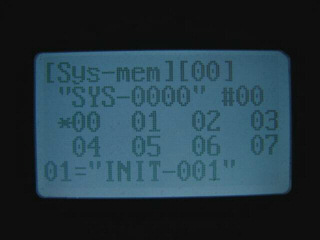

先週からの続きのパラメータ設定器のプログラムを調整/デバッグです。PC−USBモードにXMODEMを実装する予定でしたが、細かい動作を修正しました。右はシステムメモリモードの8チャンネルをグループに設定するLCD画面です。丸2日かけて、ほぼ終了しました。次回、XMODEMを実装します。

8chを使ってBWV540を録音しました。画像をクリックすると約8Mバイトのmp3ファイルをダウンロードします。曲は約8分40秒です。この日は台風15号が関東直撃とのことで、早めにアパートに帰りました。

9月13日

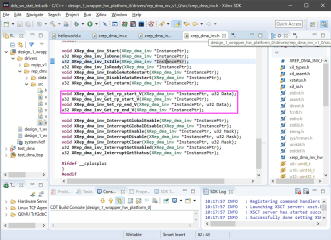

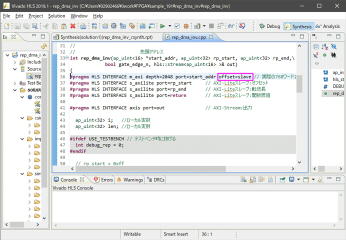

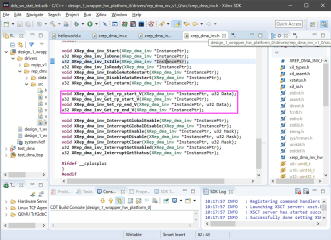

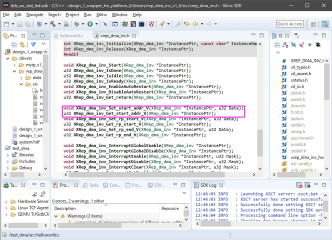

次のプロジェクトのウェーブテーブルDCOの続きです。マイクロブレーズのSDKからDMAのレジスタアクセスの確認です。DMAのスタートアドレスのアクセス関数がありません。

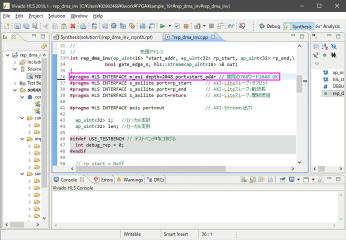

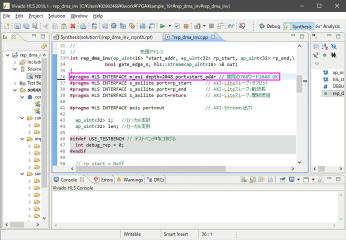

HLSの引数の設定部分を確認します。参考にしたWEBページの記述を確認すると、AXIマスタのスタートアドレスにはoffset=slaveという記述があり、これを追加しました。

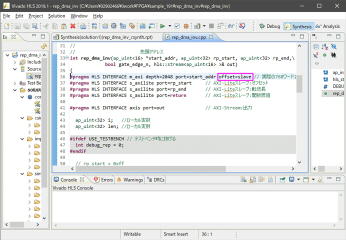

追加後、再合成して確認します。スタートアドレス設定関数が出現しました。

9月14日

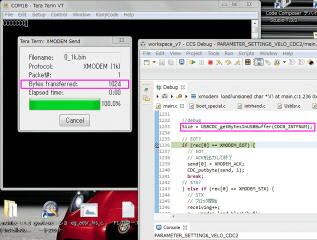

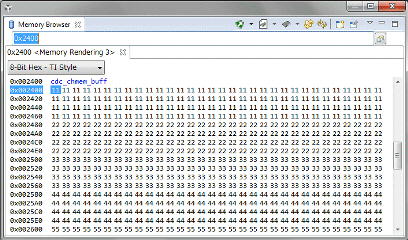

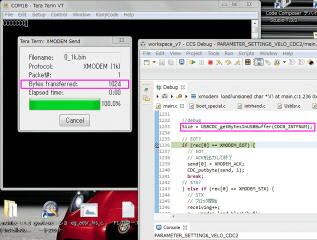

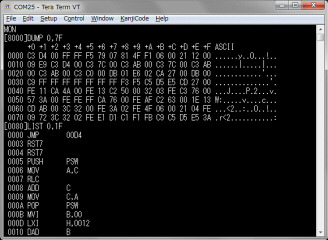

この週末は土日のみガレージ作業です。パラメータ設定器のPC−USBモードにXMODEMの実装を開始しました。送信から開始したのですが、CRCが一致しないようなので、CRCを確認するため受信に切り替えました。PC側に用意したデータは0x11、0x22、0x33...が0x80の長さでフィルして1Kバイト長で作成します。

Teraterm側からは1Kバイト送っているように見えます。

プログラムはUSBの受信バッファに残っているデータ数を確認して、API関数で読み込みます。

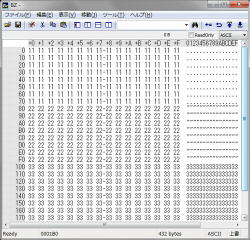

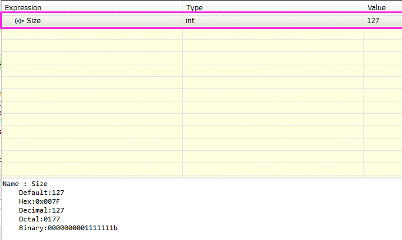

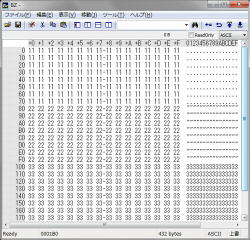

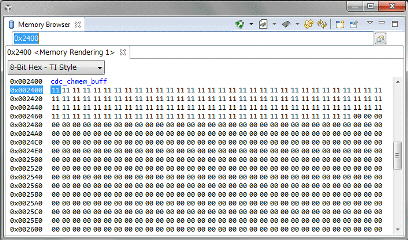

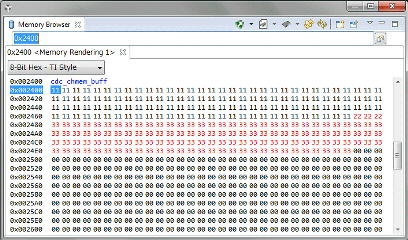

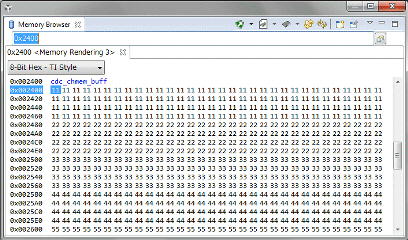

1回目のバッファの内容です。3バイト0x11が足りていません。STX、ブロック番号の2個分の合計で3バイトの0x11が足りていないようです。

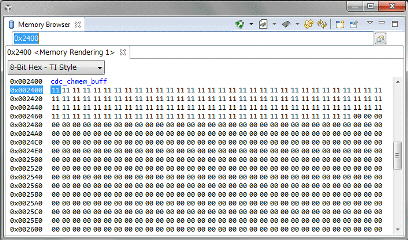

2回目のバッファの内容です。0x22が3バイトだけで、その後は0x33になっています。もう少し調べてみます。

9月20日

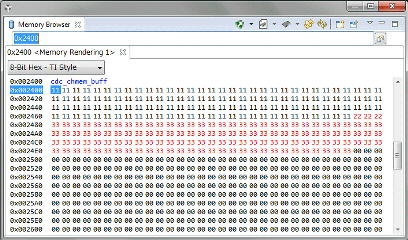

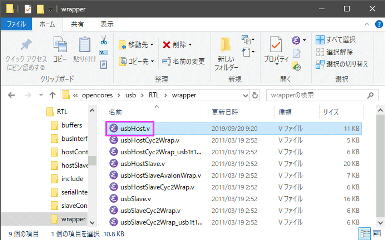

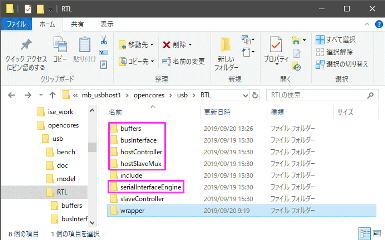

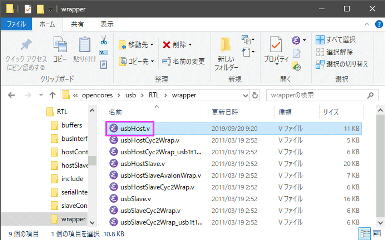

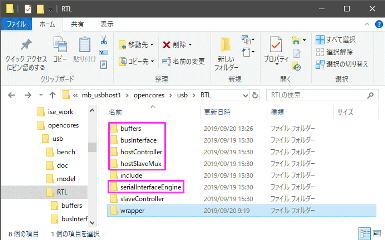

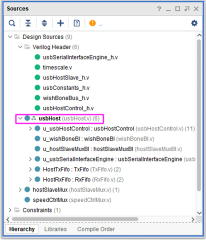

以前、FPGAマガジンにOpenCoresのUSBデバイスIPの記事があると紹介しましたが、このIPはホストも含まれていて、環境がISEとSpaltan−6でちょっと古いです。Vivadoで合成、インプリできるか確認してみます。プロジェクト一式を解凍して、wrapperの下に

あるusbHost.vがホストIPのトップモジュールです。

赤枠内は必要なサブディレクトリです。

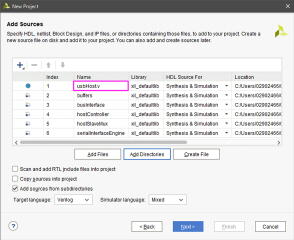

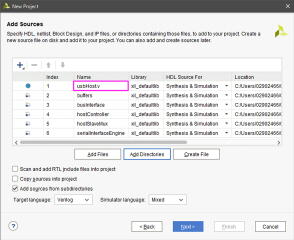

Vivadoで新規プロジェクトを作成し、トップモジュールと他のサブディレクトリをソースとしてプロジェクトに追加します。

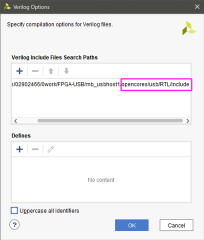

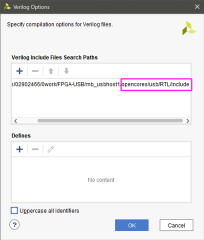

次にインクルードファイルのディレクトリもプロジェクトに追加します。

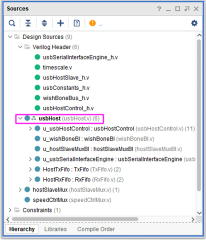

Vivadoのソースウインドは以下のようになりました。WISHBONEバスを直接端子に出して適当な制約ファイルを作成して合成、インプリできるか確認します。

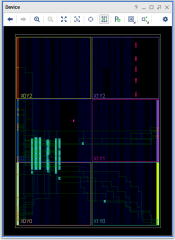

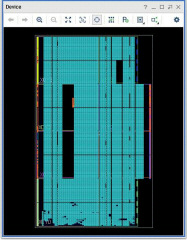

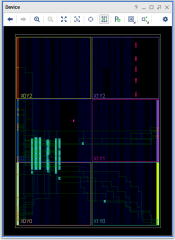

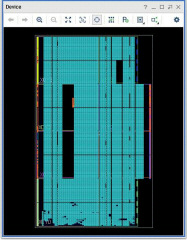

FPGAはいつものARTY(35T)ボードです。以下はデバイス図です。

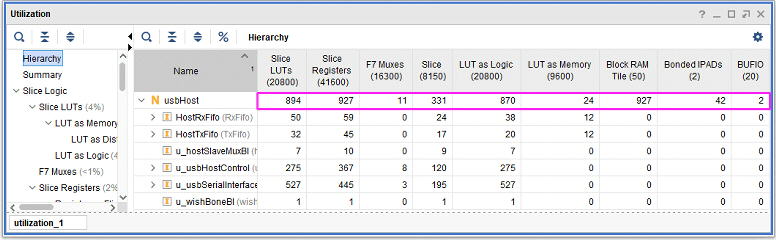

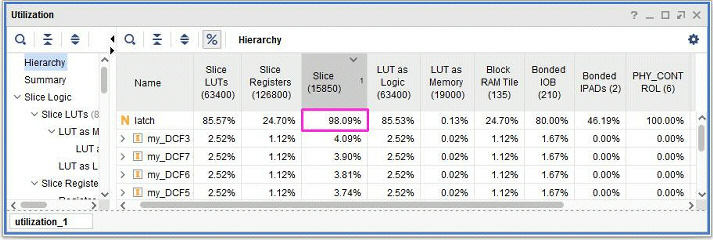

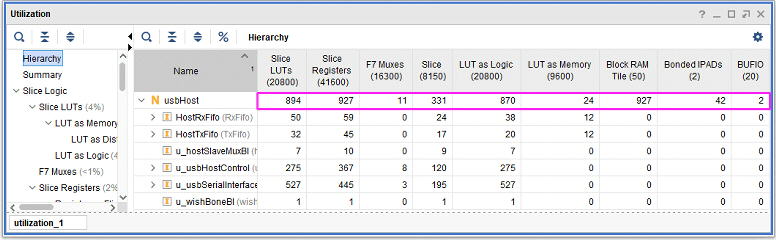

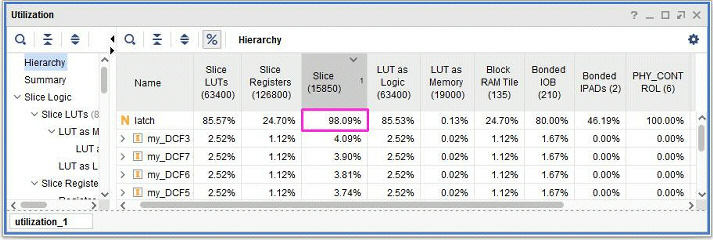

続いて、ロジックの使用量です。合成、インプリまで問題なさそうなので、今後IP化してホスト用ラブラリを使ってMicroBlazeで制御できるようにする予定です。

9月21日

この週は遅い夏休みです。パラメータ設定器のPC−USBモードのXMODEMの続きです。以下は正常にPCからのデータが転送できた時のメモリダンプです。常にうまく行くわけではなく、正しく受信できない時もあり、まだ原因が分かりません。

9月22日

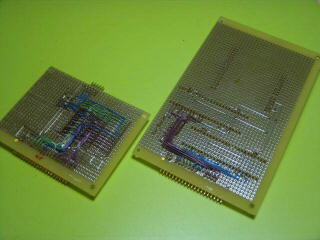

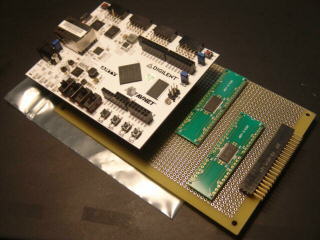

SBC8080というボードがあるのを最近知りました。SUBボードもいっしょに入手しました。シンセ制御の使用しているTK80BSは一応現役ですが、メモリデバイスとICソケットの接触不良が多いです。そこで、このCPUボードを使用してTK80BS互換機を作製する予定です。

秋月から購入した、SBC8080用の部品です。

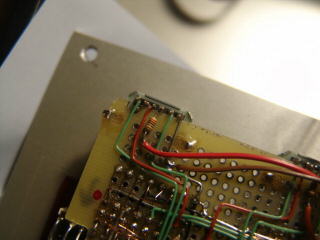

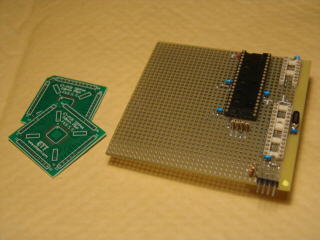

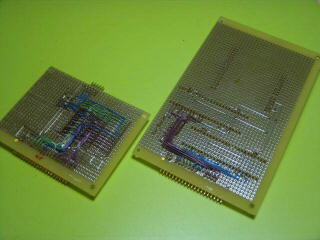

CPUボードとSUBボードに部品を実装しました。ICソケットは全て手持ちの丸ピンを使用しました。

BSの機能を実装するFPGAボード用の変換ボードも作製します。FPGAボードはARTY(35T)です。FPGA内にVRAMと

OpenCoresの8255を実装してキー入力を行う予定です。ユニバーサル基板に載っているのは5V−3.3V変換基板です。

FPGA

シンセに半音単位で音程をオフセットする機能を追加しました。以前に作成したFPGAのDDSトーンジェネレータにも組み込まれている機能なので、これと

音程が合うようにしました。オフセット設定はパラメータ設定器のシステムモードで行います。また、以前にフロントパネルに追加した1オクターブのオフセットスイッチは全チャンネルのミュートスイッチに転用しました。

パラメータ設定器のP1のロータリエンコーダのプッシュスイッチの動作が不安定です。押さなくても押した状態になります。分解して調べると原因はプッシュスイッチの電源側が半田不良でした。ロータリエンコーダを50パルスから25パルスに交換した時に半田不良になっていたようです。

正常動作になりました。良かったです。

SBC8080

の続きです。手持ちの旧ソ連製?8080チップセットと、SRAMの62256、UVEPROMの27256、また1977年製のインテル8251

を用意しました。サポートページのモニタ機能付きPaloAltoタイニーBASICのROMを書き込みます。

9月23日

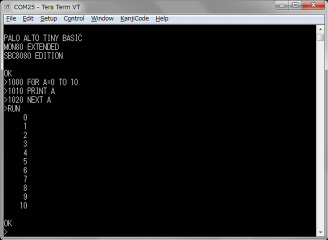

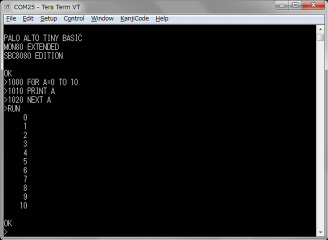

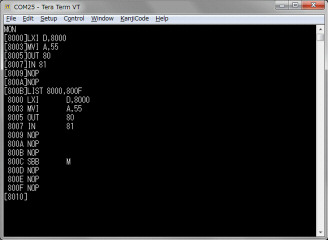

TeraTermを接続して動作確認します。BASICが動作しました。

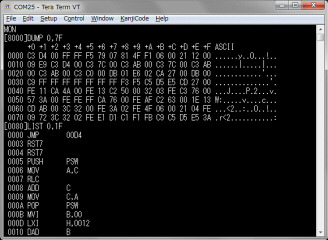

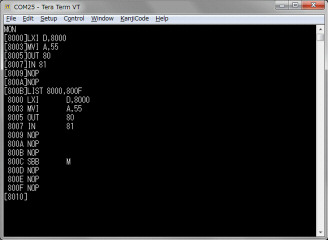

続いてモニタプログラムです。ダンプと逆アセンブラを実行したところです。

このモニタは簡易アセンブラが付いていて、ニーモニックでプログラムの入力ができます。動作良好です。

9月24日

パラメータ設定器のXmodemが正常に動作しないですが、とりあえずTeraTermのバイナリファイル転送機能で代用し、暫定的な完成とします。MSP430LPを別途購入して、Xmodemのプログラムは継続して調査します。

半音のオフセット、全ミュート機能を実装したFPGAのロジック使用量です。98.09%になりました。

続いてデバイス図です。

ヤフオクで27C512を購入しました。TK−80BS互換機用です。512Kビットは64Kバイトですが、0〜FFのベクタとフロッピ用IPL、D000〜EFFF番地にあるBASIC、Fxxx番地にあるモニタをこのROMに入れます。アドレスを工夫してLevel−1/2のBASICもこのROMに入れる予定です。

9月27日

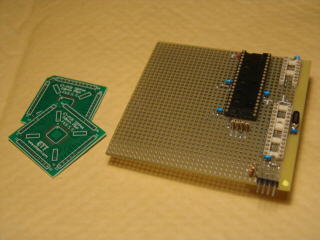

TK80BS互換機のROM/RAMボードとFPGAボードを作製します。RAMは手持ちの628128LPを使います。容量は128Kバイトですが、前半の64Kの内、下位の0100〜7BFF、上位の8000〜CFFFまでの2つのエリアを使います。後半の64Kはもったいないですが使用しません。ROM/RAMのアドレスデコードはFPGAで行います。LP品なのでニッケル水素電池でバックアップできるようにします。

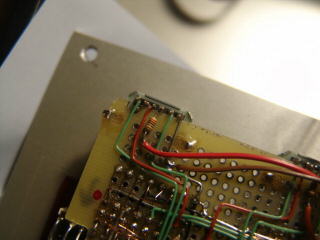

ROM/RAMボードとFPGAボードの配線を行いました。

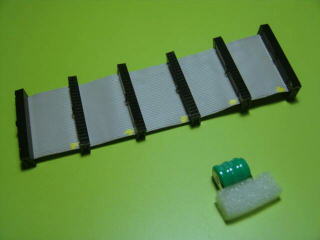

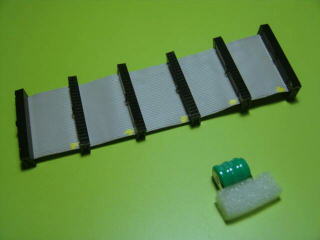

手持ちの40ピンのコネクタを6個圧接し、マザーコネクタを作製しました。アマゾンでニッケル水素のバックアップ電池も購入しておきました。

OpenCoresのUSB1.1のホストライブラリの記事が載っている、インターフェース誌の古本を購入しておきました。使用目的はTK80BS互換機用のFPGAに直接、USBキーボードを接続することです。

10月5日

この週は土曜の夜にガレージに来ました。秋月で購入したMSP430LPとブレッドボードセットが来ました。

こちらはQFP44の変換基板です。8080簡易ICEのCPLD用です。ダウンロードケーブルがまだ入手できていないので、CPLDの書き込みができません。

10月6日

SBC8080のマザーコネクタ用固定プレートを作製しました。1.2mm厚のアルミ板にストレンリリーフの穴を開けて固定しました。1.2mm厚は丁度フラットケーブルの厚みです。動作確認をしたところ、良好でした。

8080簡易ICEはCPLD用の変換基板用ピンソケットを実装して、配線を進めました。だいたい80%程終了です。CPUケーブルは使用せず、CPUボードのCPUソケットに重ねて使用します。

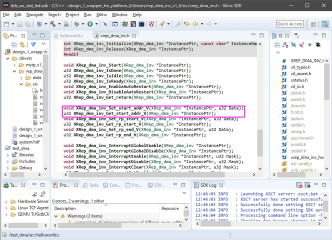

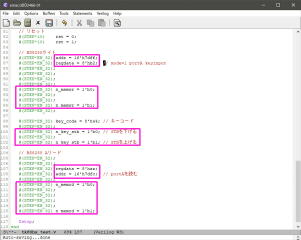

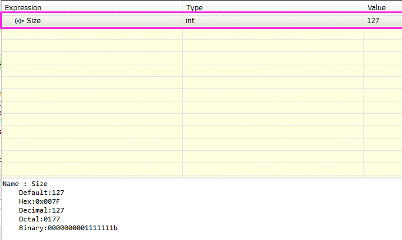

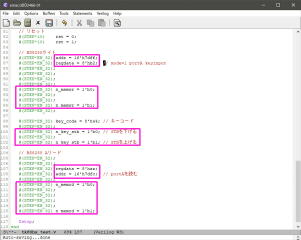

パラメータ設定機のXMODEMの受信の調整デバッグを行いました。XMODEMはPCからSTXの1バイト、ブロック番号が2バイト、データ本体の1024バイト、CRCが2バイトが送られてきます。ブロック番号以降の1028バイトを一度に読むと、正常に受信できるようになりました。原因は、例えばMSP430側がブロック番号を2バイト分を読んだ時に、既にPC側はデータ本体まで送信しているということのようです。

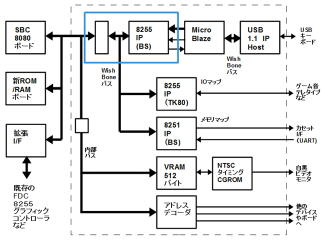

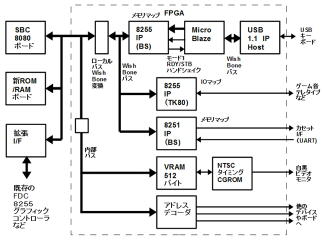

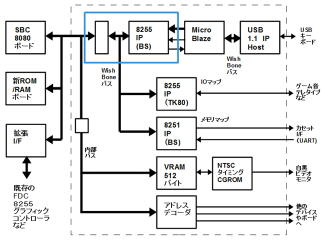

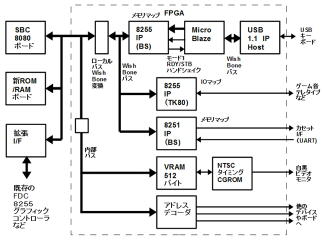

SBC8080を使ったTK80BS互換システムのブロック図を作成しました。8251(UART)はIPが見つかってません。

10月9日

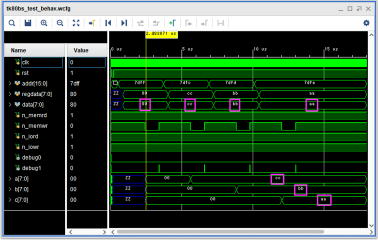

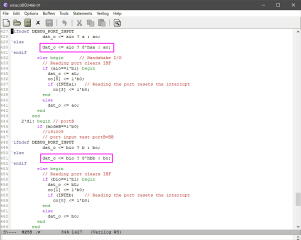

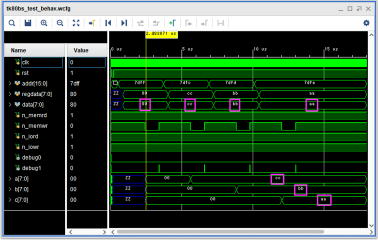

TK80BS互換システムで使用する8255のIPの動作確認を行います。はじめOpenCoresにあるこの8255を使う予定でしたが、クロックを使用しない非同期ロジックだったので、検索したところGitHubに別の物が見つかりました。ソースはここにあります。Vivadoでシミュレーションを行います。はじめにモード0の出力です。制御ワードに0x80を書いて、ポートA=0xCC、B=0xBB、C=0xAAを出力します。問題なく動作しているようです。

続いて、モード0の入力です。3ポートを全て外部に接続するのは面倒なので、ソースにデバッグコードを入れて、強制的にポートA=0xAA、B=0xBB、C=0xCCを入力するように修正します。シミレーションで制御ワードに0x9Bを書いた後、ポートを読み出します。問題なく動作しているようです。

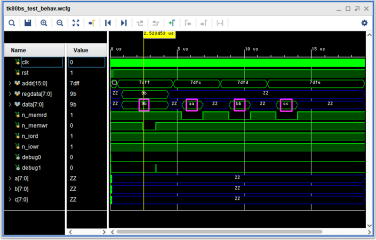

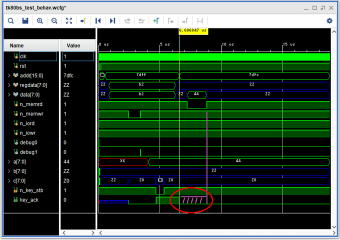

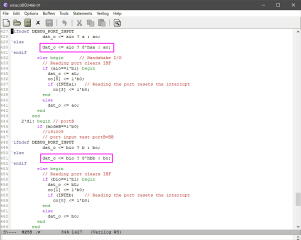

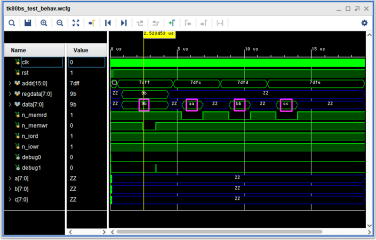

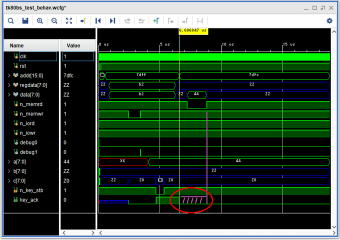

続いて実際に使用するモード1のポートA入力です。ポートAとSTB、IBF(ACK)を外部に引き出し、テストベンチで制御ワードにTK80BSの初期値と同じ0xB2を書いた後、ポートAに0x44を入力し、STBを下げて、適当に上げます。STBが下がるとACKがHighになります。ACKがクリアされるのはポートAを読んだ時のはずですが、シミュレーション結果を見るとポートAのアドレス(チップセレクト)によってクリアされています。このように動作するのは、このIPで使われているWishBoneバスにはWE信号しかなく、独立したリード信号が無いからと思われます。WEでなく、アドレスが確定すれば、それはポートAのリード動作です。実際にソースコード内でACK信号がアドレスでクリアしているのを確認しました。本物とのタイミングの違いは右の赤丸の部分です。

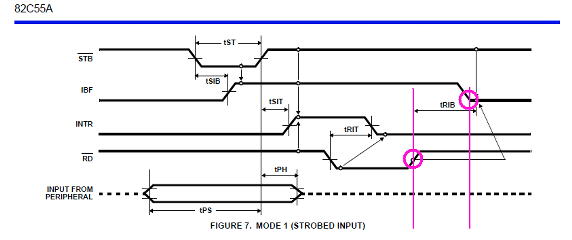

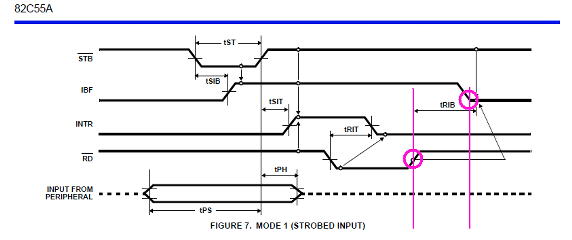

インターシールの82C55のデータシートで本物のタイミングを確認しておきます。モード1の入力のタイミングの抜粋です。

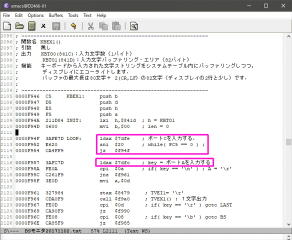

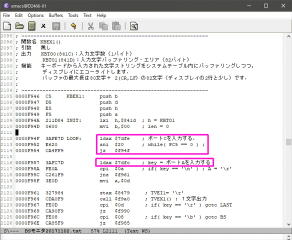

TK80BSのキーボード入力のプログラムの逆アセンブルを確認すると、以下のようになっています。PC5(ACK)がHighになるまで待って、キー入力しています。Lowに戻るタイミングは無関係なので、このままでも実害は無さそうです。

ブロック図中の青枠内のシミュレーションが完了しました。