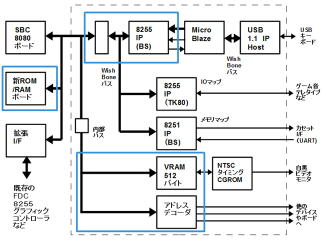

TK80/BSの

シンセシステムを復活/拡張したい〜

その43

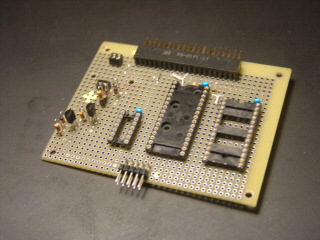

SBC8080ボード用簡易ICE

旧シンセの電源強化

2019年

2019年

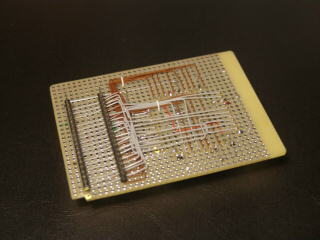

10月12日

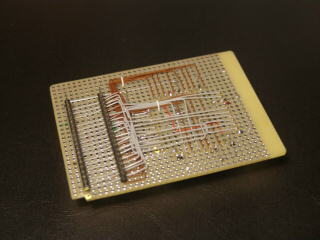

アマゾンでXilinxのCPLD用のUSBダウンロードケーブルの互換品を購入したとこと、税関を通関できないので返金すると連絡がありました。ケースにはXilinxの名前が入っているので、偽ブランド品という判断のようです(笑)。しかたがないので手持ちのROMライタ用の変換アダプタを作製しました。デバイスはXC9536(無印)ですが、JTAGを使った書き込みではないので、配線が多く、大変です。ROMライタで問題なく書き込みができました。

10月13日

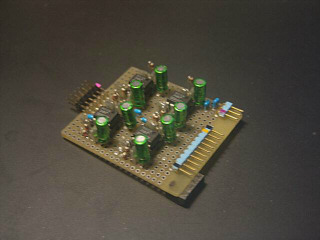

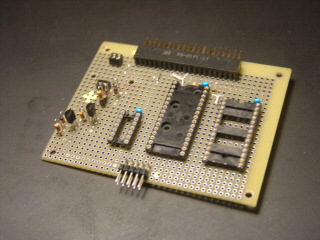

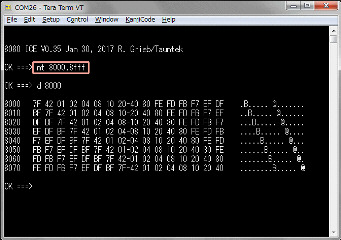

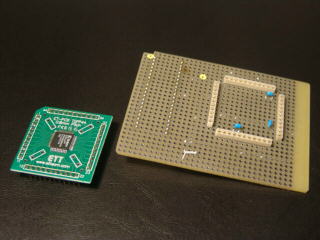

先週作製した8080の簡易ICEボードの配線を再確認し、上記のCPLDを実装します。CPUボードのCPUを取り外し、代わりに簡易ICEを挿して動作確認を行います。

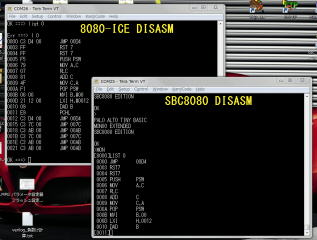

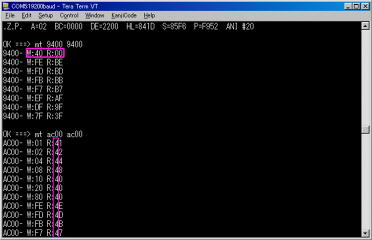

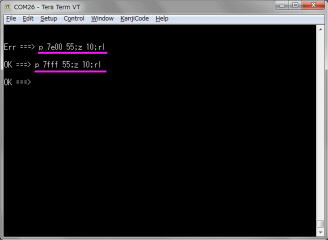

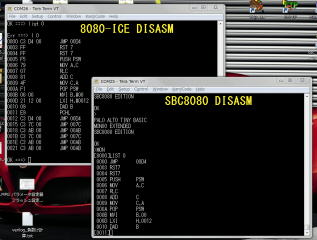

簡易ICEの動作は、ほぼ良好で、左画面がICEの逆アセンブルコマンド。右はSBC8080のモニタの逆アセンブルコマンドです。ICEの各コマンドも一通り動作確認しました。ただ、電源投入時にそのまま実行動作が出来ず、リセットボタンを押す必要があります。これはプリント基板を使ったオリジナルの方でも同じ動作でした。

この3年くらい、よく半田付けをするので、半田リールが無くなりました。同じ細い線径の半田がもう一つあります。

10月14日

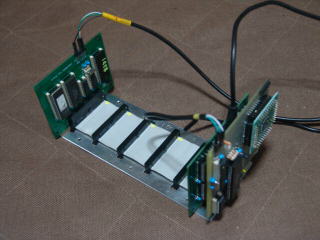

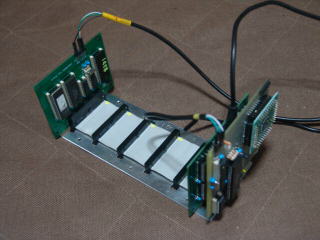

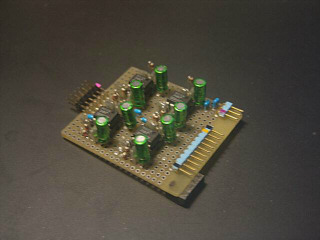

旧シンセの電源を強化します。この辺で作り始めたディレイド・モジュレータの消費電力が大きいので別電源にします。だいぶ前に購入した12VのACアダプタです。±12V電源に配線します。

旧シンセの筐体からモジュールを取り外し、電源を供給している端子台から、下の段のディレイド・モジュレータに配線している電源ケーブルを取り外します。

新しい電源を筐体内に固定してAC100Vに接続、ディレイド・モジュレータのみ、この電源を接続します。

ディレイド・モジュレータの電源が±15Vから±12Vに変更になったので、回路定数を変更(抵抗1箇所)し、トランスコンダクタンス・アンプのNJM13700の出力のオフセットを取り直しました。8チャンネル分、調整を行いました。

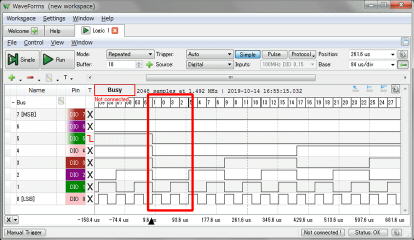

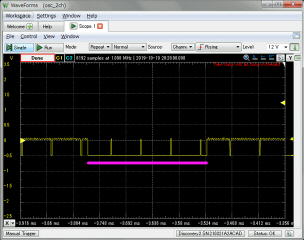

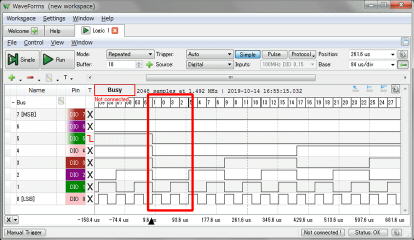

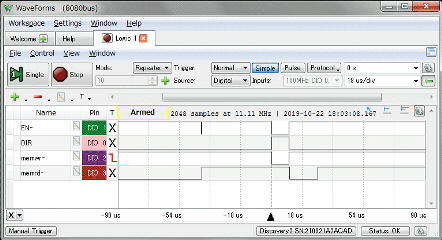

全体の動作確認を開始すると、DCO3の出力波形が異常です。はじめアナログのオシロで確認を始めたのですが、2チャンネルのアナログオシロでは原因がつかめず、アナログディスカバリのロジックアナライザを使って確認します。

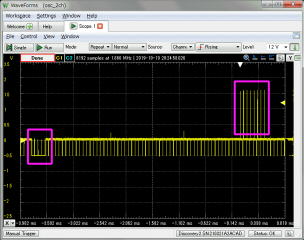

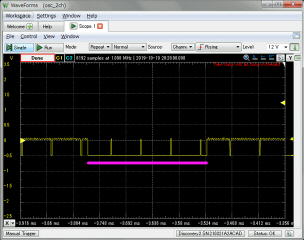

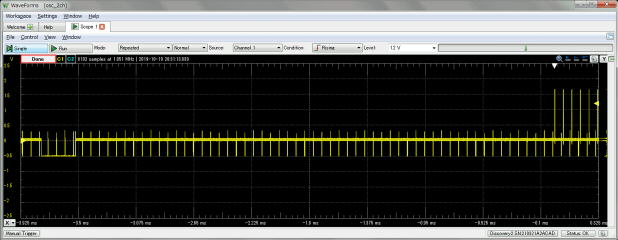

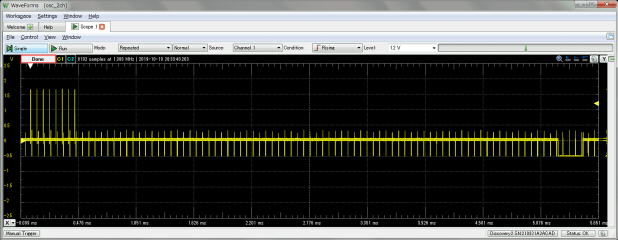

ROMテーブルのアドレスを確認すると、C−MOSの4040バイナリカウンタの動作不良であることが分かりました。4040はクロックの立ち下がりでカウントアップなのですが、なぜか立ち上がりでカウントアップになっています。動作速度を上げるために、クロックをROMテーブルのA0に接続しているので、この現象が起きるとアドレスが1、0、3、2、..となって出力が異常になります。4040はEbayから購入したものて、マーキングは”CD4040 HEF HLF”となっていなます。左が壊れてクロックの立ち上がりでカウントアップしている方。右は同じ新しいデバイスに交換した正常な波形です。

10月19日

この週は4連休になりました。旧シンセと出力レベルを合わせるため、FPGAシンセの出力レベルを上げます。左はデルタシグマDACのフィルタ/バッファアンプボードです。バッファのフィードバック抵抗を大きくしてレベルを調整しました。右はボードをFPGAボードのPMODコネクタに接続したところです。

FPGAシンセをラックに戻し、旧シンセとレベルを比べます。良くなりました。

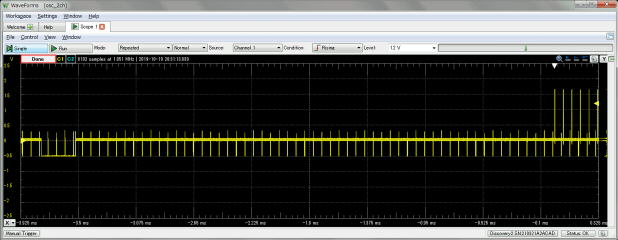

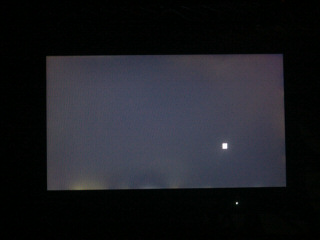

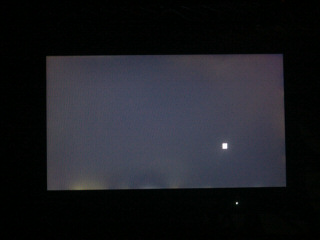

SBC8080ボードでTK80BS互換機を作る続きです。BSのビデオ信号を解析します。BSは横32文字、縦16文字のVRAMです。簡易ICEでVRAMにアクセスして左上にマークを出力します。出力した文字コードは80で8x8ビットの正方形です。

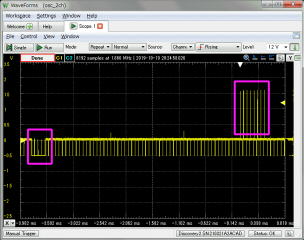

左の赤枠が垂直同期で、右がマークです。マークの部分は8本輝度が上がっています。この部分が8x8ビットの正方形の部分です。モニタプログラムでもVRAMにアクセスできますが、プログラムを作らずにマークだけを表示することはできません。簡易ICEなら簡単です。

切り割り込みパルスを拡大します。垂直同期の中にも水平同期信号が入っています。

垂直同期から左上マークまでの拡大波形です。

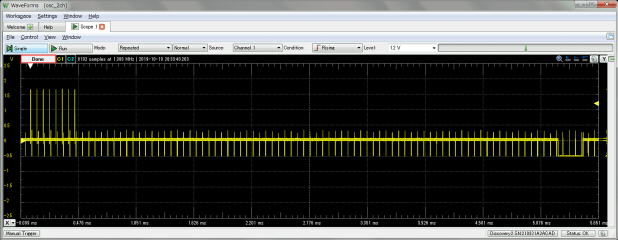

続いて、右下にマークを出力します。

右下マークから垂直同期までの拡大波形です。垂直同期の数を数えて同じ回路を作成します。これらの波形からBSのビデオ出力は飛び越し走査無しの信号と判りました。

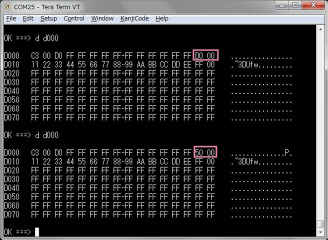

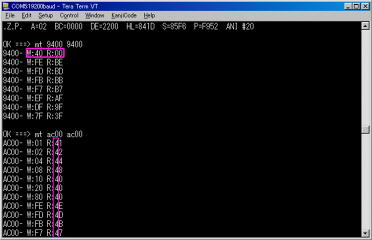

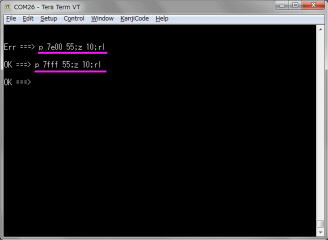

本家のTK80BSシステムはメモリエラーが発生しています。エラーは2エリアあり、1つ目が9400〜97FFと2つ目がAC00〜AFFFです。いずれも上位の4ビットがエラーです。メモリは4ビットの2114なので、エラーも上位、下位に分かれます。9400〜97FFはBSボード上、AC00〜AFFFは自作の12Kメモリボード上です。

12Kメモリボードはデバイスの2114を一度外して挿し直し、再確認しましたが、エラーは解消していません。

10月20日

先週のDCOで壊れていたCD4040です。レーザマーキングで読みにくいため、赤ペイントで染めてみました。”CD4040 HLF”でした。メーカ不詳です。

10月21日

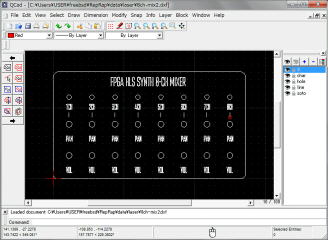

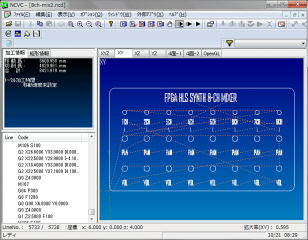

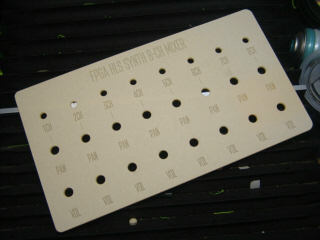

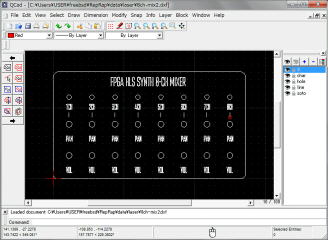

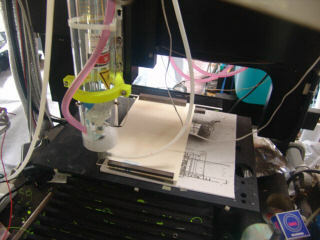

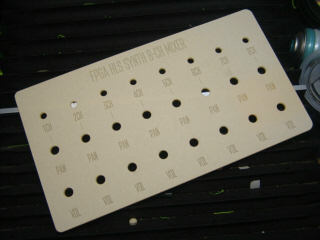

アナログシンセビルダーズサミットにFPGAシンセを出展する予定ですが、普段使っているミキサは大きく、運ぶのが大変なので、簡易ミキサを作製します。QCADでレタリング文字と穴、外形の図面を作成します。

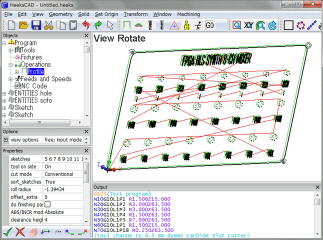

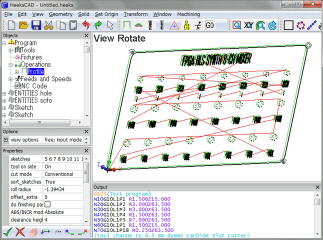

HeeksCNCでGコードに変換します。

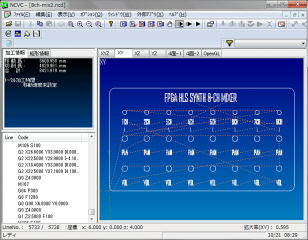

レザー加工用のデータに変換した後、NCVCで移動順序を確認します。

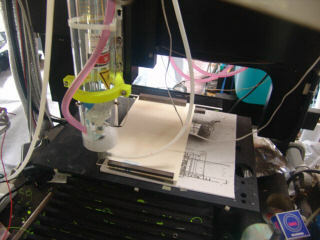

レーザ加工器で2mm厚のアクリル板から切り出します。2mmだと少し薄いですが、3mmだとジャックが固定できません。

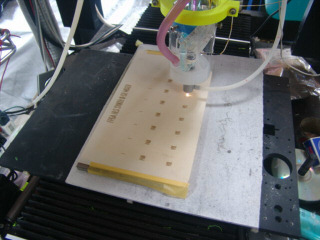

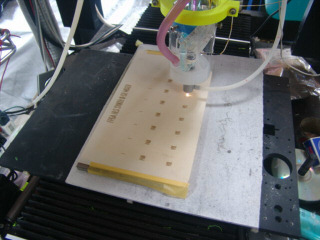

文字彫刻と穴開けが終了したところで、保護シートを剥がします。

作製したパネルにボリュームとツマミを取り付けて、配線を行いました。次回、オペアンプを追加します。

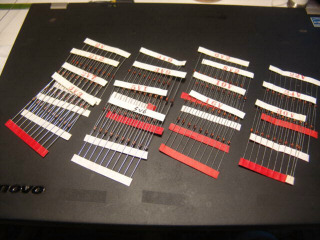

アマゾンで購入のツェナダイオードセットです。160本セットで404円です。

TK80BS互換機の続きです。新ROM/RAMボードに上記の3.3Vツェナダイオードを使ってSRAMメモリのバッテリバックアップ回路を追加しました。

10月22日

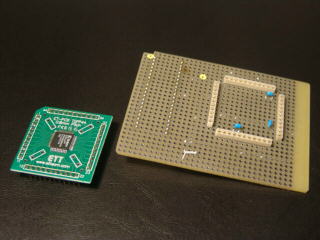

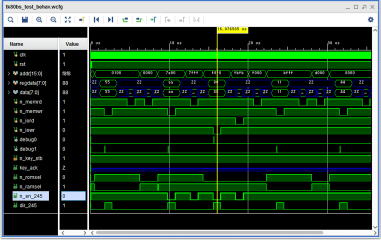

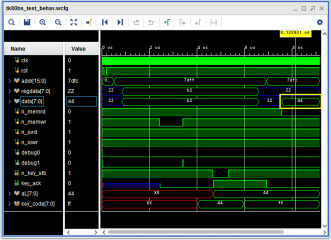

TK80BS互換機のVRAMとキーボードを実装するFPGA変換基板の動作確認をします。FPGA内にダミーのメモリとIOを1バイト実装し、Vivadoのシミュレーションで基本動作を確認します。

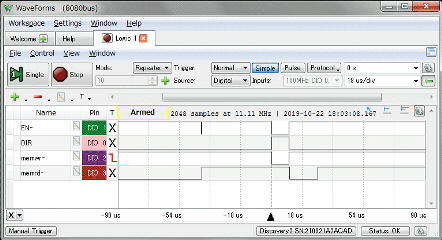

シミュレーションでは問題なさそうなので、FPGAのロジックをダウンロードして実機で確認します。はじめに2電源バッファの74LCXR163245の動作を確認します。

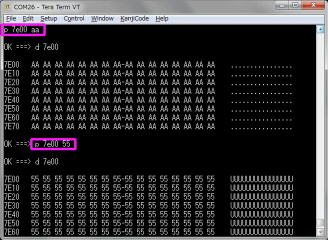

簡易ICEを介してFPGA内にダミーで実装

したVRAMエリア(7E00〜7FFF)を連続アクセ

スします。FPGAで生成している74LCXR163245のDIRとEN信号を確認します。問題なさそうです。

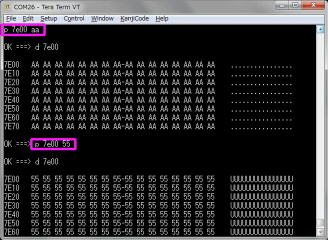

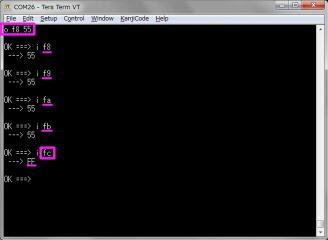

ダミーで実装

した、1バイトのメモリ(VRAM)とIO(TK80上の8255)をライト/リードして、正しくアクセスきることを確認しました。ダミーなので、所定エリア内の何処を読んでも同じ値が読めます。

10月26日

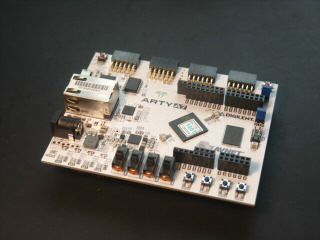

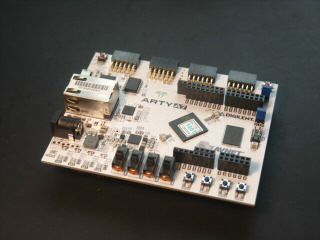

会社にFPAGボードのARTY(35T)を置いてきてしまったので、100Tにコネクタを半田付けして、TK80BS互換機の動作確認を進めます。

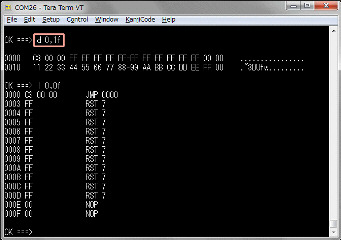

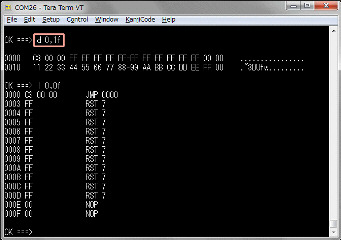

VivadoプロジェクトのデバイスをXC7A100Tに変えて、ROM/RAMエリアのチップセレクト生成ロジックを合成、インプリ後ダウンロードして新ROM/RAMボードの動作確認を行います。RAMは628128で、ROMは27C512です。ROMには予め、主な先頭番地にアドレスが判るように、JMP命令を入れておきます。

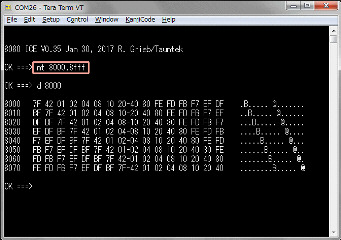

はじめにRAMエリアです。簡易ICEのメモリテストコマンドで下位の0100〜7BFF、上位の8000〜CFFFが正しく動作していることを確認しました。

続いて、ROMエリアです。簡易ICEで逆アセンブルして、D000(BASICのL2上位)、E000(BASICのL2下位)、F000(モニタ)の先頭番地付近が正しく読めることを確認しました。

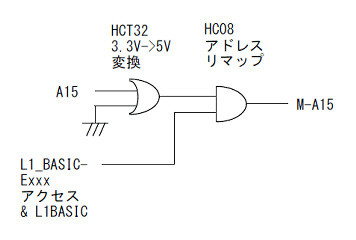

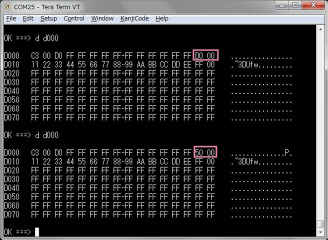

次にBASICのL1エリアです。FPGAボード上のスライドスイッチでBASICのLlとL2を切り替え、L1でDxxxをアクセスすると、5xxxにリマップします。ちょっとアドレスを間違えていて、L1のアドレスはExxxでした。次回、6xxxがExxxにリマップされることを再確認します。

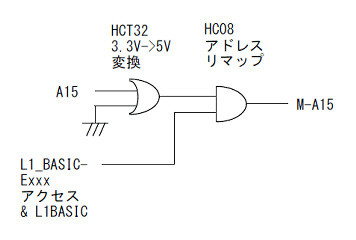

FPGAの外部に実装したアドレスリマップ回路です。A15をL1のBASIC設定とExxxのアドレスデコードのAND信号で外部ロジックを使ってマスクしているだけです。これにより、L1のL2のBASICの重なっているExxxを6xxx番地に移動することができ、2つのBASICとモニタが1個の27C512に入ります。

10月27日

8チャンネル簡易ミキサにオペアンプを追加して、電源、ミキサ出力の配線を追加しました。アナログディスカバリを使って基本動作確認を行いました。次回、FPGAシンセから±5Vを引き出し、動作確認を行う予定です。

10月28日

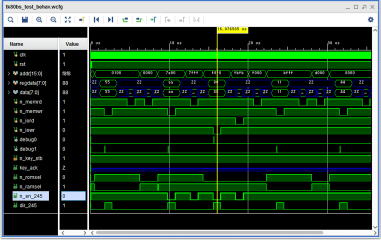

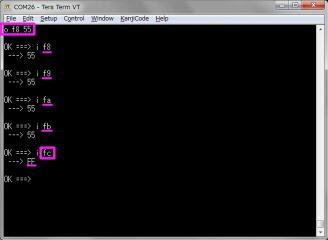

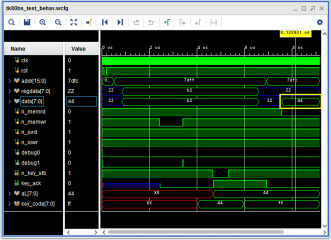

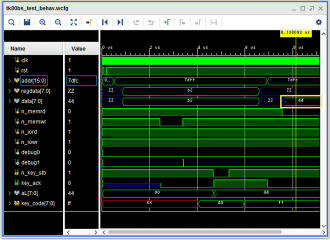

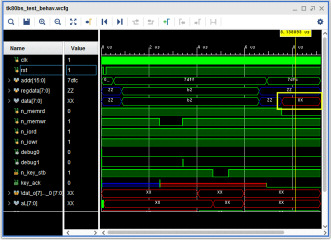

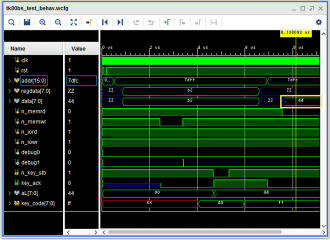

アパートでの作業です。以前に8255のIPをVivadoのシミュレータで動作確認しましたが、ビヘイビアシミュレーションではモード1でポートAに入力したキーコードとSTB/RDYのハンドシェイクが正常動作しています。黄色枠にポートAに入力したキーコード44が出力されています。

しかし、合成後シミュレーションではデータバスに出力される黄色枠のキーコードがXXの不定になっています。

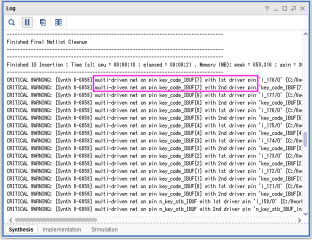

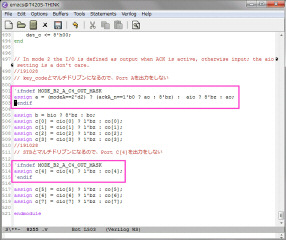

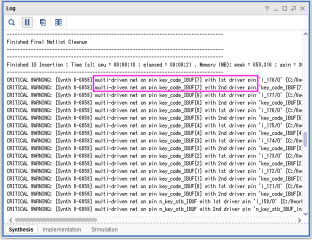

合成時ログを確認すると、ポートAとポートCの4ビットがマルチドリブンになっていると、ワーニングが出ています。

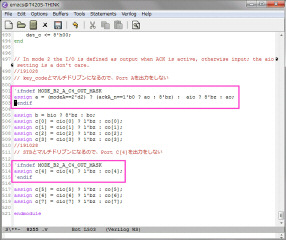

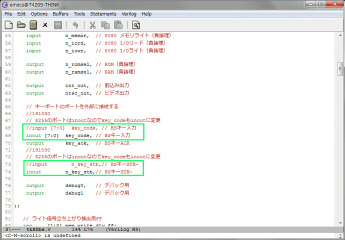

8255のIPのソースコードを確認します。キーコードを入力しているポートAの8ビットとSTB信号を入力するポートCの4ビットを条件付きで出力している部分を暫定的に削除してみます。

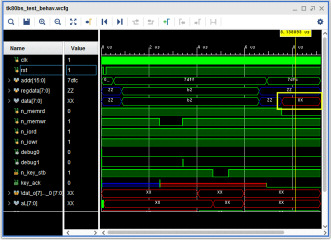

インプリ後シミュレーションです。正常動作になりました。上記の修正では動的モード設定に対応できないですが、とりあえず動作しています。マルチドリブンになる部分が判明したので継続して調査します。

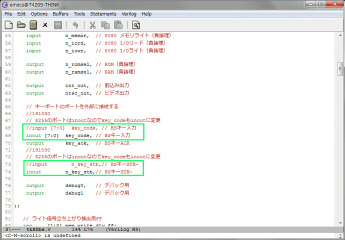

10月29日

マルチドリブンの続きです。8255のIPのポートA〜Cは設定により入出力が変化するinout属性です。それに接続しているkey_codeとkey_stb信号もinout属性にする必要がありました。緑枠のように修正して、IP側のソースは元に戻してもマルチドリブンは解消されました。

10月30日

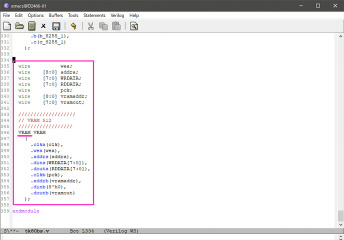

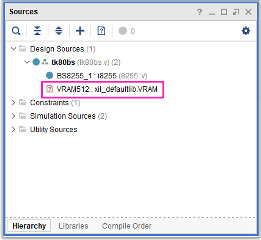

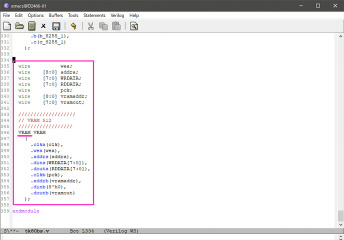

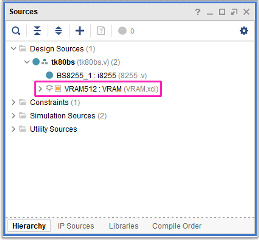

会社の空き時間にVRAMを実装します。書籍のFPGA大全の文字表示のページを参考に、トップモジュールに赤枠のDPMを使ったVRAMを追加しました。

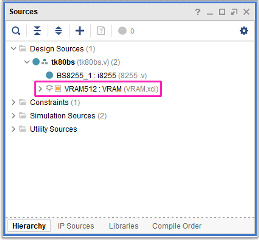

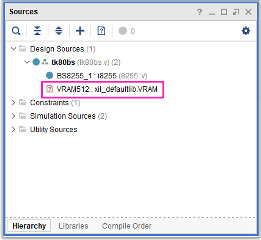

ソースを修正すると、プロジェクトが自動的に更新され、ソースペインのVRAMに?マークが表示されます。VRAMの本体が無いという表示です。

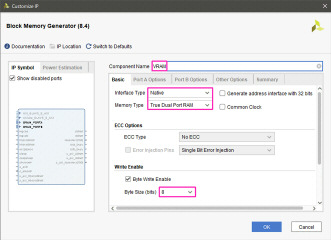

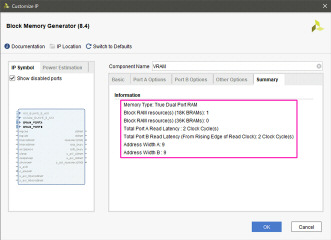

IP

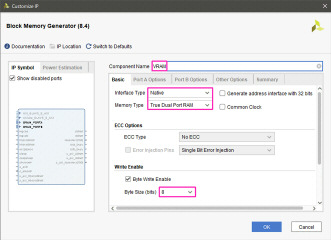

カタログのブロック・メモリ・ジェネレータのメモリ・ストレージ・エレメントから、RAM&ROM&BRAMを選び、各設定を行います。コンポーネント名をソースコードに合

わせて”VRAM”に変更し、インターフェースを”Native”に、タイプを”Ture Dual Port RAM”に設定します。ライトイネーブルに

チェックを付けて、サイズを”8”に設定します。上記でコンポーネント名をソースコードに合わせて変更しないと、後で?マークが消えないので注意します。

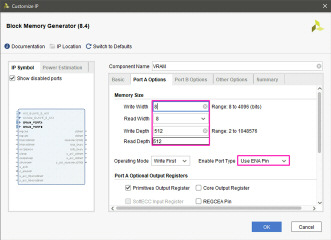

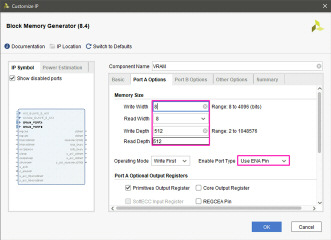

ポートA(CPU側)の設定はバス幅を”8”に、深さを”512”に設定します。

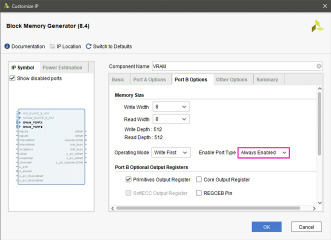

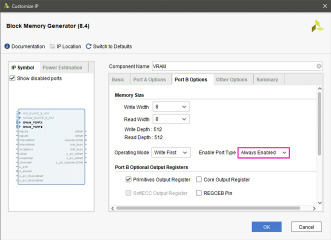

ポートB(ビデオ側)は、カウンタで常時読み出しなのでイネーブルを”Always Enabled”に設定します。

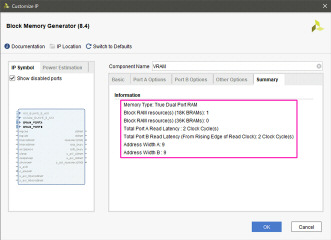

設定の確認です。18KのBRAMが1つ使われ、アドレス幅が9(512バイト)になっていることを確認します。

”Out of Context per IP”と”Genetate”を実行しするとソースペインの?マークが消えます。その後、IPのソースディレクトリにある”VRAM.veo”ファイルと追加したVRAMのIPへの接続部の信号リストが一致しているか確認しておきます。

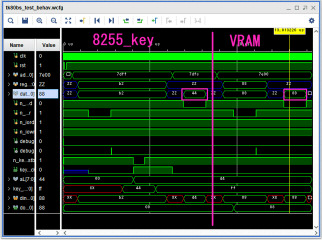

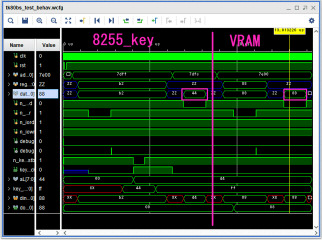

とりあえず、CPU側のみデータバスに接続して、合成、インプリ後、シミュレーションを行います。テストベンチは8255への1文字入力と、その後、VRAMに”88”を書いて、同じ番地を読みます。キーコード”44”とVRAMの”88”がデータバスに

出力されています。CPU側は良さそうなので、次はビデオ側を作成する予定です。

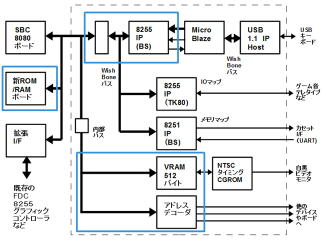

青枠内のアドレスデコーダを含むROMとRAMの実動作とVRAMのCPU側のシミュレーションの確認ができました。