TK80/BSの

シンセシステムを復活/拡張したい〜

その45

SBC8080ボードを使った

TK80BS互換機の作製

TK80BSの修理

2019年

2019年

11月16日

TK80BS

互換機の続きです。最終的にはUSBキーボードを接続する予定ですが、その前に、本物のBSのキーボードを使ってFPGAの8255の動作確認を行います。キーボードに載っているコントローラはuPD364ですが、WEB上でデータシートを見つけることができませんでした。

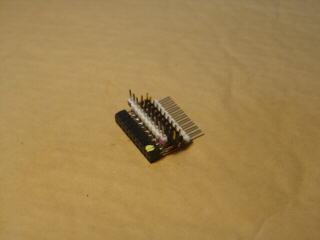

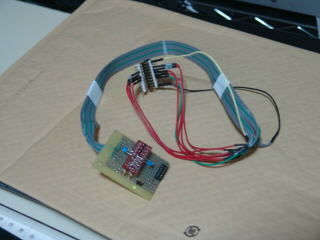

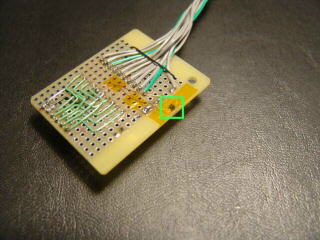

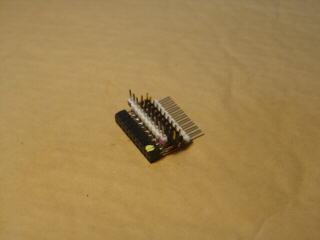

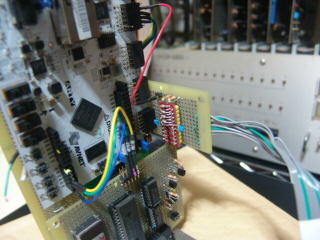

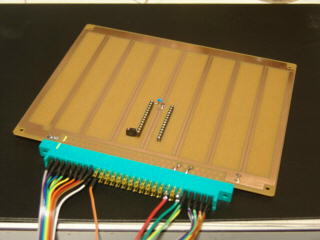

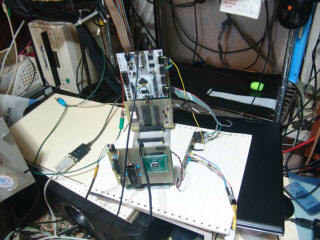

キーボードのコネクタのピン配置を調べるために、分岐コネクタを作製しました。

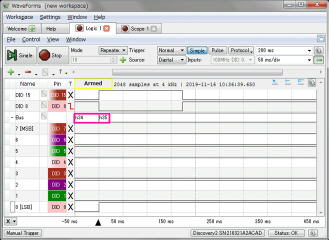

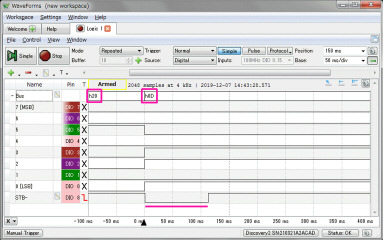

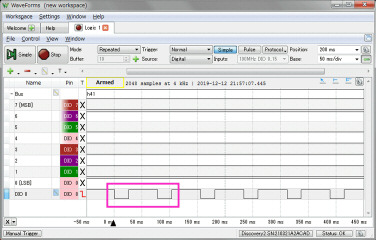

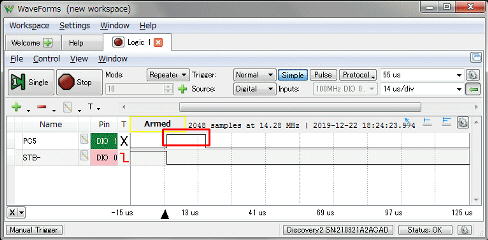

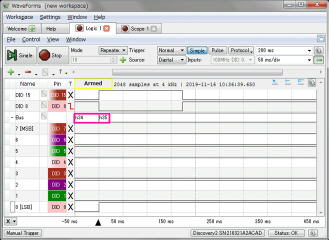

アナログディスカバリのロジアナで分岐した信号を調べます。キーボードの出力する8ビットデータとSTB−信号(ストローブ)の位置が判りました。正論理のSTB信号も出ていました。モード1で出力されるIBF信号(ACK)はコネクタには出力されていませんでした。また、本体から5V以外に12Vと−5Vの電源も供給さ

れています。右の波形はピン配置が判明した後で’4’の次に’5’を押したときです。正しいASCIIコードになりました。

マルツで購入したD−SUBの25ピンコネクタと3.5mmのプラグとジャックが来ました。D−SUBはROMライタのパラレルケーブル用です。

TK80BS互換機用のFPGAボードを100Tから35Tに変更し、設定を変更してインプリし直しました。

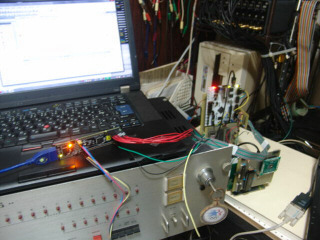

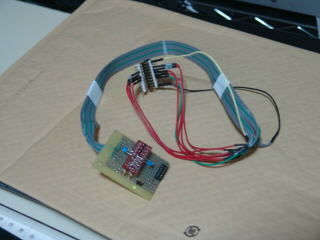

BSのキーボードは12Vと−5Vも必要なようなので、電源は本家のTK80BSから供給し、キーコードとSTB−信号をFPGAボードに接続するケーブルを作製しました。信号線のレベルを5Vから3.3Vに変換し、PMODコネクタに接続できるようにします。

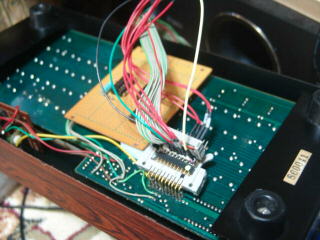

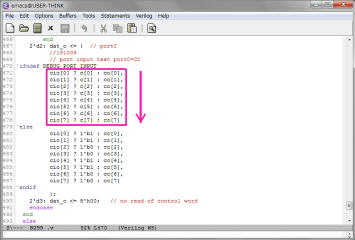

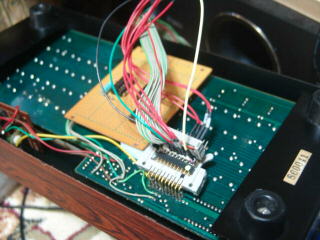

分岐したキーコードとSTB−信号をFPGAボードに接続し、8255の動作確認を行いましたが、キーは入力できませんでした。原因はポートCの5ビットに出るはずのキーが押されていると

いうIBF(Input Buffer Full)が出力されないためです。ポートCの3ビットに出力されていました。

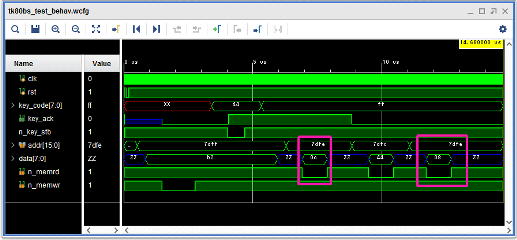

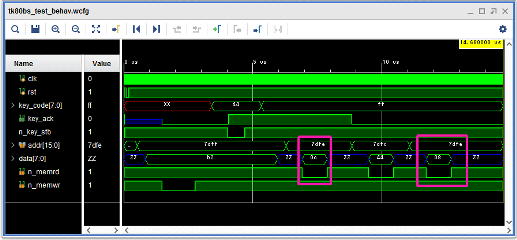

Vivadoのシミュレータで確認します。キー入力でポートCが0Cになり、ポートAのリードでポートCが08へ変化しているので、IBFは3ビット目に出ています。

11月17日

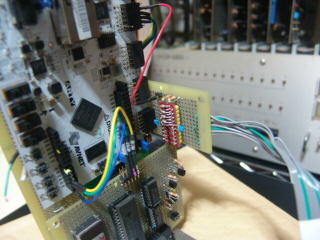

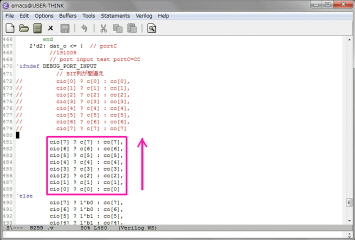

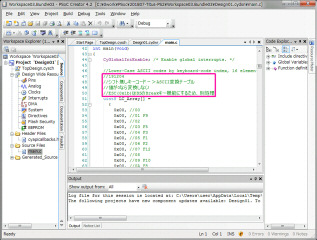

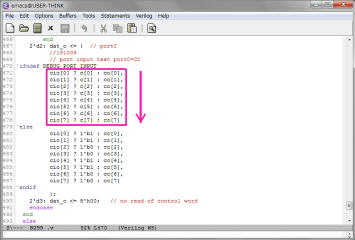

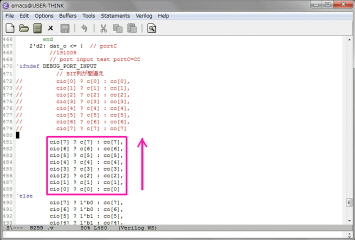

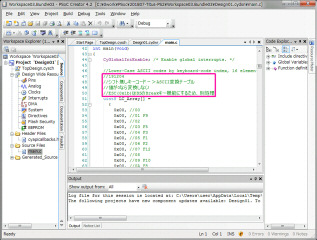

8255のIPのVerilogのソースコードを確認したところ、内部レジスタをポートCに出力しているビット連結が上位下位で逆になっていて、間違えています(笑)。以前に動作確認のために埋め込んだデバッグコードも、そのまま間違えていました。

早速、ビット列を逆して修正しました。この8255のIPはGitHubにあったもので、動作を保障したものではないです。

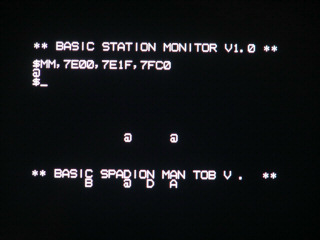

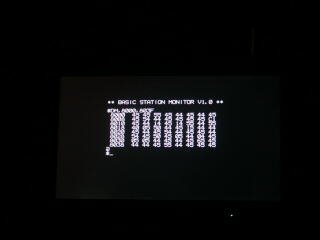

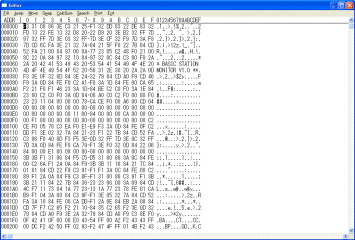

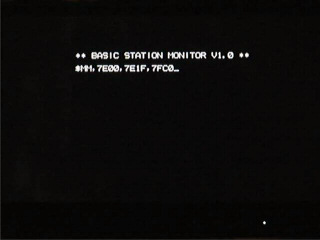

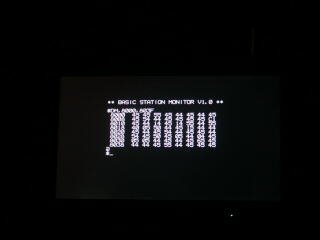

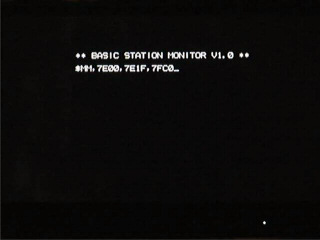

修正後、モニタへキー入力ができるようになりました。ただ、3回に1回くらいの割合で一度に2文字入力されることもあり、調査が必要です。下はメモリダンプを実行したところです。

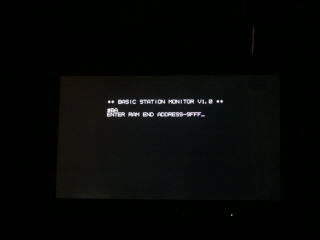

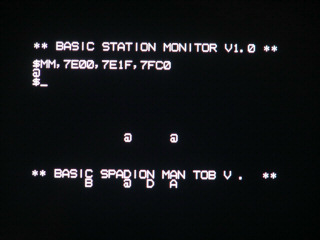

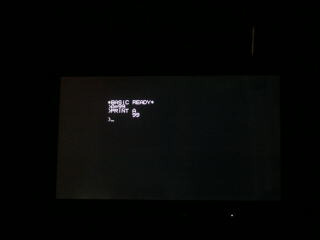

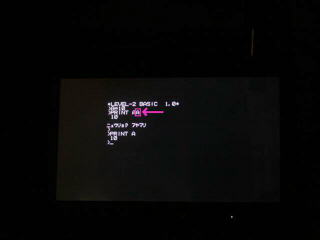

続いてBASICの動作確認です。FPGAボードのスライドスイッチをL−1側に設定にして、BASICを実行してみます。エンドアドレス入力のメッセージが長いのでL−1が動作していることが判ります。アドレスの6000をE000にマップするリマップ機能が正しく動作しています。

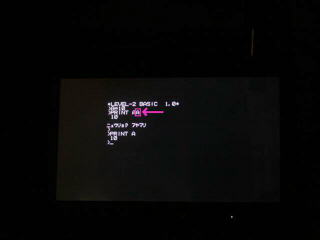

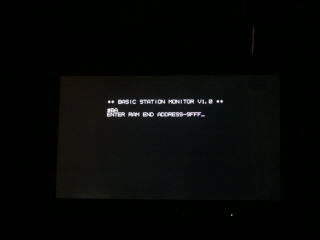

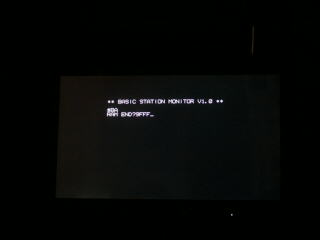

続いて、スライドスイッチをL−2側に設定して実行してみます。エンドアドレス入力のメッセージが短いのでL−2が動作していることが判ります。こちらも正常に動作しているようです。ただ、偶にVRAMに不正な書き込みが発生します。右の赤矢印の’A’は不正書き込みです。こちらも調査が必要です。

11月20日

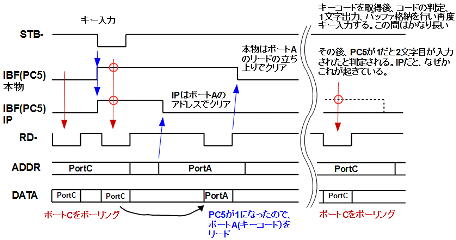

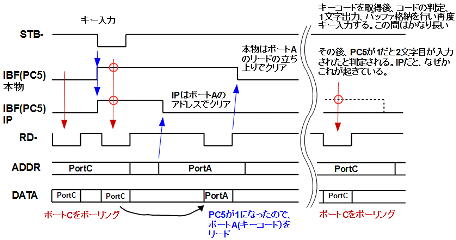

キー入力が2回入る件です。アパートで実機が無いので、机上での考察です。以前にも書きましたが、本物の8255とIPの8255ではPC5のIBF(ACK)が0に戻るタイミングが違いました。これによってキーが2回入るか確認するためタイミング図を作成しました。キー入力の判定はCポートをポーリングして、5ビット目が1になることで行います。キーが押されていればループを抜け、ポートAを読んでキーコードを取得します。IBF(ACK)はポートAを読むことで0に戻りますが、本物の8255ではRD−の立ち上がり、IPの8255ではポートAのアドレス確定です。これはIPの8255にはRD−信号が接続されていないからでした。ポーリングのループを抜けた後はIBFの状態は参照されないので、やはりIBFが0に戻るタイミングは不具合とは無関係のようです。

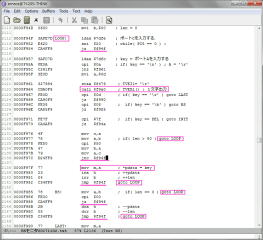

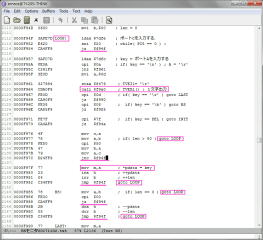

以下はモニタの文字入力関数の逆アセンブルリストです。赤枠のgoto LOOPの所がポーリング先頭へ戻っているところです。キーが押されてポーリングのループを抜けた後、キーコードの種別判定、VRAMへ1文字出力、バッファへの書き込みを行っています。次のポーリングまでは、かなりのステップ数があり、キーを1回押したのに2回入るのは、2文字目のポーリング中にPC5が1になっているからで、ケーブルや5V−>3.3Vレベル変換回路などハードウェアの不具合かもしれません。

11月23日

TK80BS互換機用のUSBキーボードをアマゾンで購入しました。キー機構はメンブレンですが、キーストロークの長い物を選びました。また、FPGAにUSBホストを組込むのは時間が掛かりそうなので、念のためPS/2付きを購入しました。

PS/2の延長ケーブルもいっしょに購入しました。

キー配列を比べてみます。BSはJISキーなので、記号やカナキー(使わないですが)の位置も日本語キーボードと同じです。ただ、ファンクションなどが余分に付いています。

ケーブルが長すぎるので、一度分解して短くしました。

先週キーボードのコネクタピン配置で未調査だった、Breakキーの信号を調べ始めると、BSの調子が悪くなりました。簡易ICEでモニタROM領域を調べると、モニタROMの内容が正しくないです。早速、ROMを取り出してROMライタで読み込みます。マスクROMの型番はuPD2332Cですが、アダプタで2732に変換して読み込みます。

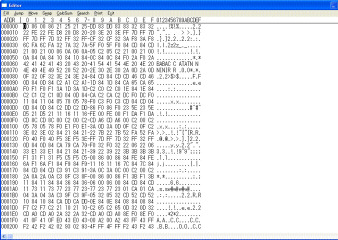

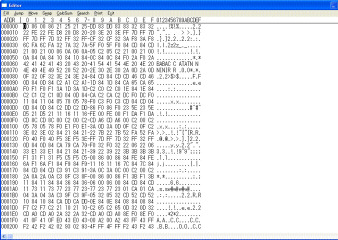

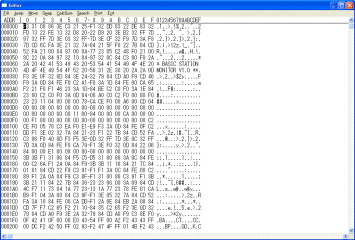

左が取り出したモニタROMの先頭で、右が予備のROMのダンプです。明らかに左側はアドレスが異常です。

11月24日

モニタROMは予備に交換して復帰しましたが、だいぶ前に直ったはずの上位12KバイトのRAMエリアは全てFFが読めます。一度分解して、再度組み立てましたが、直りませんでした。また、Breakキーも効かず、モニタが割り込みモードに入れません。

11月30日

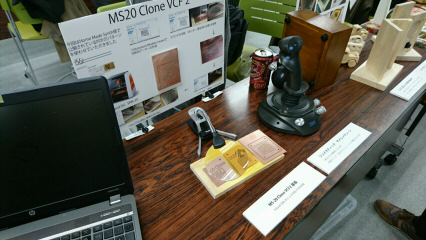

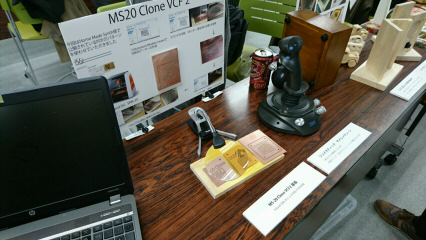

友人S、元同僚Yさんとアナログシンセビルダーズサミットに参加してきました。

FPGAシンセを出展しました。移動中の故障や忘れ物も無く、ちゃんと動いて良かったです。ここに前回も含めて出展資料のページを作りました。

他の出展を紹介します。完成度の高いアナログポリフォニックシンセ。ロータリエンコーダが6個に7セグ表示もあって、FPGAシンセと似ています。

S端子ケーブルでパッチをするユーロラックシンセ。

特殊な操作形状の電子楽器ウダー。

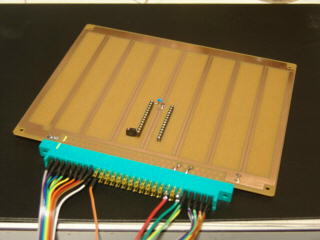

ローランドのCNCルータを使ったVCFの切削基板の展示。

12月1日

土曜の夜はアナログシンセビルダーズサミットの機材をガレージに運びました。TK80BS互換機の続きです。本家BSのキーボードが壊れても良いようにBSキー

ボード互換を作る予定です。キー入力のヒストリ機能なども実装したいと思います。これを作製すれば本家BSにも互換機にも使えます。とりあえずPS/2で接続します。だいぶ前に購入してあったPSoC5LPでPS/2をASCIIコードに変換するWEBページがありました。クリックするとサイトに飛びます。

キーボードのUSBコネクタにPS/2変換を付けて、アナログディスカバリで信号を測定します。

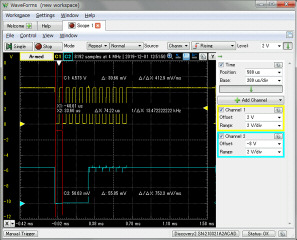

データ、クロックとも4.7Kでプルアップすると、キーボード側から送信が始まります。PS/2キーはキーボード側がクロックを出力します。下はキーを離したときのF0コードです。上からクロック、データです。クロック周波数は約13.4KHzです。

前回のキーが2回入ってしまう不具合です。本家BSのキーボードを繋いで再確認します。データの8ビットは5V<−>3.3V変換ボードで電圧変換していますが、STB−信号は抵抗で分圧しているのが不具合の原因のようです。次回、もう少しちゃんとした電圧変換で確認してみます。

アナログシンセビルダーズサミットから戻ったFPGAシンセの動作確認を行いました。問題なく動作しています。

12月4日

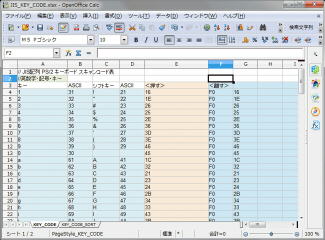

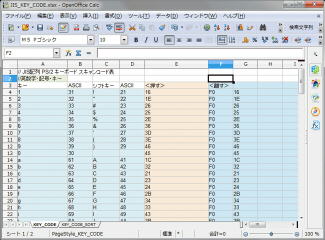

上記のPSoC5LPを使ったPS/2−>ASCII変換は英語キー用なので、日本語キーのキーコードを表にしました。クリックするとオープンオフィスCALCのobsファイルをダウンロードします。

12月7日

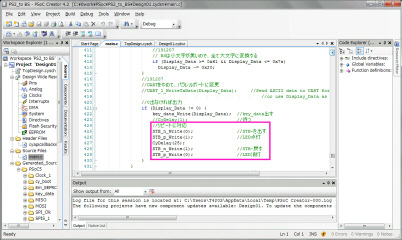

上記のPSoC5LPを使ったPS/2−>ASCII変換のキーテーブルを日本語キーに変更しました。

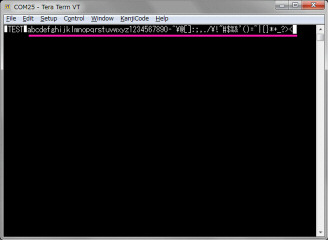

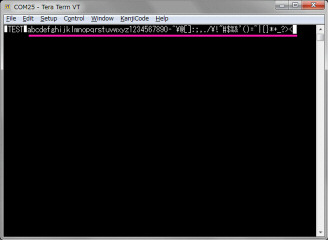

UART出力をTeraTermに接続して動作確認を行います。

先頭で”TEST”を出力し、後の文字はキーボードからの入力です。一通り、キー入力ができることを確認しました。

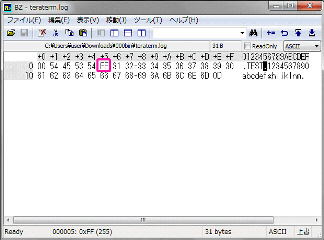

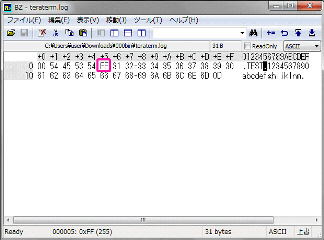

TeraTermのバイナリログです。”TEST”の後にFFが1回出ていますが、それ以外は正常動作しているようです。

本家TK80BSの上位12Kメモリの不良解析と新作のために通販でユニバーサル基板とコネクタを購入しました。

USB−MIDIパラレル変換と同じ大きさのグレー色のケースも購入しました。USB−MIDIパラレル変換のベロシティのパッチ用です。フロントパネルをつや消し黒で塗装して、レーザでレタリングする予定です。

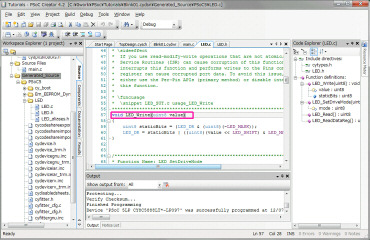

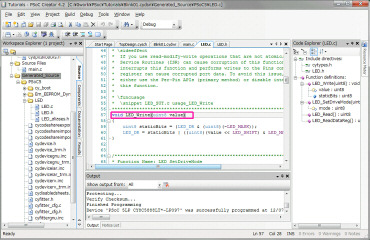

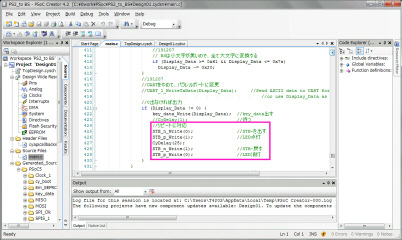

PSoCは普通のコントローラと違い、初めからGPIOが用意されているわけではありません。ここの”PSoCを始めましょう(Lチカまで)”を参考にして、勉強します。GPIOを使う場合の基本的な流れは、デザイナ上でGPIOを使った回路図を作り、ピンアサインを行った後、”Generate Application”を行なって、GPIOのAPIを含んだソースを生成させるという手順です。以下はLEDと名前の付いた1ビットのGPIOの出力関数”LED_Write”です。

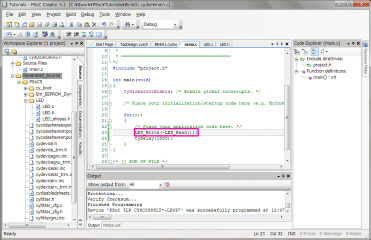

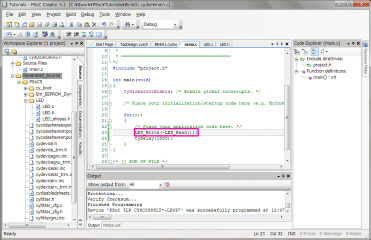

以下は”LED_Write”を呼んでいる部分のコードです。ちょっと慣れないと難しいです。

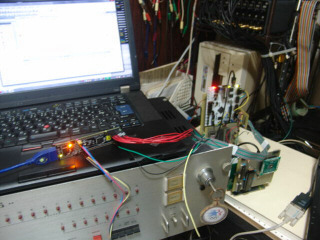

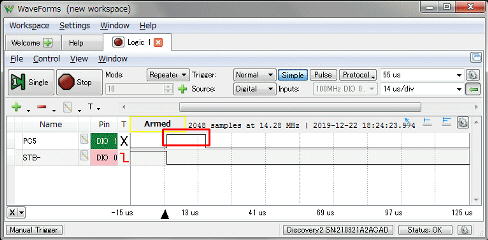

上記のページを参考に、PS/2−>ASCII変換のUART出力の部分を8ビットパラレルとSTB−信号に変更します。動作確認のため、アナログディスカバリのロジアナを接続します。

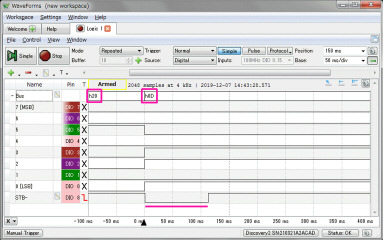

キーを押したことをキーコードの1バイトで、離したことをF0+キーコードの2バイトで検出する普通のアルファベット、記号と数字は問題なく動作しているようです。以下はスペースの後にEnterを押したところです。現状のコードのままでは矢印キーなど上の条件に合わないキーは正常動作しません。少なくとも無効なキーは無視される必要があります。

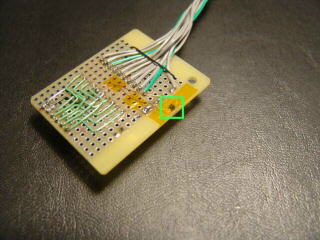

STB−信号のレベル変換を抵抗分圧から、ロジックに変更しました。会社の机の中にSN74LV1T125が余っていたので、これを使いました。SC70パッケージなので小さく、配線が難しいです。LVデバイスは3.3V電源で5Vトレラント入力です。データシートはここにあります。

12月8日

上記のPS/2キーをパラレルに変換したキーボードを互換機に接続して動作確認します。途中でキーが入らなくなります。PSoC側のプログラムの不具合のようです。アパートに持ち帰って確認します。

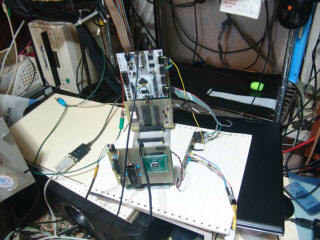

ユニバーサル基板に62256のRAMを載せて上位12Kバイトメモリを新作します。とりあえず62256用のソケットを実装したところです。他にアドレスデコーダも必要です。本家TK80BSは分解が面倒なので、互換機にコネクタを接続してテストします。

12月12日

アパートにキーボードとPSoC一式を持ってきました。途中でキーが入らなくなる件をデバッグします。単にコードが間違えていました(笑)。

BSのキーは大文字しか無いので、小文字が入力された時は大文字になるように変換し、追加でキーリピートに対応させました。

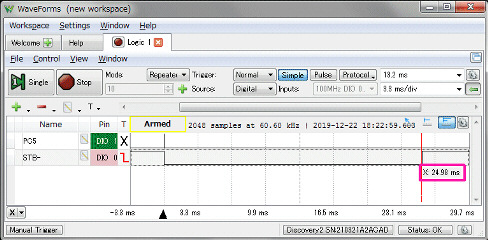

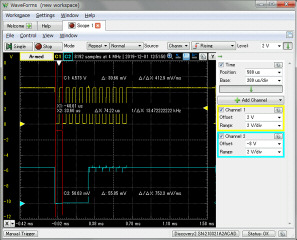

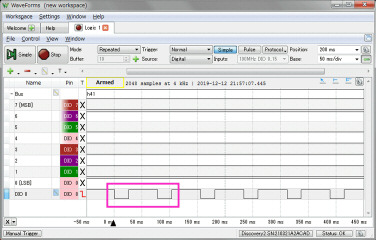

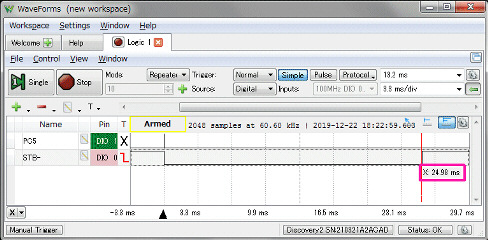

PCのキーボードはキーを押し続けたとき、キーリピートまでの時間が500mSec、キーリピートの間隔100mSecがデフォルトです。STB−信号の幅をキーリピート間隔の1/4の25mSecにしました。以下は’A’を押し続けて、リピート状態になっているパラレルデータとSTB−信号の波形です。

12月17日

アパートでリピートに対応させたPSoCのキーボードをTK80BS互換機に接続して動作確認しました。単体では連続動作させても問題ないですが、FETを使った5V−>3.3Vレベル変換をキーコード出力ポートに接続するだけで、PS/2のシリアル入力の部分が誤動作することが分かりました。互換機側に接続しなくても、現象が起こり、原因は不明です。この週はトライトンの整備と移動で作業を中断しました。

12月21日

TK80BS互換機用キーボードの部品を秋月から購入しました。3.3Vの3端子レギュレータ、5V−>3.3Vレベル変換の部品とPSoC5LPの評価ボードです。

プラスチックケースも購入しておきます。

PSoCはVDDIOがグループ分けされているので、BSに接続するデータ線とSTB−信号のIO電源を3端子レギュレータを使って3.3Vにして5V−>3.3Vレベル変換基板を使わないようにしました。各VDDIOはパターン接続されているので、VDDIO2のパターンをカットして3.3Vに接続します。単体では連続キー入力しても問題ないと思ったのですが違っていたようで、長時間連続してキー入力を行うと、SPIスレーブのステータスレジスタがエンプティのままになって、PS/2キーボードからのデータが受信できなくなるようです。継続して調査します。

12月22日

次はFPGA内のキー入力用8255のIPが10回に1回くらい無反応になる件です。下は正常動作している時のSTB−信号とIBF(ACK)信号です。PSoCがPS/2キーボードからキーコードを受信し、STB−信号を25mSec出力し、ポートCの5ビットにIBF(ACK)が細いパルスが出力されます。IBFが1になるのは8255のロジックでSTB−の立下り検出です。IBFが0戻るのはCPUがIBFをポーリング後、キーコードのポートAのデータを読んだときです。

正常動作している時のポートCの5ビットにIBF(ACK)拡大波形です。無反応のときは赤枠のIBFが出力されないことが分かりました。CPUはIBFをポーリングしてキー入力を判断しているので、このIBFが出力されないと、当然無反応になります。8255のIP内に不具合があるようです。

次はFPGA内のVRAMに不正書き込みが起きる件です。下はBSのモニタを起動し、メッセージが出力された後、MMコマンドでメッセージをVRAMの下から2行目の7FC0番地にムーブした時の7秒ほどのmpg動画です。FPGAボード上のスイッチを使ってMMコマンドとほぼ同時にCPU側のアクセスを禁止しているので、FPGA内で不正な書き込みが勝手に起っていると思われます。FPGAのブロックメモリを使ったデユアルポートRAMなので、ビデオ読み出し側にもライトイネーブル端子があります。これはディゼーブルにして読み出し専用に設定してあります。不思議です。

MMコマンド後、長時間放置したVRAMの表示です。不正な書き込みが増えていきますが、VRAMの下側に限られているようです。継続して調査します。