TK80/BSの

シンセシステムを復活/拡張したい〜

その57

midiconvプログラム、HLSのDMA

2020年

2020年

9月3日

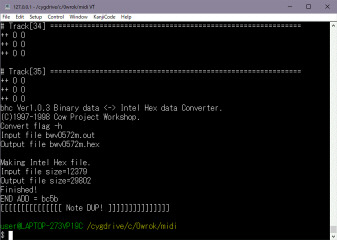

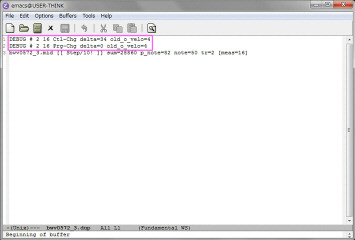

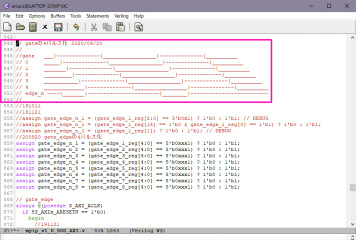

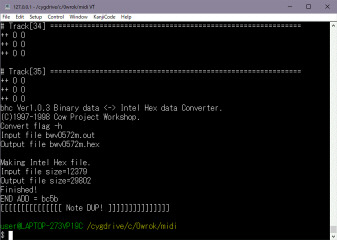

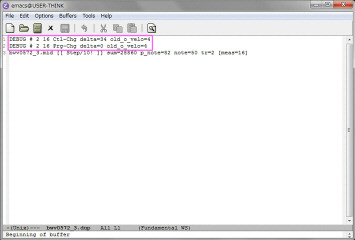

midiconvの続きです。ガレージ環境でデータの先頭に無効データ2バイトが余分に入って動作不良だった、midiconvプログラムをアパート環境で実行してみます。プログラムとデータはガレージと同一です。

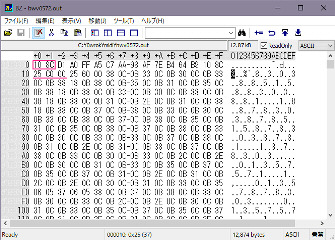

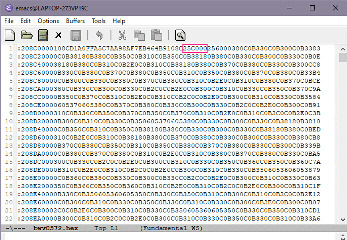

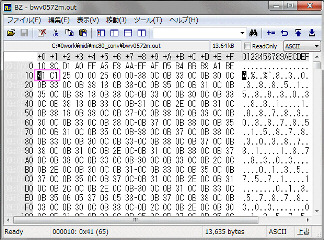

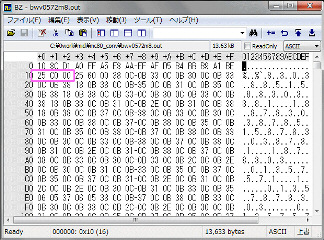

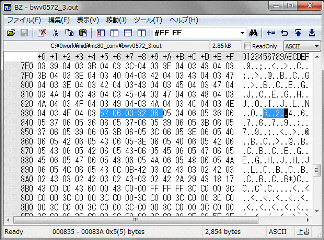

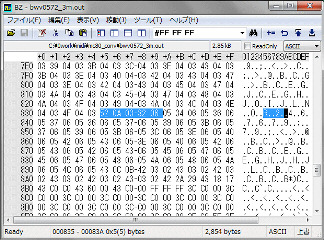

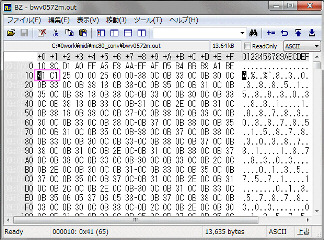

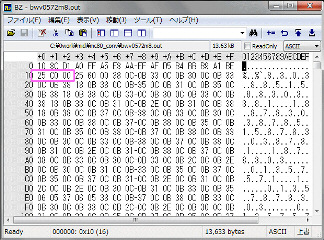

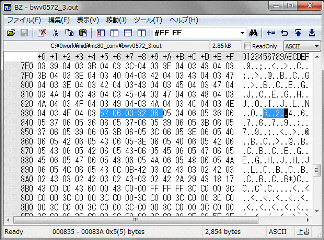

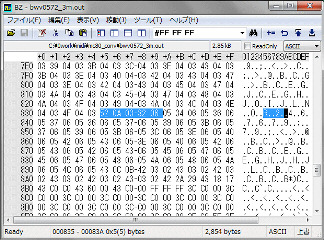

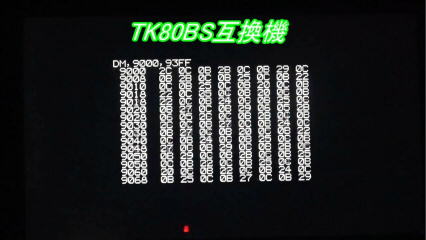

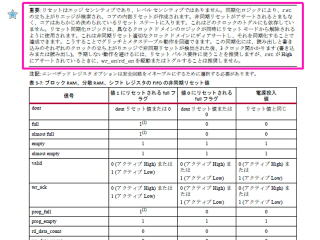

変換後のバイナリデータです。8c00〜8c0fが8チャンネル分の先頭アドレステーブルで8c10が1チャンネルデータの先頭です。音程が25で音長c0、ゲート長0で、無効データは無くなぜか正常です。

続いてインテルHEXのデータです。正しくHEXファイルに変換されて、こちらも正常です。次回、ガレージの環境で再確認します。

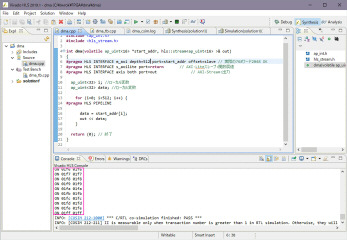

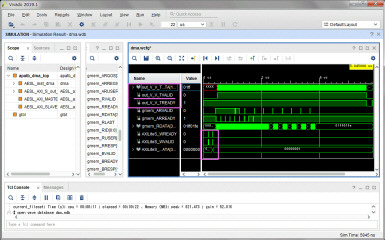

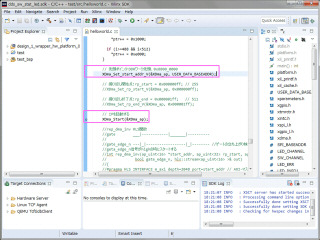

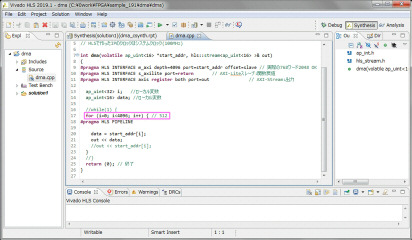

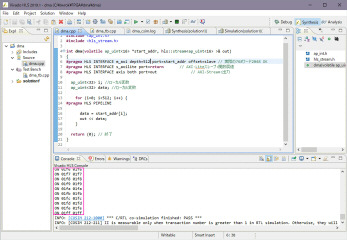

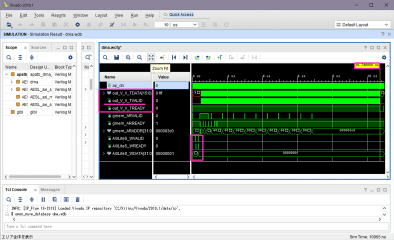

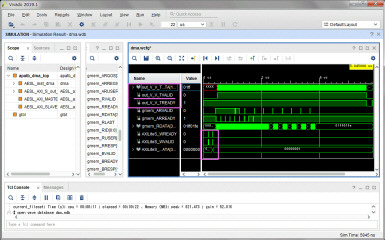

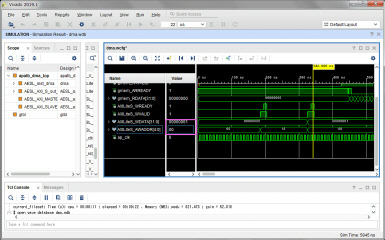

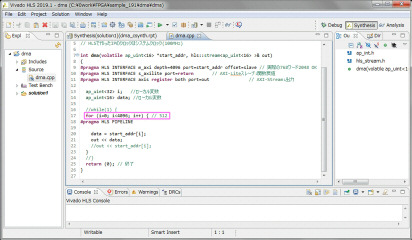

HLSのDMAの続きです。C/RTLコシミュレーションします。先週と同じく、for文のPIPELINE付きです。テストベンチのprintfの出力は正常に見えます。

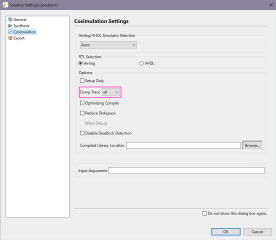

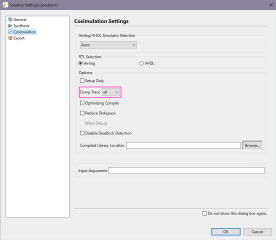

C/RTLコシミュレーション時に波形シミュレーションを出力して、確認します。設定でDumpTraceをFullにします。

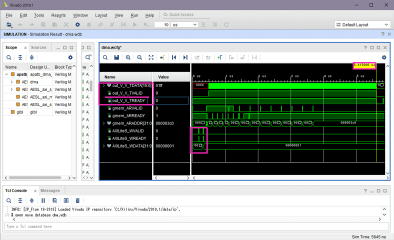

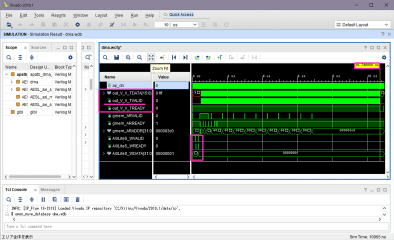

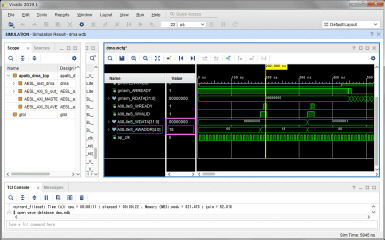

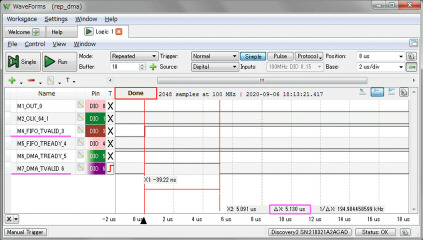

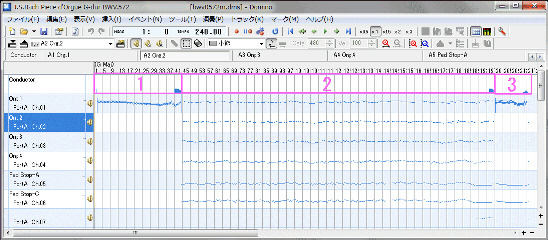

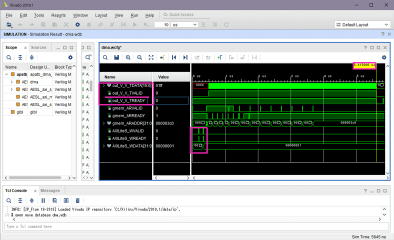

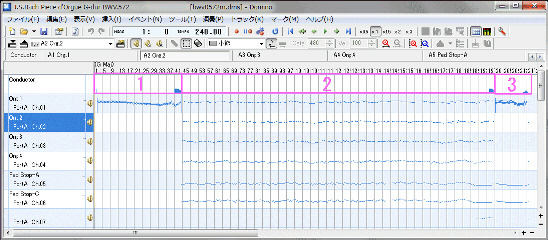

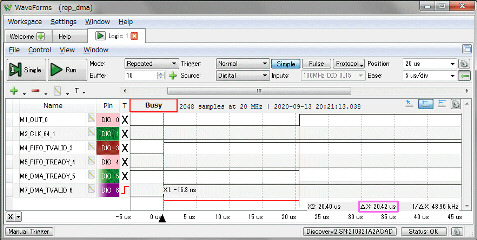

波形ボダンがイネーブルになるので、クリックするとVivadoが起動し、波形が表示できるようになります。左下にAXI−Liteでレジスタ設定があり、その後、gmem(メモリ)からデータが読み出せれて、out_V(AXI−Stream)のTVALIDが常時HIGHになっています。全体の長さは約5.6uSです。実機のFPGAのTVALIDテストポイントはLOWのままだったので、結果が異なります。

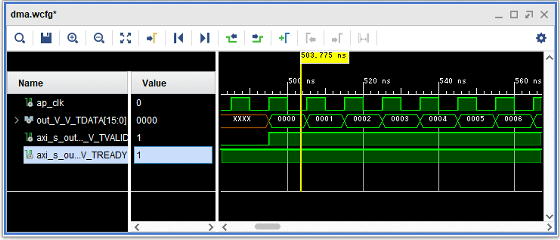

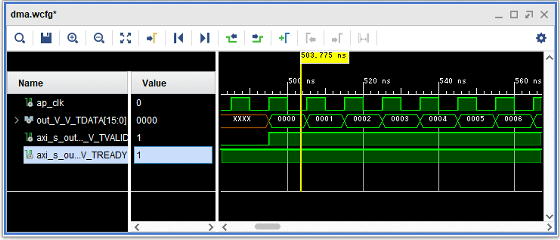

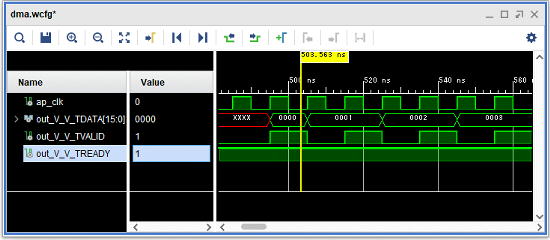

out_V(AXI−Stream)を拡大してみます。1クロックでインクリメントデータが出力されています。

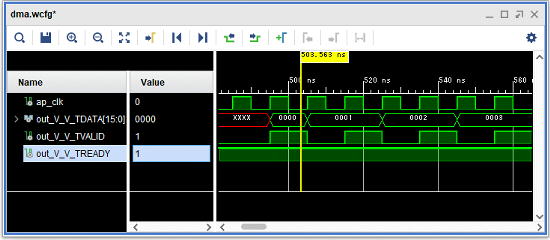

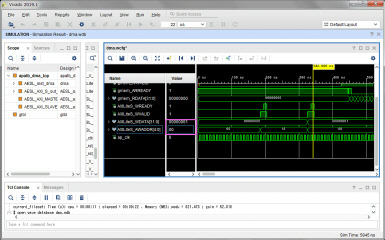

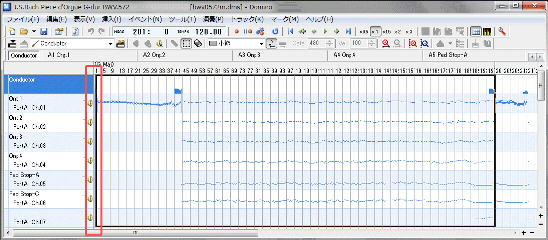

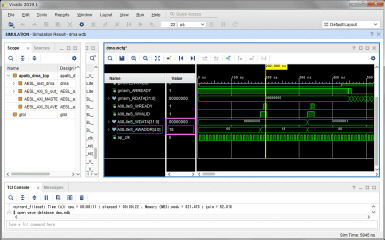

HLSのfor文のPIPELINEを取って再度、C/RTLコシミュレーションします。TVALIDが交番しています。全体の長さが5.6uSから10uSに長くなっています。

out_V(AXI−Stream)を拡大してみます。2回目から2クロックでインクリメントデータが出力されています。PIPELINE指定を取った効果が表れています。

9月6日

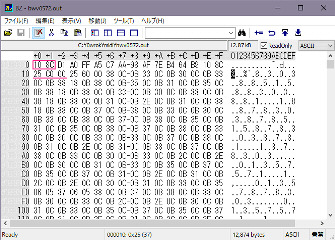

この週末は日曜のみのガレージ作業です。先週からの続きのmidiconvプログラムです。ガレージ環境では下の赤枠の2バイトの無効データが入っています。

色々調べて、原因がわかりました。2バイトの無効データが入るデータは8チャンネルのmidiデータでした。

アパート環境では2バイトの無効データは無く、赤枠が3バイトの1音分のデータです。

正

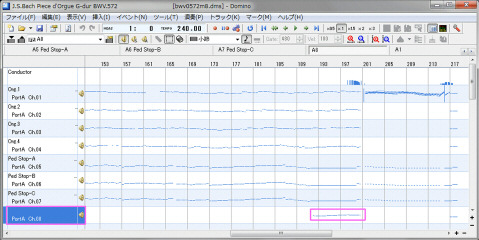

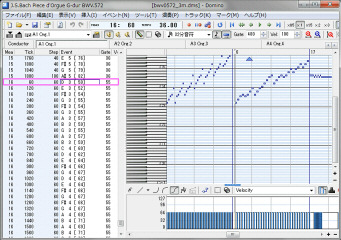

しく変換できる方は下のように7チャンネルまでのデータでした。5と6チャンネルが同じ音程データなので、6チャンネルを削除して、7チャンネルにしたのが

このデータです。これはmidiconvプログラムの不具合です。8c00〜8c0fはスタートテーブルですが、変換が終了しないと各チャンネルのスタート番地が定まらないため、データの変換後にテーブルとデータを連結しています。プログラムの不具合でチャンネル数が8になると、この不具合が発生します。こ

れは単純なミスで修正しておきました。bwv572を3つの部分に分けて変換したのですが、3部が正しく変換できず、タイミングのズレが発生しています。次回、再度

確認します。

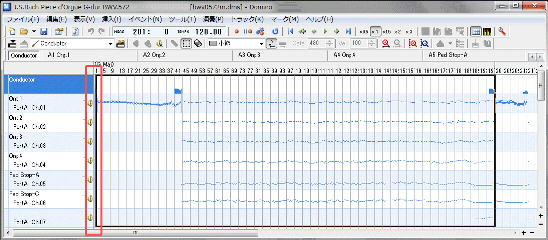

HLSのDMAの続きです。アパートと同様にC/RTL

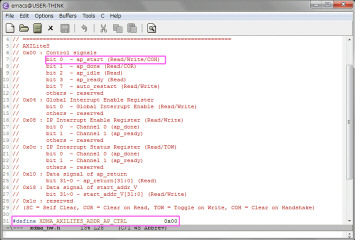

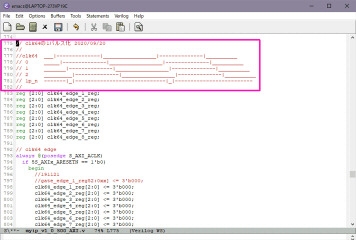

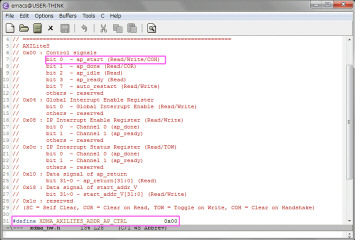

コシミュレーションで波形を出して確認します。PIPELINEを有効にしてTVALID信号を連続出力して、幅を長くします。50〜100MHzでTVALIDが出力すると、アナログディスカバリでは正しく取り込めないからです。左下のAIX−Liteのレジスタアクセスを確認しておきます。

拡大して確認します。18番地に0を書いています。

続いて、0番地に1を書いています。

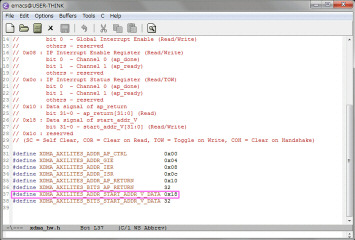

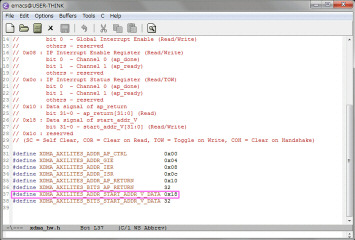

APIのヘッダファイルで確認します。0番地はコントロールレジスタです。0ビット目はap_startビットです。

18番地は引数のスタートアドレスのポインタです。

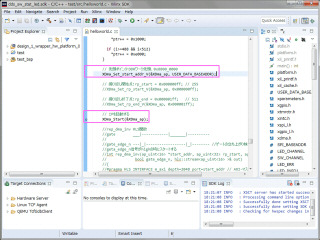

下はSDKのDMAの初期化の部分です。XDma_Set_start_addr_V()関数でスタート番地(DDRの0x88000000)を設定しています。これが18番地

に0を書いているのに対応しています。続いて、XDma_Start()関数でIPをスタートさせています。こちらは0番地に1を書いているのに対応して

います。

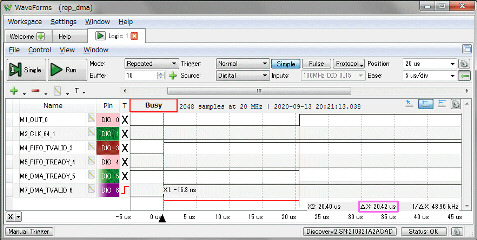

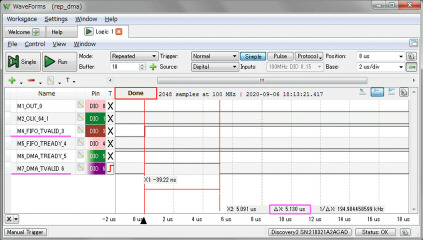

アナログディスカバリのロジアナをFPGAボードのテストポイントに接続して確認します。XDma_Start()関数でブレイクし、アナログディスカバリをシングル動作させます。XDma_Start

()関数を実行すると、TVALID信号が出力しました。長さは約5uSecです。シミュレーションの値に近いです。これは1回のみ出力されることを確認

しました。この単純DMAでは512ワード転送しているようなので、次段のFIFOのリード側からデータを取り出してみたいと思

います。

9月12日

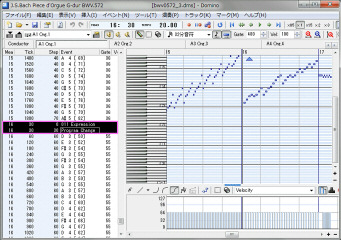

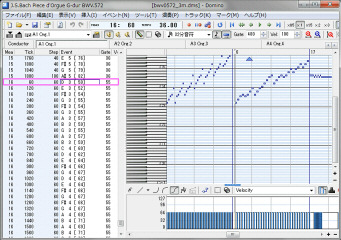

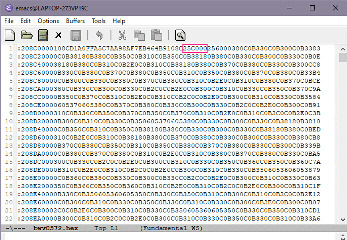

midiconvプログラムの不具合の続きです。先週からのBWV572の第3部の変換結果のタイミングがおかしいので、バイナリダンプしてみます。青色内のステップ数が06、06となって、休符があるばずですが、ありません。

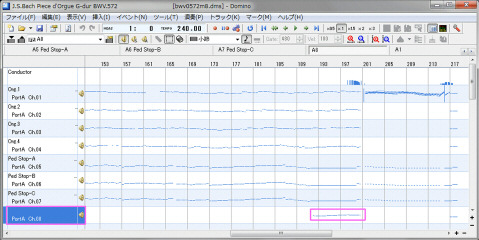

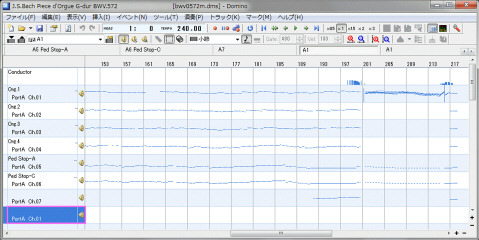

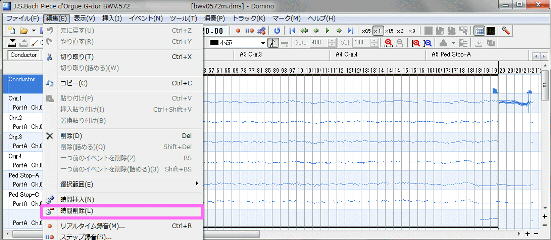

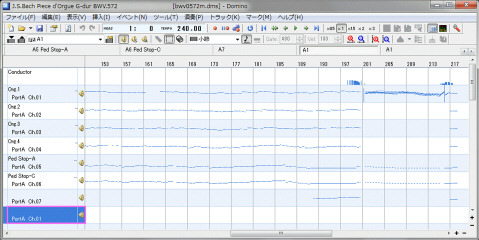

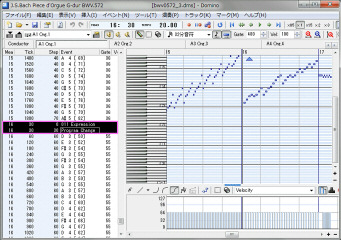

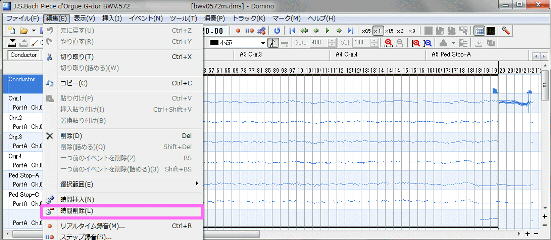

ドミノで確認すると、エクスプレションとプログラムチェンジのイベントが入っていました。

midiconvプログラムはノート以外のデータは変換前に消しておく必要がありました。上記のイベントを削除します。

削除後の変換データです。ステップ数が0A、06となって休符が出現しました。

もう一つ正しく変換するたの条件があり、チャンネルの先頭に空き小節が1つ必要でした。やり方は以下のようにします。今回は下のような3部構成です。

3部のみにするには、下のように先頭の赤枠の1小節を残して、中間部を選択します。

その後、時間削除で削除します。直ぐに忘れてしまうので備忘録のために残しておきます。

プログラムを追加して、データの途中にノート以外のイベントがる場合には重複ファイルに警告を出すようにしました。

早速、3曲録音しました。無事変換できて良かったです。

9月13日

HLSのDMAの続きです。データ転送数を512ワードから4096ワードに変えてみます。FIFOの倍の長さです。

ロジックをFPGAボードにダウンロードして、SDKでDMAをスタートさせテストポイントの波形を確認します。FIFOからのTREADYが40uSec後に下がっています。データがフルになったことが分かります。512ワードで5uSecだったので、4倍の40uSecで正しく動作しているようです。

9月20日

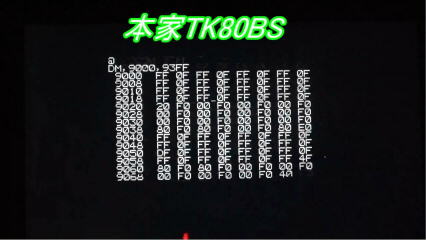

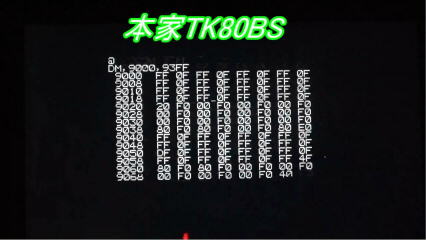

この4連休は後半の3日のみガレージ作業を行いました。TK80BS互換機と本家のモニタ出力のノイズを比べる動画を撮ってみました。初めに本家ですが、かなりノイズが出ます。クリックすると約4MバイトのMP4をダウンロードします。

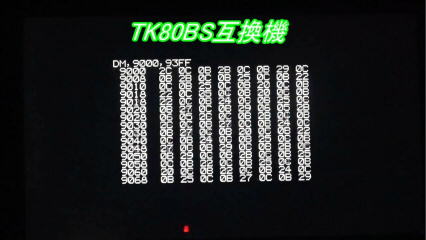

続いて互換機です。ノイズはほどんど出ません。クリックすると約4MバイトのMP4をダウンロードします。

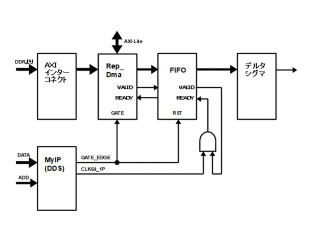

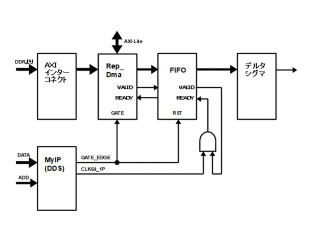

HLSのDMA部のブロック図を書きました。FIFOの読み出しクロックを1パルス化する必要があります。また、ゲートの立ち上がりエッジ信号をDMAとFIFOに接続する必要があります。

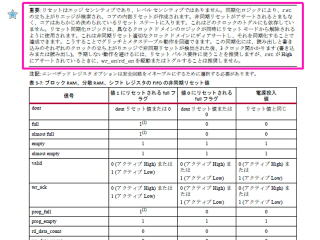

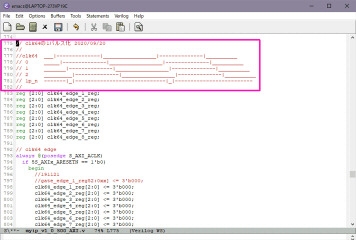

FIFOはシステムクロックに対してTREADY信号1回で1ワード読み出されます。64倍の音程クロックを1パルス化します。

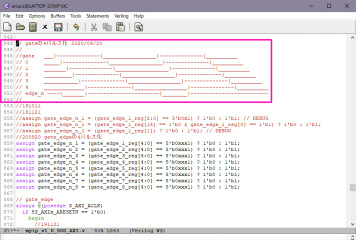

GATEは立ち上がりエッジを検出して、DMAとFIFOに接続する必要します。FIFOの非同期リセットの要件で3クロック以上必要との記述があるので、4パルス化します。

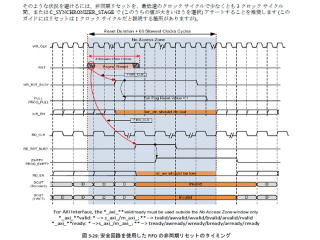

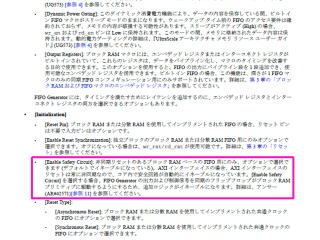

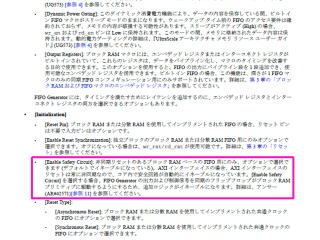

FIFOジェネレータの仕様書を再確認しておきます。非同期リセットは他のクロックとは関係なく、立下りエッジで検出されること。

FIFOにブロックRAMを使うと自動的に安全回路が入ること。

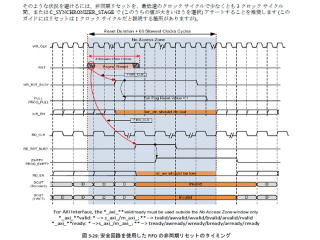

安全回路がある時のタイミングです。リセットが8クロックと書いてありますが?です。3クロックじゃなくて、8クロック必要ということでしょうか?また、リセット後に内部で動作が再開されるのに60クロックかかるということのようです。