TK80/BSの

シンセシステムを復活/拡張したい〜

その59

Rep_Dmaの動作確認

多チャンネル化

2020年

2020年

11月21日

20日は休みで、午後からガレージに来ました。HLSのRep_Dmaの続きです。簡単に2chで動作すると思ったのですが、そんなに簡単ではなかったです。SDKでデバッグすると、マイクロブレーズが走ったままとなり制御できません。

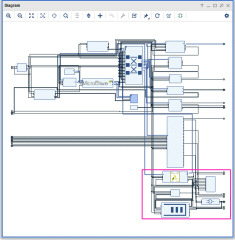

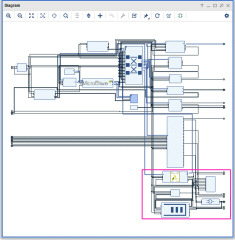

1チャンネルで動作している状態から少しづつ変更し、どこが悪いのか確認します。1チャンネル分だけ臨時で入れていたFIFOのクリアを8チャンネルにしたmyipを組み込んで動作確認を行います。

FIFOがクリアされ、正しく動作しています。

ブロックデザイン上で2チャンネルのDMAとFIFO、デルタシグマDACを追加し、合成/インプリします。

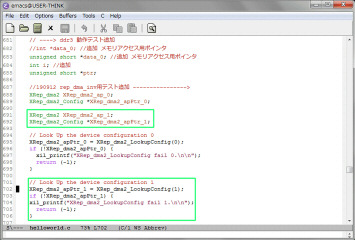

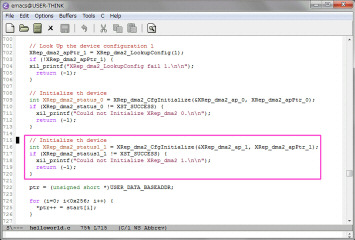

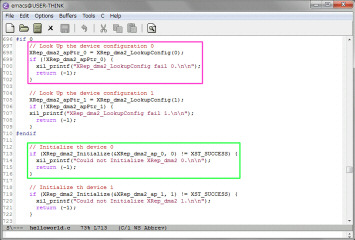

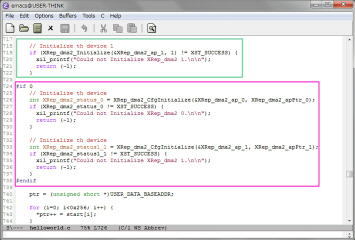

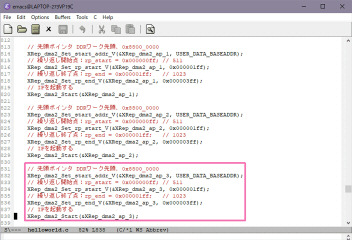

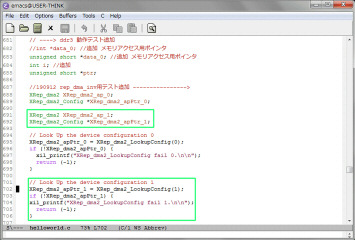

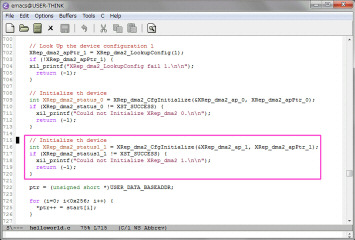

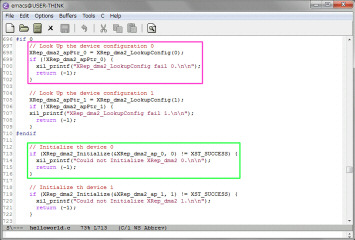

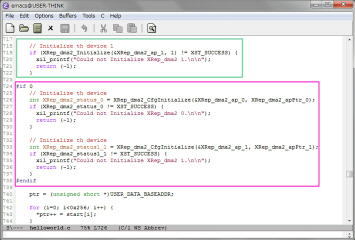

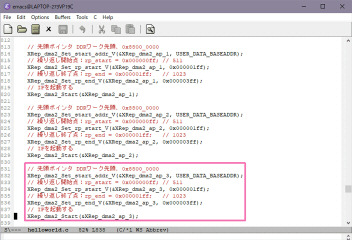

2チャンネルの初期化を追加します。1チャンネルと同様に、変数を用意してLoockupConfig関数を使って情報を取得し、CfgIntialize関数で初期化します。

SDK

内でFPGAにロジックをダウンロードし、プログラムのデバッグをすると、CPUが停止せず、実行状態のままになります。停止ボタンで停止させると、ア

センブラのコードで停止し、この後の再実行はできませんでした。1チャンネルと同じAPIで2チャンネルも初期化しているのが不具合の原因のようで

す。

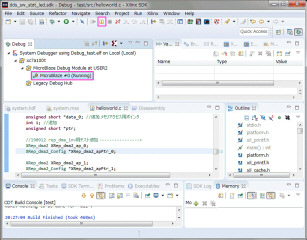

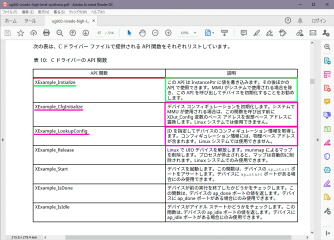

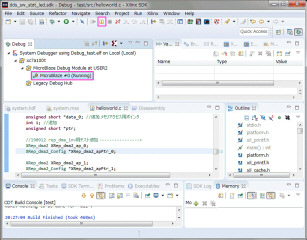

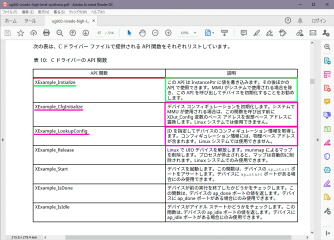

高位合成のユーザマニュアルで初期化関数を確認すると、MMUの有無で使用する関数が決められているようです。今回MMUは未使用です。FPGA大全でもInitialize関数が使われています。

早速、Initialize関数で初期化するように変更し、SDKでプログラムのデバッグをすると、正常に停止して開始されるようになりました。

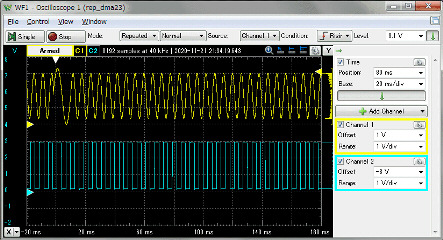

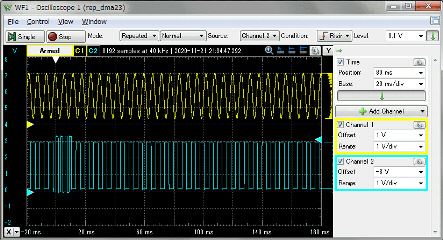

実行後、ボード上のスイッチでチャンネル1と2のDMAが開始できるようになりました。左が正弦波の1チャンネル、左が方形波の2チャンネルで個別に制御できることを確認しました。

11月22日

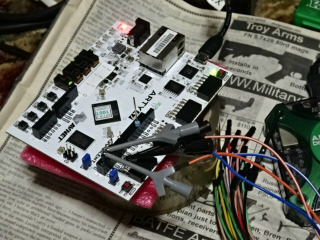

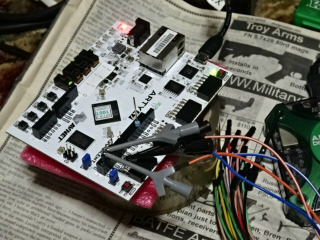

ボード上のスイッチで2チャンネルの出力できるようになったので、MC80バスから出力してみます。以前に作製しておいたレベル変換基板を介して、USBパラレル変換器の出力を接続します。

MC80バスで、2チャンネルのRep_dmaが動作することを確認しました。

11月23日

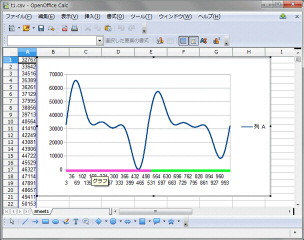

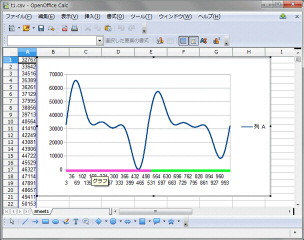

暫定の正弦波と方形波の出力データを16ビットのトーンホィールジェネレータの波形に変更します。16’、5−

1/3’、8’の合成です。赤のラインがスタート部で振幅が16ビットフルにして、緑のラインがリピート部で振幅を80%にしました。1チャンネルと2

チャンネルを別のデータにしようと思ったのですが、マイクロブレーズのRAMが32Kの設定になっていて、RAMが足らなくなったので、とりあえず、同じ

データです。オープンオフィスのCALCで波形を確認します。

上記のデータを配列に入れDDRに転送して出力テストを行いました。先頭の振幅が大きいので、トリガが掛かり先頭を分別できます。動作良好です。

11月25日

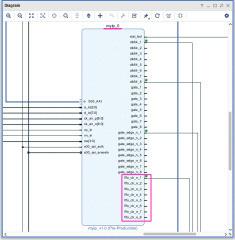

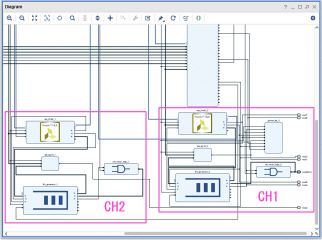

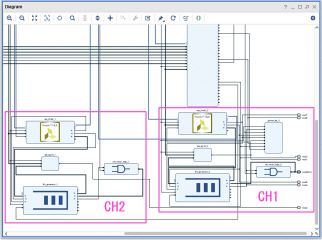

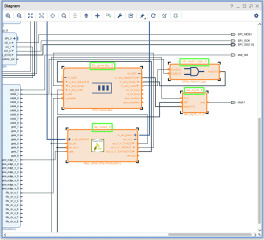

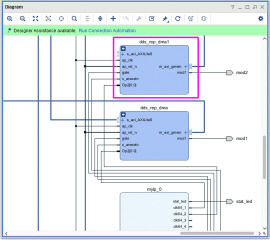

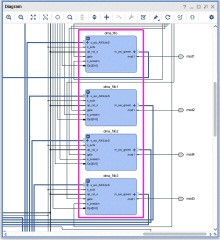

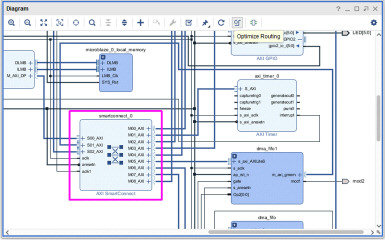

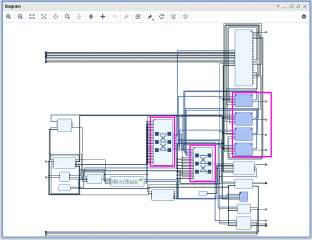

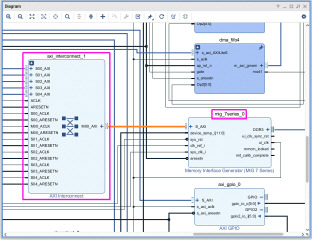

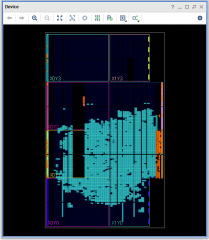

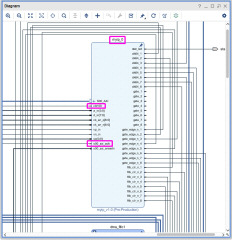

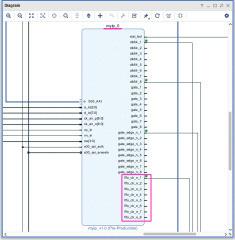

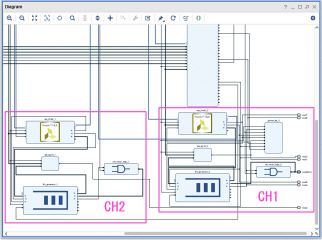

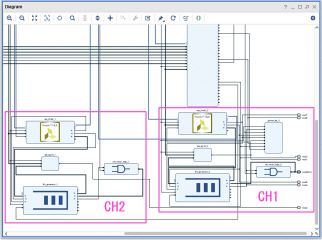

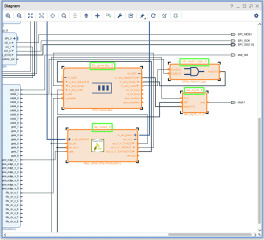

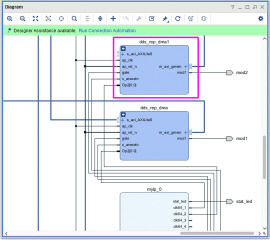

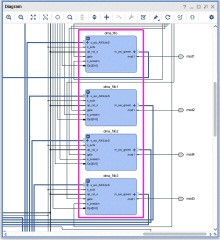

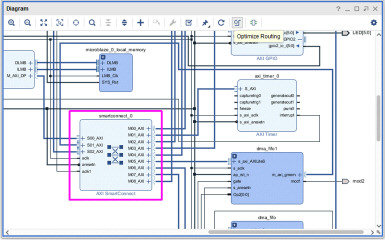

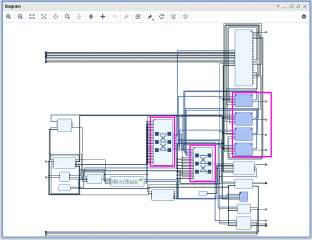

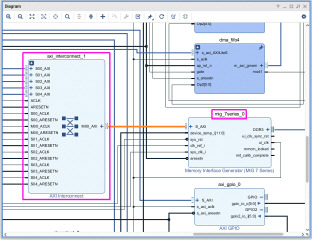

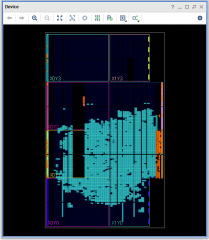

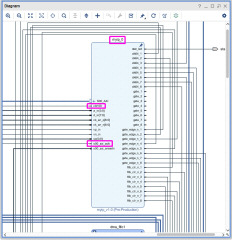

上記のようにDMA部のチャンネルを増やすには必要なモジュールを単純に増やしていえばいいのですが、数が増えると配線が大変で、ブロックもごちゃごちゃしてきます。ブロックデザインでは階層化が可能です。下は上記で書いた単純に各モジュールを追加して2チャンネルにしたブロックです。

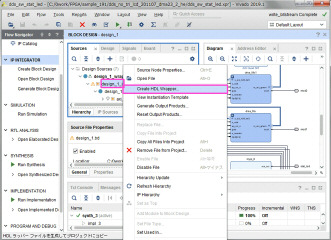

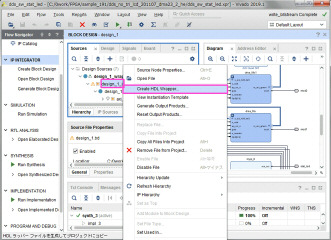

階層化するには階層化したいモジュールをCTRLを押しながら選択していきます。ここではDMA、FIFO、汎用ロジックのANDとデルタシグマDACを選択します。選択されたモジュールはオレンジ色になるので分りやすいです。

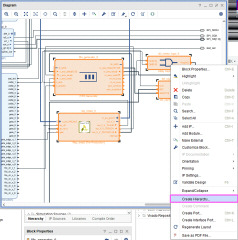

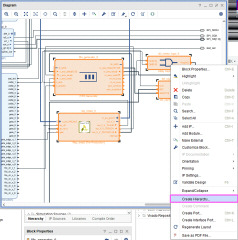

右クリックでメニュー出し”Create Hierarchy”を選びます。

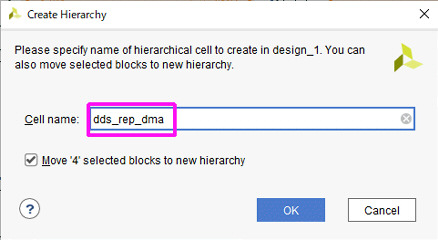

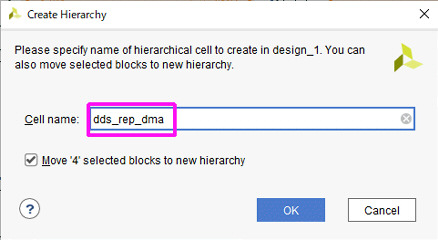

階層化するモジュールに名前を付けて、OKを押します。

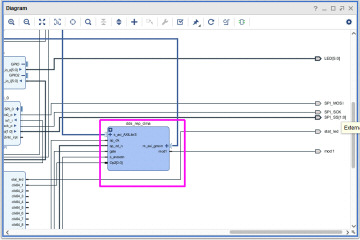

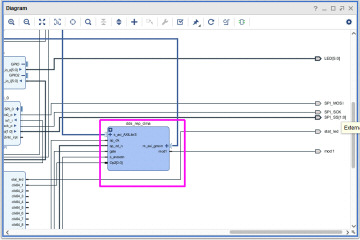

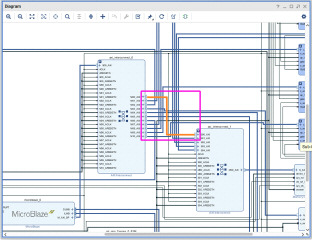

選択した複数モジュールが1つになり、モジュールの外側との配線も維持されます。

モジュールを選択して、コピー&ペーストして、外部との配線を追加すれば、簡単に2チャンネルになります。

階層化されたモジュールは”+”マークをクリックすると内部が展開されます。この方法ではれば8チャンネルにするのは簡単にできそうです。

11月28日

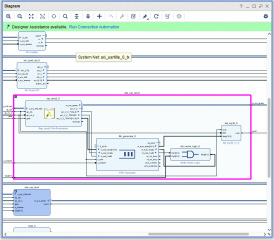

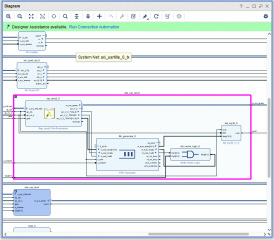

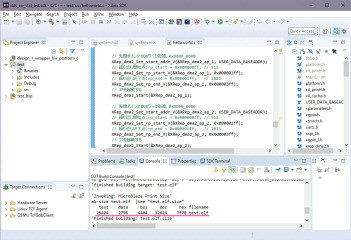

アパートで階層化を行ったDMA部が動作するか実機で確認してみます。DMA、FIFO、汎用ロジックのANDとデルタシグマDACを階層化して、2チャンネルにしてブロックを作成します。

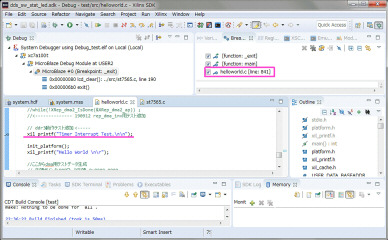

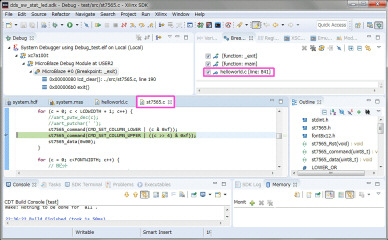

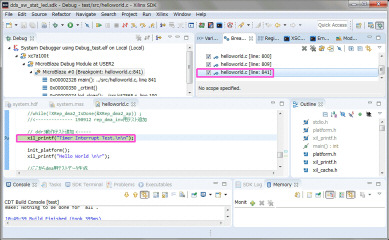

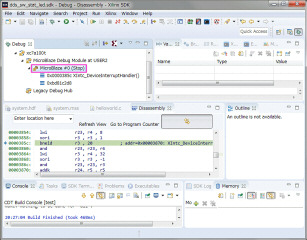

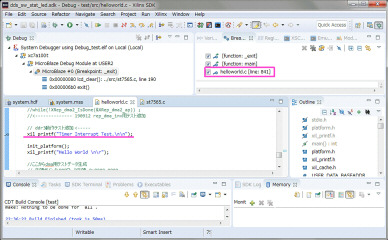

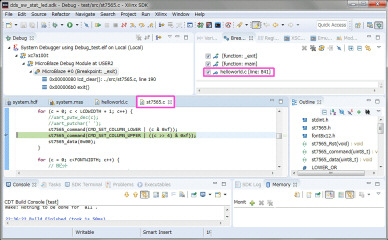

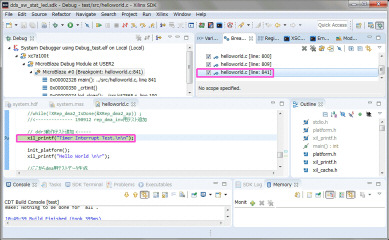

通常通り、FPGAを合成/インプリして、SDKを起動します。helloworld.c内の階層化したモジュールの初期化関数後にブレイクポイントを設定しました。

実行すると、なぜか関係の無いLCDのソースコードst7565.c内で停止します。FPGAとSDKの整合が取れていないようです。

11月29日

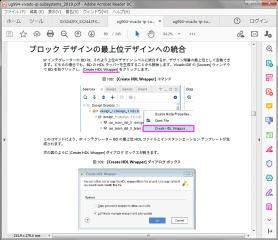

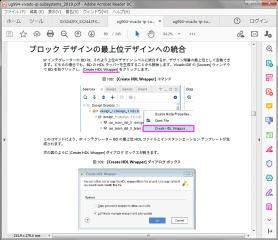

階層化の記述のあるug994の”IPインテグレーターを使用したIPサブシステムの設計”を確認してみます。階層化した後は2つのステップが必要だと書いてありました。初めに”ラッパーの生成”です。

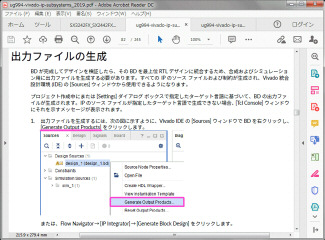

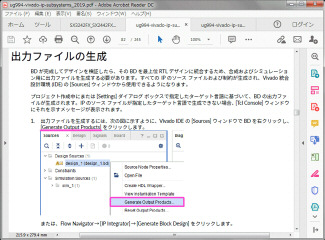

続いて、”出力ファイルの生成”です。

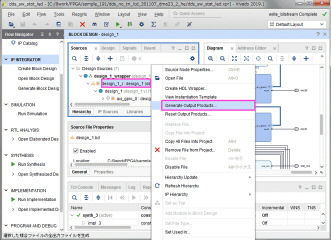

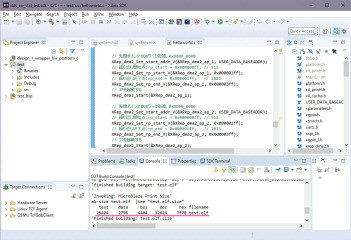

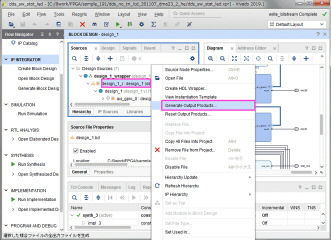

早速、同じようにオペレーションを行います。初めに、design_1.dbを右クリックして”Create HDL Wapper”を選択し、ラッパーの生成を行います。

続いて、同じくdesign_1.dbを右クリックして”Create Output Products”を選択し、出力ファイルの生成を行います。

その後、FPGAを合成/インプリして、SDKを起動します。通常の通り、初期化の後で停止するようになりました。やはり、ちゃんとマニュアルを読まないといけません(笑)。

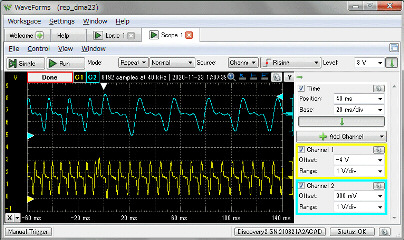

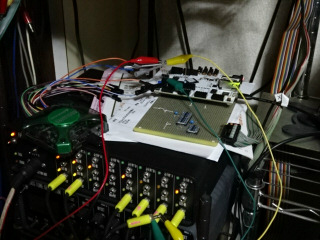

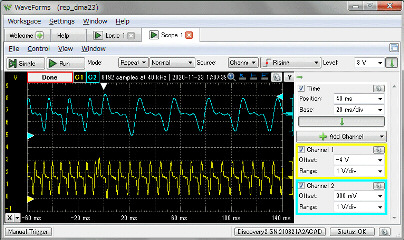

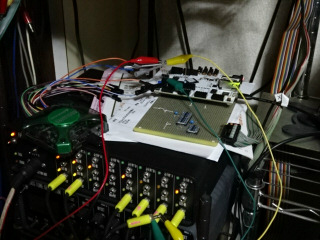

先週と同様にレベル変換基板を介して、MC80バスから出力してみます。

PC−>USB−パラレル変換ー>実験ボードという接続です。

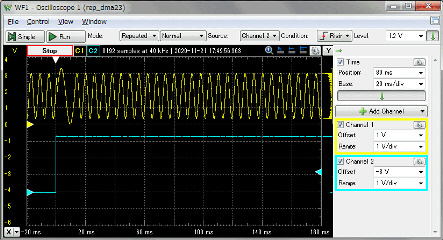

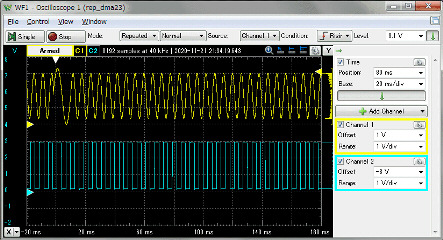

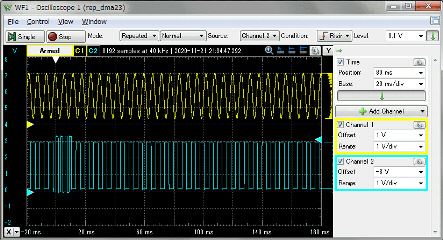

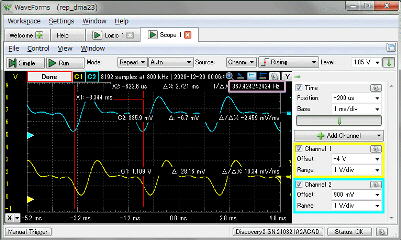

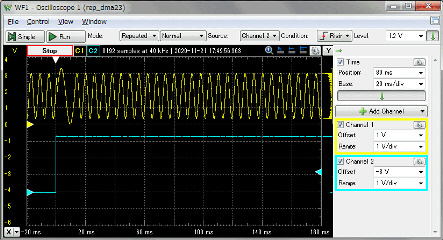

2チャンネルで正常動作しています。波形は先週と同じ16’、5−

1/3’、8’の合成です。FIFOのクリアのテストで先頭1回(下線部)出力ありの設定です。ここで波形を拡大します。DDSの周波数を512倍にして、波形テーブル長を512ワードに変更したので、周波数も正しく出ています。デルタシグマ出力を旧アナログシンセのVCFに入力して、MP3を録音しました。画像をクリックすると約1.3MバイトのMP3をダウンロードします。

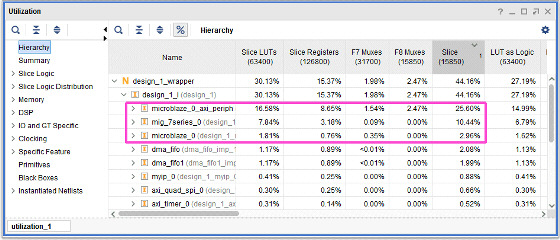

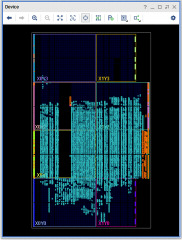

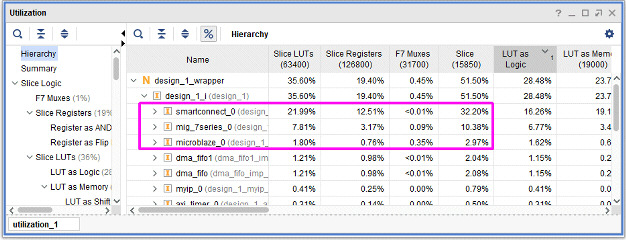

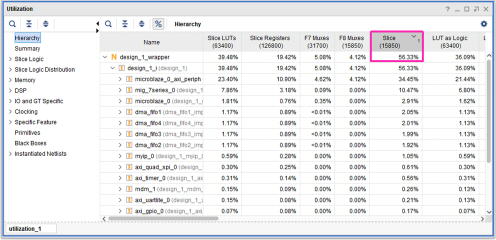

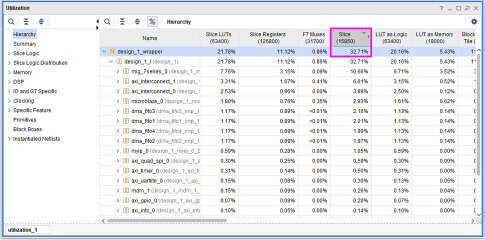

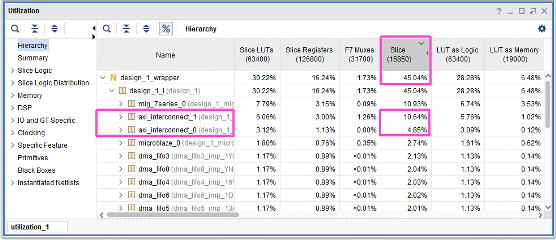

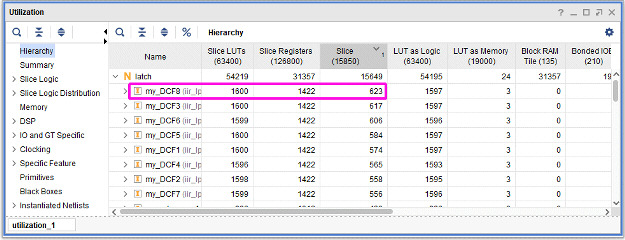

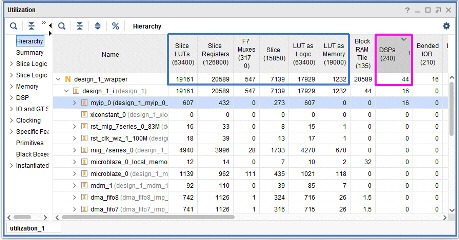

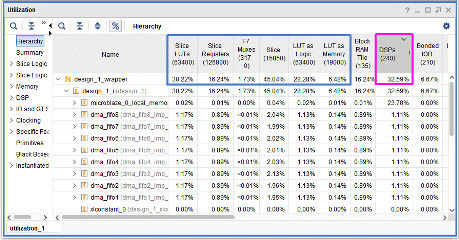

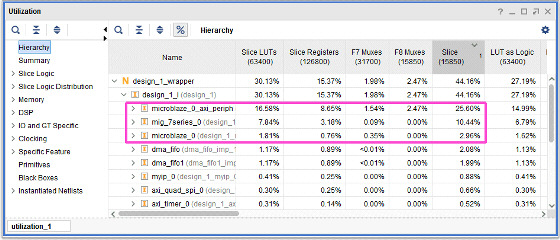

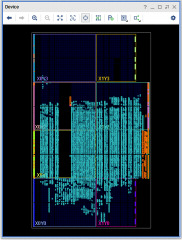

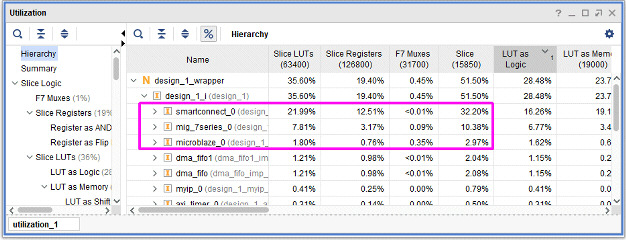

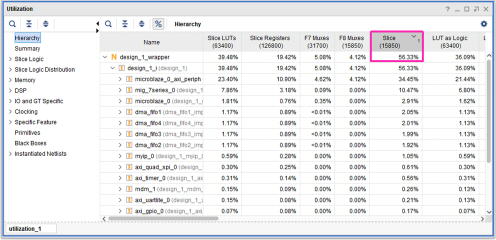

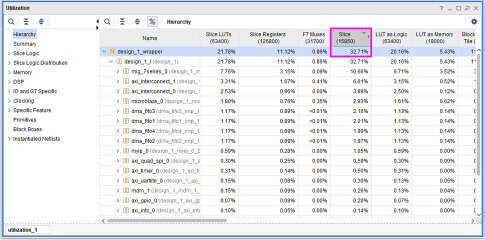

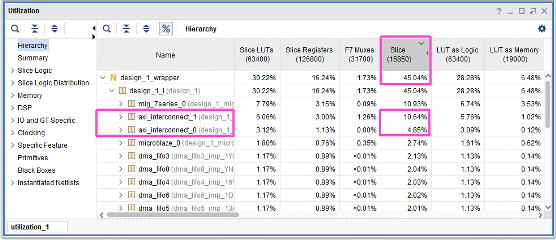

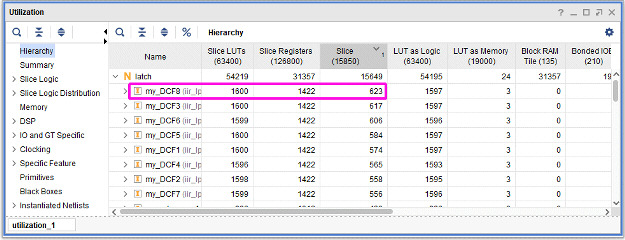

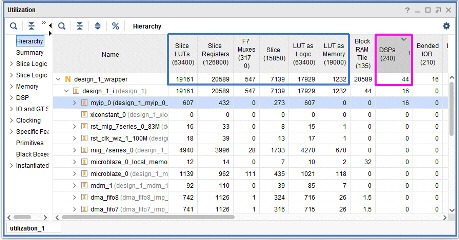

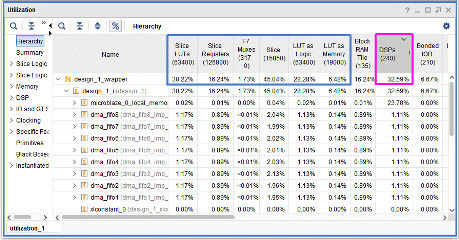

気になる、ロジック使用量を確認しておきます。デバイスは100Tです。FPGA内のデバッグ用ILA(ロジアナ)を削除して、2チャンネルのDMAの音源(デルタシグマDAC出力)のみでスライスが約44%です。AXIインターコネクトが25%、DDRコントローラが10%使われています。予想より多いです。

少し気が早いですが、24チャンネルのアナログミキサーを注文しました。旧シンセ、FPGAシンセ、今回作成してDMAテーブルシンセ用で合計24チャンネルです(笑)。今回の24チャンネルにはUSBオーディオが無いので、今使用してる12チャンネルと併用します。12チャンネの上に設置する予定です。余っていたワイヤラックの足の長さを揃えて組み立てました。野外に保管してあったので、少し錆びています。

11月30日

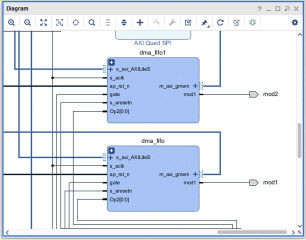

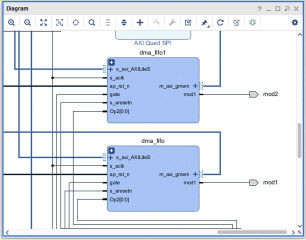

アパートのPCでAXIインターコネクトを2チャンネル分増設し、DMA部を4チャンネルにして、ロジックの使用量がどのくらい増えるか確認してみます。

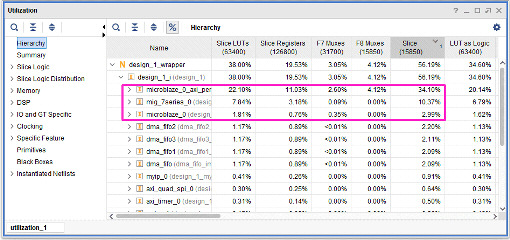

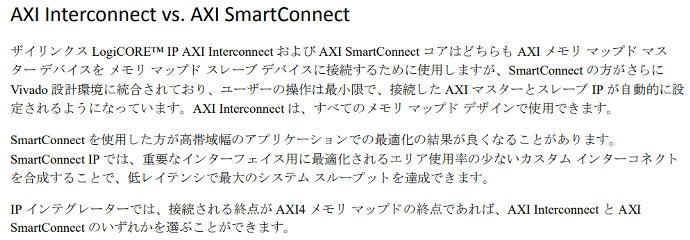

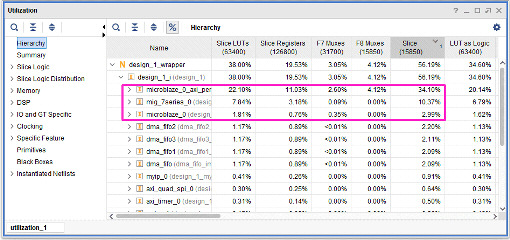

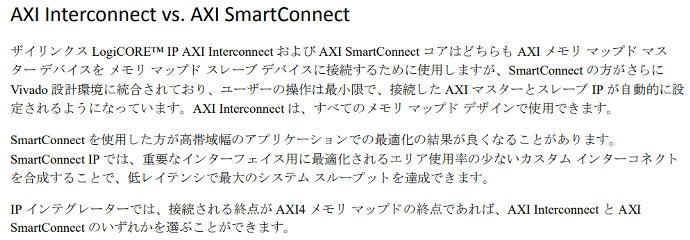

4チャンネルでは全体でスライスが約56%になり、AXIインターコネクトが25%から34%に増えました。AXIスマートコネクトというIPもあるので、使用量を確認した方がいいです。

ユーザガイドのug994にインターコネクトとスマートコネクトの違いが出ていました。エリアが少なくなるようです。

12月2日

アパートでAXIインターコネクトからAXIスマートコネクトに変更してロジック使用量を確認します。DMAは2チャンネルです。

残念ながら、使用量は増えました。全体で約51%に増加しています。スマートコネクトが32%です。AXIインターコネクトの時は全体が約44%、インターコネクトが25%でした。ということで、インターコネクトを使った方が良さそうです。

12月5日

新ミキサのために少し配置を変えます。現行の12チャンネルミキサを手前に移動し、ワイヤラックを設置しました。

午後になって、24チャンネルミキサが到着しました。早速、ラックの上に乗せて、各チャンネルの動作を確認しました。

ミキサと一緒に購入した、ケーブルとL字フォーンプラグです。

3.5mmのプラグはヤフオクで購入済みです。先端にプラグを半田付けして、8チャンネル分のケーブルを作製しました。

12月6日

ラックは高めに作ってあったので、ポールを短くして、旧DCOが隠れる高さに調整しました。

こちらはアマゾンで購入のMC80バス用の26ピンのフラットケーブル圧接コネクタです。15個で500円くらいで、すごく安いです。

旧シンセとFPGAシンセを接続して動作確認しました。エフェクタが2系統あり、良さそうです。新しいミキサにはUSBインタフェースが無いので、12チャンネルを経由してPCに接続します。

12月13日

MC80バスのケーブルを延長します。フラットケーブルをピンヘッダを使って対向させて延長すると、1ピンと2ピンが入違ってしまうので、一度、基板を介して延長します。先週購入した26ピンの圧接コネクタを3個使ってケーブルを作製しました。

早速、延長ケーブルの動作確認を行います。動作良好です。

12月15日

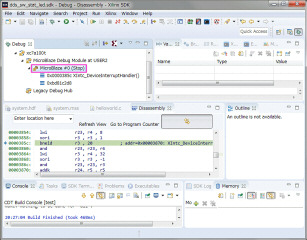

アパート作業です。先々週、DMA部を4チャンネルにしてロジック使用量を確認しました。実際に4チャンネルで動作確認を行うと、なぜか3チャンネルまでは正常に動作しますが、4チャンネル目の初期化プログラムを追加すると、デバッグ開始時にMicroBlazeがmain関数の先頭で停止しない不具合が発生しました。

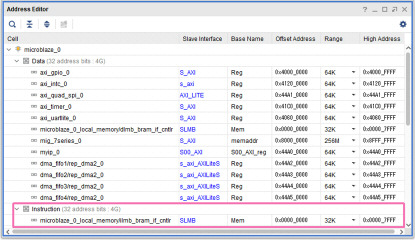

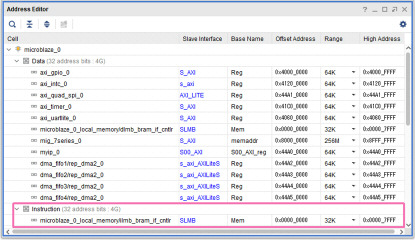

SDKのビルド時のelfのサイズを見ると7f70まで達していて、ローカルメモリが足りていないのではと思われます。現状のMicroBlazeのローカルメモリは32KBに設定しています。

詳しいメモリの使用状況はメモリマップを確認するのが一番ですが、デフォルトでマップファイルを出力しない設定になっているようで、以下のWEBページで出力する方法が紹介されていました。

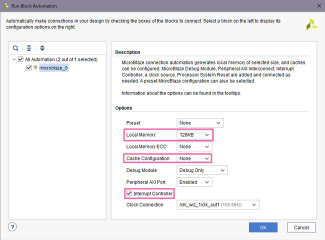

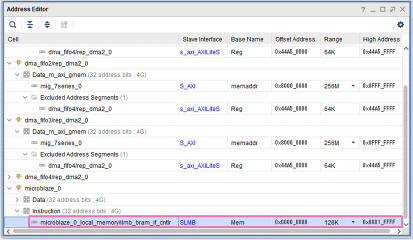

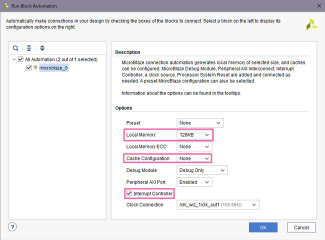

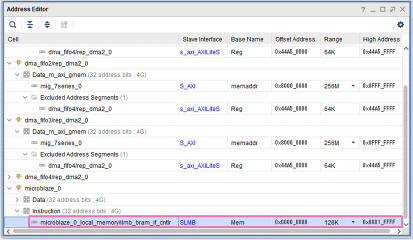

MicroBlazeのローカルメモリを増やすにはブロックデザイン上で一度、MicroBlazeを削除してから、再度IPで追加する必要があるようです。(ブロックオートメーションの実行でローカルメモリの設定か可能です)ローカルメモリを最大の128KBに設定して、キャッシュ無し、割り込み有りに設定しました。一度、削除すると外れてしまう結線もあるので、再度接続してブロックデザインを完成させます。その後、アドレスエディタでローカルメモリが128KBになっていることを確認します。

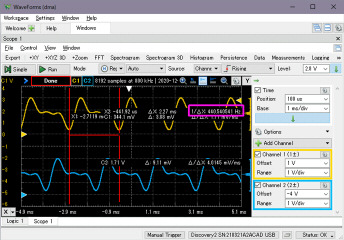

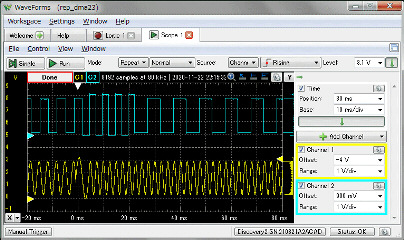

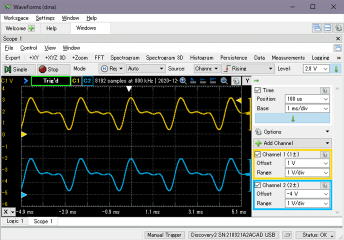

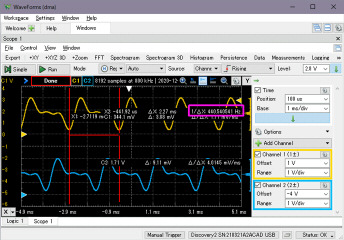

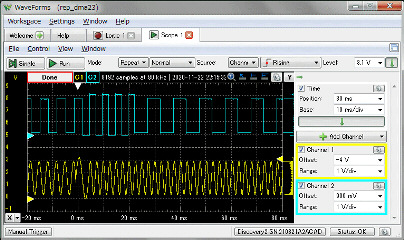

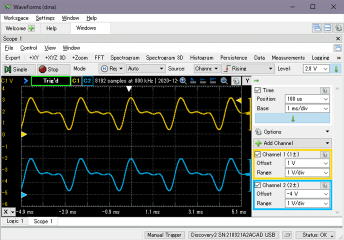

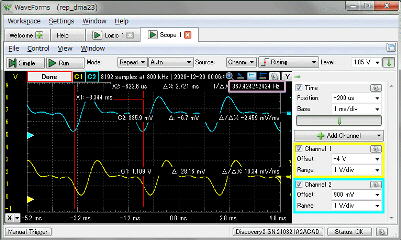

FPGAを合成/インプリしてロジックをダウンロードし、SDKでデバッグします。正しくmain関数の先頭で停止するようになりました。4チャンネル分の初期化を行い、デルタシグマDACの出力をアナログディスカバリのオシロで確認します。

アナログディスカバリが2チャンネルで、出力の4チャンネルが同じ波形なので、いまいちですが、1〜4チャンネルに正しくDDRの波形データが出力されていることを確認しました。今後の確認事項として8チャンネルに増設し、DDR3−>インターコネクト−>DMA間の転送が間に合っているか確認が必要です。現在のテーブル長は512ですが、256に短くするなど調整が必要かもしれません。

ローカルメモリを増やしたので、ロジック容量を確認しておきます。スライスが54.33%です。メモリを増やす前が54.19%だったので、ほとんど増えていません。

12月17日

またまた、

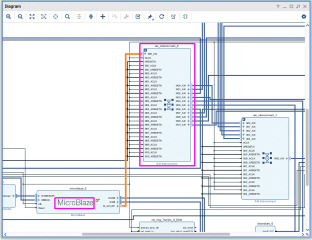

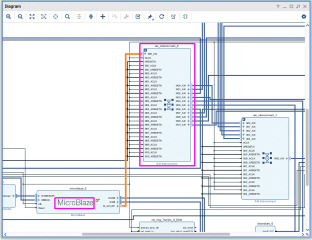

アパート作業です。一昨日、Microblazeのメモリを128KBにしたところでロジックの使用量の一番多いスライスが54%を少し超えていました。一番ロジックを使っているのはAXIインターコネクトです。現状でスレーブ5ポート、マスタ12ポートを使っています。今後、DMA部を4チャンネルから8チャンネルに増設すると、さらにAXIインターコネクトのロジック使用量が増えると思われます。1つのインターコネクトに多数のスレーブとマスタが付いていると、多数の組み合わせでアービトレーションする必要があり、多量のロジックを使うと予想されます。そこで、MicroBlazeの繋がるスレーブが1ポートのインターコネクトと、DDR用のMIGが繋がるマスターが1ポートのインターコネクトの2つに分けてみました。DMAは以前と同じ4チャンネルです。

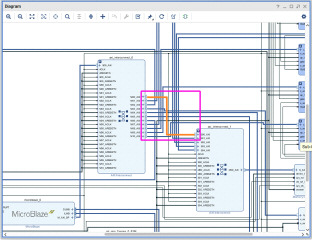

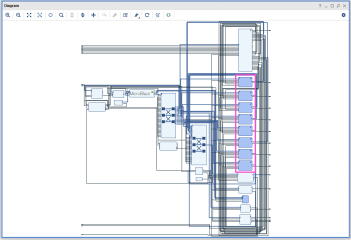

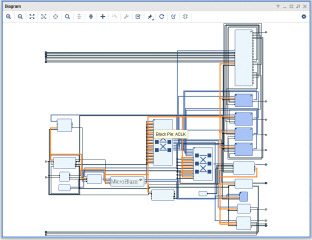

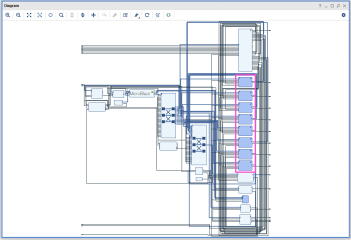

左がMicroBlozeの繋がるスレーブが1ポートのAXIインターコネクトです。右がMIGの繋がるマスタが1ポートのインターコネクトです。

2つのインターコネクト間はカスケードで接続します。

簡易的なロジック使用量のテストなので、簡単のため基本クロックをDDRの166MHzの半分の83MHzにしました。オレンジのラインが基本クロックです。

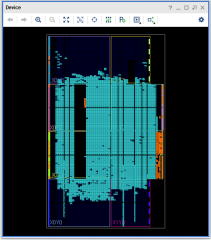

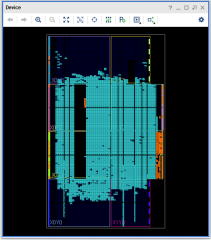

合成/インプリ後、ロジック使用量を確認します。スライスを54%から33%に減らすことができました。音程を作るDDSのクロックも100MHzから83MHzに下がったため音程はその分、低くなりますが、4チャンネルでDMAの動作良好です。

12月19日

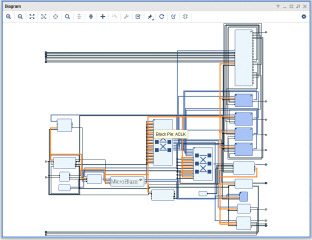

ガレージでの作業です。基本クロックはアパートの作業と同じ83MHzで、8チャンネル化してみます。

合成/インプリ後、ロジック使用量を確認します。スライスは4チャンネルで33%でしたが、8チャンネルでは約45%になりました。2つのAXIインターコネクトは合計で15.5%です。

12月20日

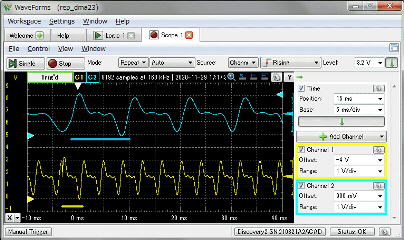

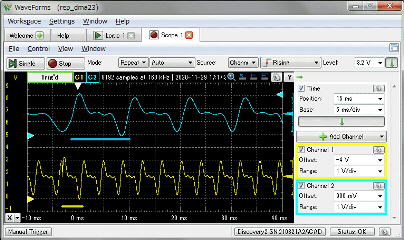

8チャンネルの動作確認を行います。アナログディスカバリでデルタシグマDACの各出力を確認します。

8チャンネルで動作良好です。DDSのクロックが100MHzから、166.667MHzの半分の83.3335MHzになったので、DDSの出力はその割合で低くなります。初期値は440Hzに設定していますが、約367Hzになっているので合っています。基本クロックを83MHzのこのまま、正しく440HzにするにはDDSの分周設定を83MHz用に修正する、またはDDSの動作クロックのみ100MHzに戻する必要があります。

以前にHLSで作成したFPGAシンセの各モジュールのスライス使用量を調べます。初めはDCFです。使用量は約623です。

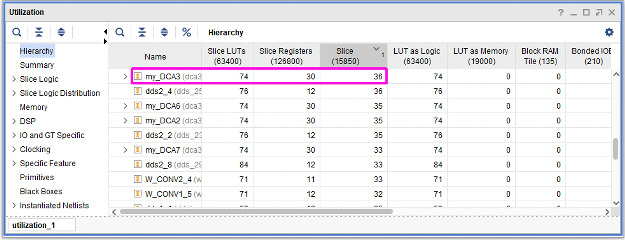

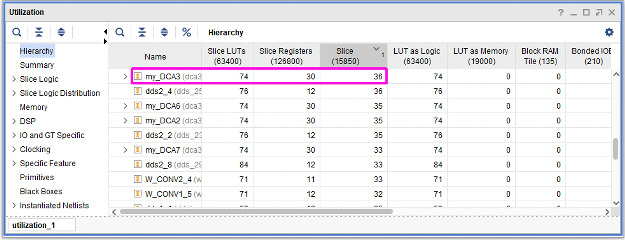

続いて、DCAです。使用量は約36です。

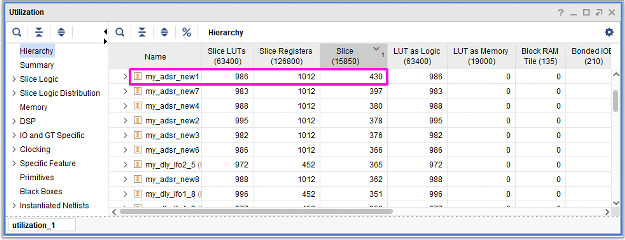

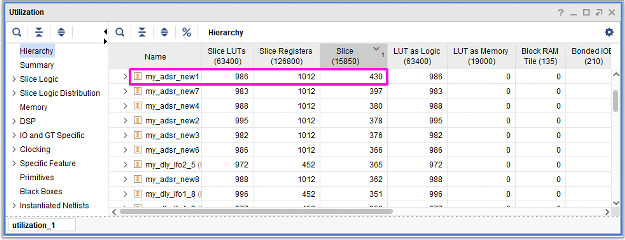

続いて、EGのスライスの使用量は約430です。

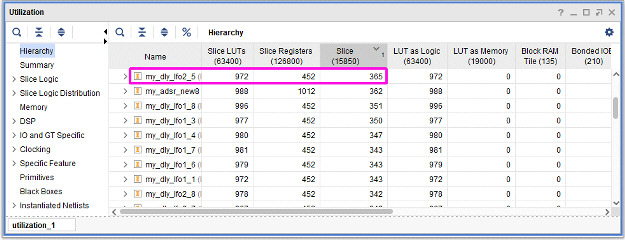

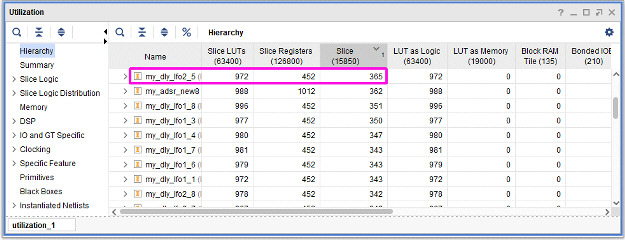

最後はLFOです。スライスの使用量は約365です。各モジュールを1つづつ使った場合を合計すると、8チャンネルで11632です。現在の残り容量は約8700なので全然足りません。サンプリング、トーンホイール音源に限定し、DCFを省くと、8チャンネルで6648です。これでも、グルーロジックもあるので、なかなか厳しいと思われます。解決策としては100Tの載ったARTYボードを2枚使う、または200Tの載ったNexysVideoボードを使うということもできます。

12月22日

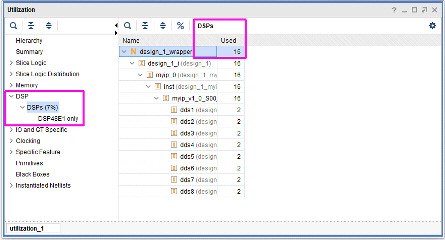

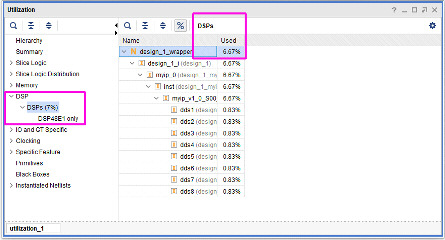

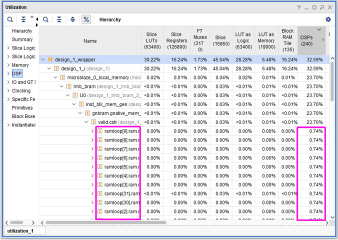

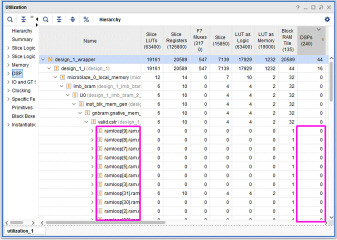

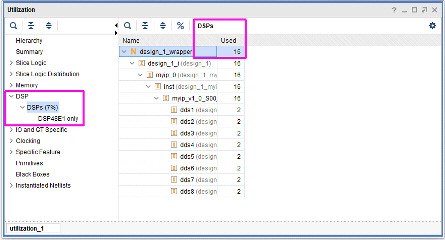

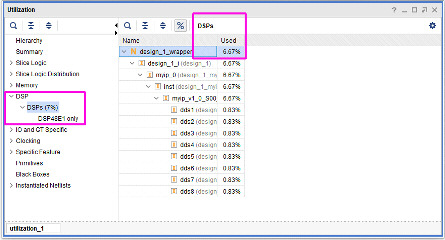

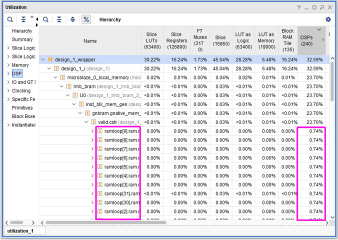

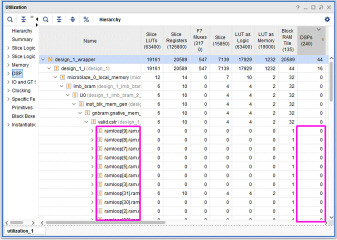

Vivadoのロジック使用量のレポートが少しおかしいです。下はHLSのFPGAシンセでも気にしていたDSP使用量の個数の昇順表示です。Vivadoのバージョンは2019.1です。

下はパーセントの表示です。青枠は上の個数をパーセント表示にした値と合っています。DSPの表示は変で、DDSの入っているmyipはDSPを使っていますが、なぜかmicroblazeのローカルメモリがDSPを23.7%も使っています。しかも、上の個数表示では昇順にしているにも関わらず、出てきません。

左サイドの階層表示でDSPを表示すると、正しいと思われる値が出てきます。DSPは合計で16個で、全体が240個なので、約7%です。

左サイドの階層表示でパーセントの表示にすると6.67%と表示され、多分これが正解です。

microblazeのローカルメモリの階層を展開していくと、不具合の原因らしきとことが分かりました。左がパーセント表示、右は個数表示です。パーセント表示でローカルメモリの最小値が0.74%で、32個の合計で23.7%になっています。個数表示にすると、0.74%は0個になり、合計で0個です。

12月23日

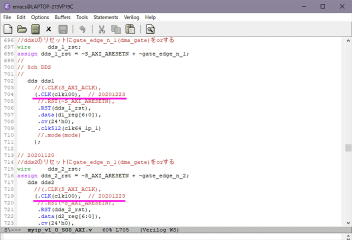

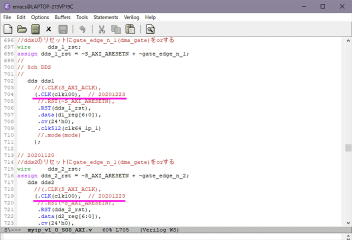

DDSのクロックを元々の100MHzにするために、myipにclk100の端子を追加しました。s00_axi_aclkは元の83MHzのシステム基本クロック入力です。

myip内のDDSインスタンスのクロックを83MHzから100MHzのclk100に変更します。

合成/インプリ後、FPGAにロジックを書き込み、デルタシグマDAC出力が440Hzになっていることを確認します。8チャンネルとも動作良好です。