TK80/BSの

シンセシステムを復活/拡張したい〜

その60

Rep_DmaとHLSシンセのマージ

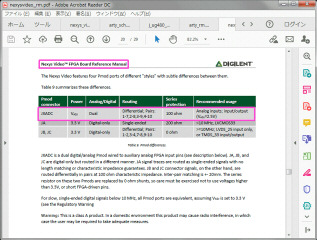

Nexys Videoボード

2020年

2020年

12月26日

お正月休みに入りました。8ch化したリピートDMAをMC80バスに接続し、DDR3−>インターコネクト−>DMAの転送速度が間に合っているか確認します。

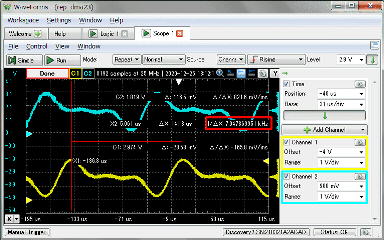

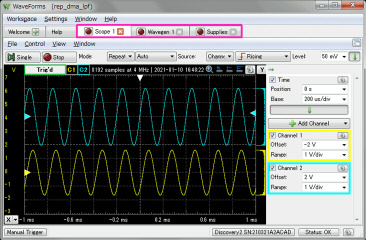

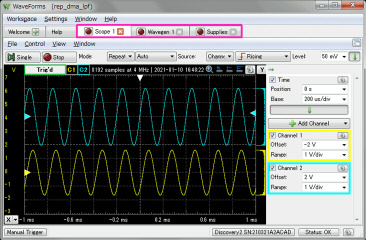

8チャンネル全てA音で一番上の7.04KHzに設定し、デルタシグマDACの出力を確認しました。転送速度は7040(周波数)x512(テーブル長)x8(チャンネル)x2(16ビット)=57.67Mbyte/Secです。AXIインターコネクトとリピートDMAは32ビット接続、MIGは128ビット接続です。直接デルタシグマ出力でフィルタ無しなので、ノイズが多いですが、問題無いようです。

リピートDMAのデルタシグマDACをそのまま、旧アナログシンセのVCFに入力し、音出し確認を行いました。動作良好です。

12月28日

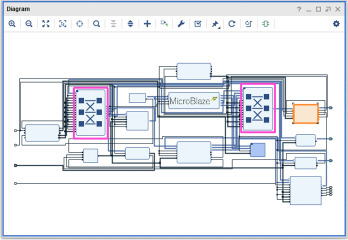

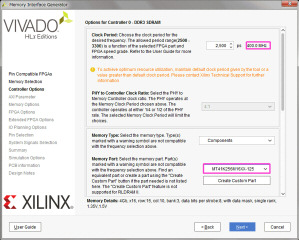

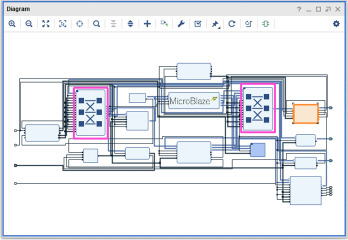

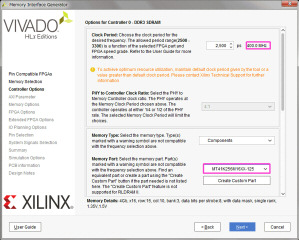

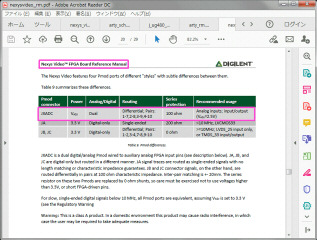

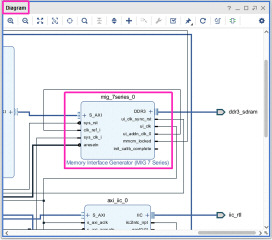

Nexys Videoボードを秋月に発注しました。Artix−7の200Tが載っています。ロジック容量は現在使用しているARTY−7の100Tの2倍です。DigilentのページからDDR3とDMAのIPを使ったデモプロジェクトをダウンロードし、Vivadoに読み込んでみました。インターコネクトが2つ使われています。DDR3のクロックはARTYボードの333MHzから、400MHzに上がっています。DDR3コントローラのMIGはXADCの温度センサを使う仕様なので、定数入力に変更してみます。温度センサをディゼーブルにして、定数入力に変更します。

ブロックデザインでMIGの温度入力に定数を接続します。

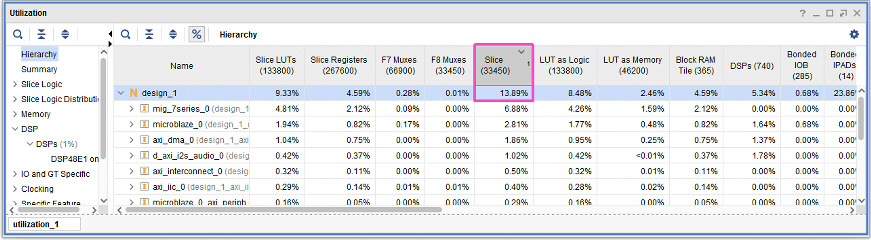

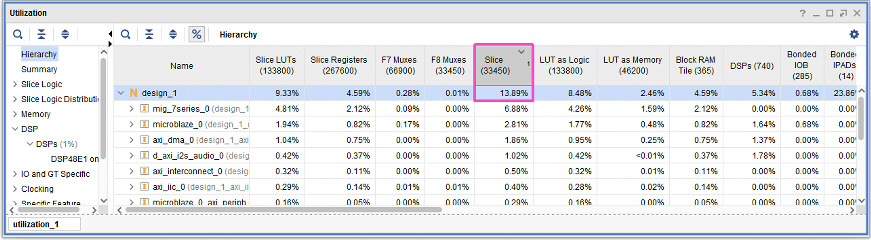

合成/インプリし、ロジック使用量を確認します。スライスの使用量は約14%です。このデザインではMicroBlaze用にキャッシュを実装しています。

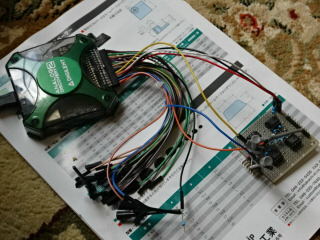

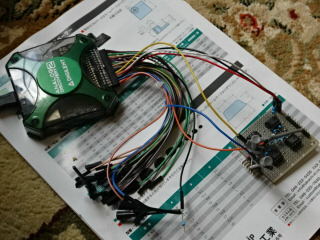

リピートDMAに戻って、4チャンネルでBWV639を録音してみました。接続はPC−>USBパラレル変換ー>リピートDMA−>旧アナログVCF−>旧アナログVCAです。ここをクリックすると、約2MバイトのMP3をダウンロードします。

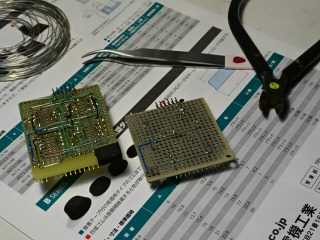

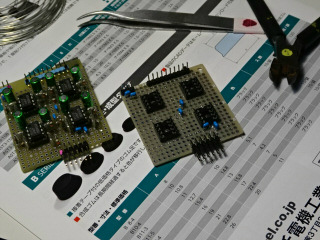

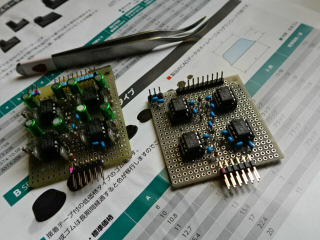

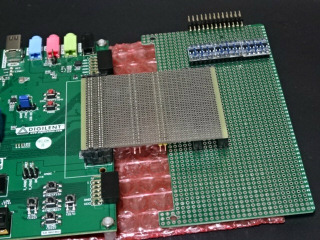

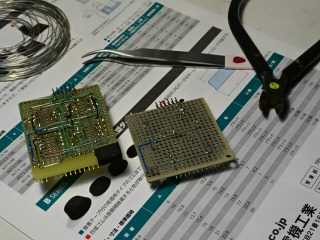

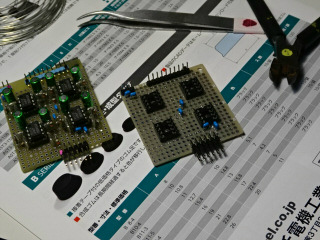

FPGAの信号線をそのまま延ばして実験していると、FPGAが壊れる可能性があるので、PMODコネクタのデルタシグマ用のフィルタボードを作製します。8チャンネルHLSシンセからフィルタボードを抜いて見本にします。Nexys VideoボードにもPMODコネクタが付いているのでそのまま使えるはずです。

12月29日

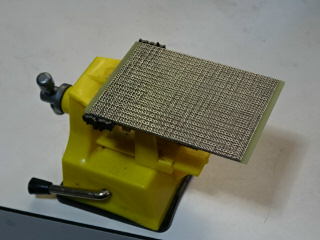

出力用のカップリングコンデンサが無いですが、4チャンネル分が完成しました。足らない部品は秋月に発注済みです。

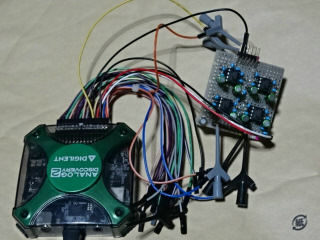

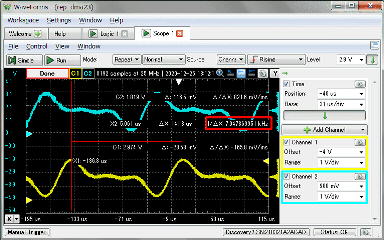

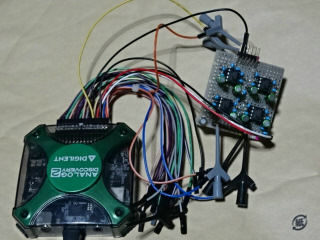

フィルタボードの動作確認をします。アナログディスカバリでプラス/マイナス電源、シグナルジェネレータ、オシロを使います。カットオフは約11kHzに設定しました。ローパスフィルタの動作良好です。

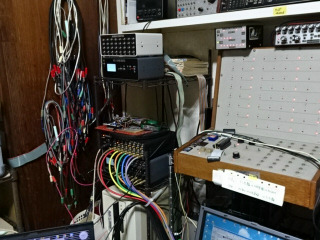

ARTYボードのPMODコネクタにフィルタボードを接続してみます。オペアンプのプラス/マイナス電源用のケーブルも作製しました。

プラス/マイナス電源は実験用に臨時でHLSシンセから取り出します。

12月30日

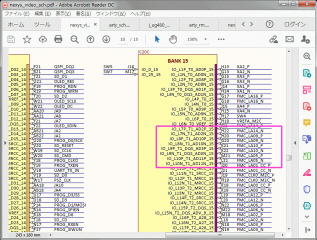

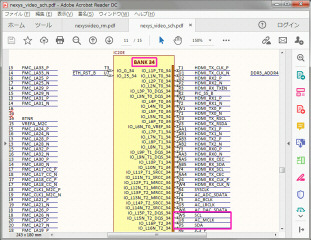

Nexys VideoボードのXADCの回路を確認しておきます。HLSシンセと同様にDCAのベロシティ制御に使用する予定です。4チャンネルはPMODコネクタに接続され、残りの4チャンネルはFMCコネクタに接続されていました。接続は差動入力になっています。マルツ経由のDIGIKEYで勘合するコネクタが購入可能です。発注しておきました。ハーフピッチのユニバーサル基板に実装可能と思われます。

PMODコネクタには8本信号線が繋がりますが、差動なので、4チャンネルになっています。

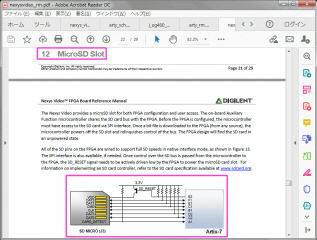

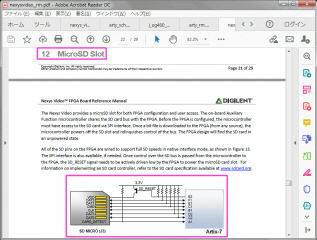

Nexys

VideoボードはSDカードからFPGAのコンフィギュレーションが可能です。コンフィギュレーション後はFPGAからもSDカードにアクセスできるように工夫されてい

ます。SDカードは大きいテーブルデータを格納するのに良いですが、MicroBlazeからSPIモードのSDカードコントローラとFATアクセスをする必要があります。

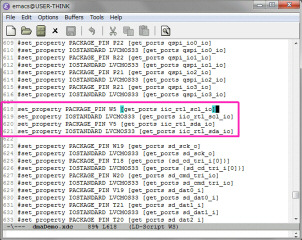

制約ファイルを変更し、デルタシグマDACの出力をPMODに変更します。フィルタボードを介して、音出し動作確認を行いました。動作良好です。

12月30日

リ

ピートDMAとHLSシンセをマージしてみます。動作させるのが目的ではなく、HLSで作成したIPが複数入っているHLSシンセを1つのIPにして

MicroBlazeのあるリピートDMAのブロックデザインに取り込めるかの確認です。簡単のため8チャンネルから2チャンネルに変更し、

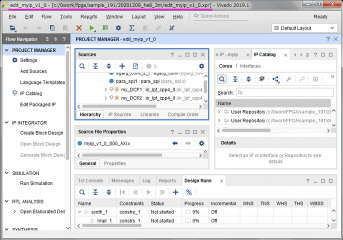

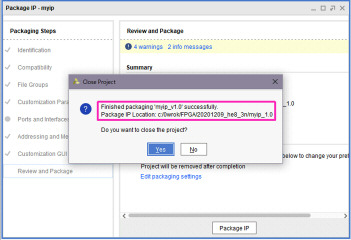

Verilogで書いてあるロジックを新しくmyipとして作成します。簡易IP作成機能を使います。Create And Package

IPを実行し、EDIT IPを選択して別ウインドを起動します。

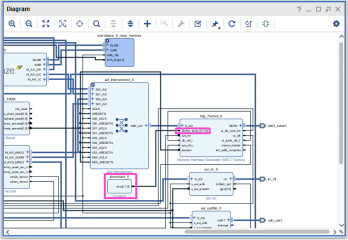

サブモジュールはVerilogソースをHLSのIPはXCIファイルをソースとして追加します。HLSで作ったIPはIPカタログに無いと言われるので、IPカタログからIPを追加して、ジェネレートします。ソースのウインドの?と鍵のマークが消えます。

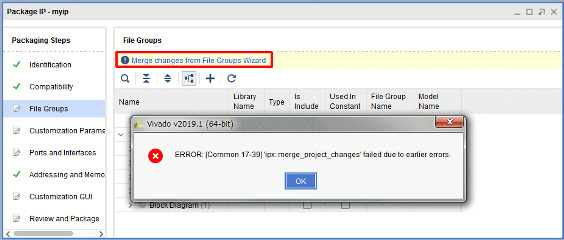

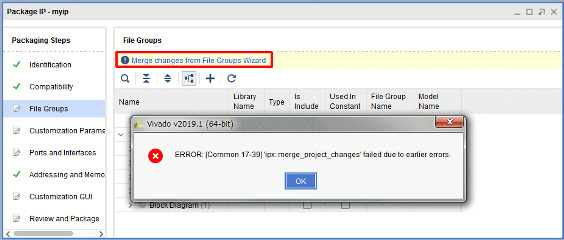

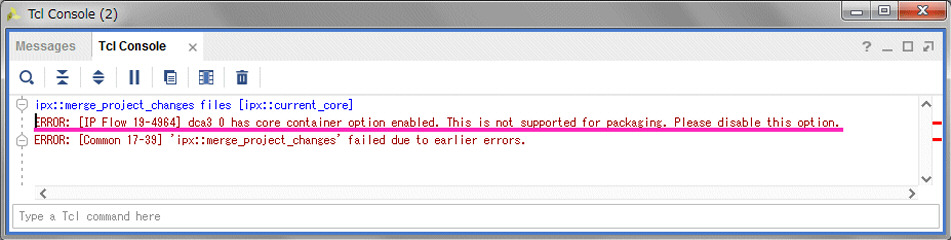

パッケージIPのファイルグループでマージを行うと、以下のエラーが出ました。

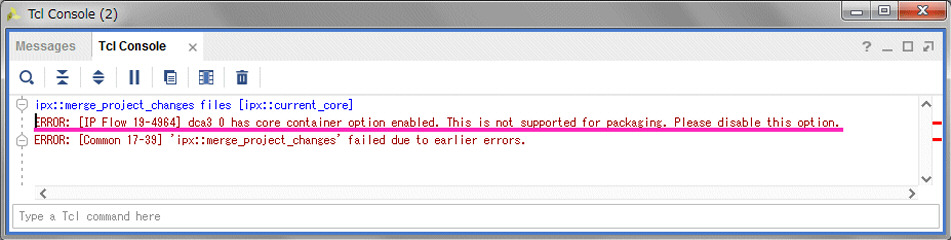

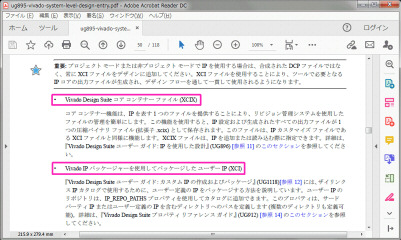

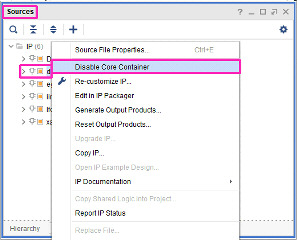

TCLコンソールでエラーを確認します。DCAのIPがコアコンテナになっているので、ディゼーブルにしろ、ということです。

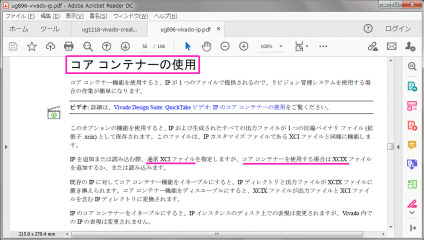

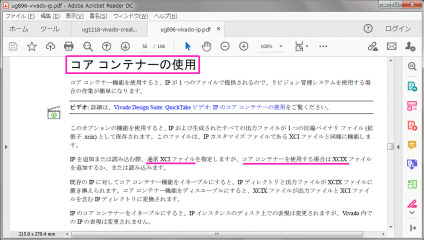

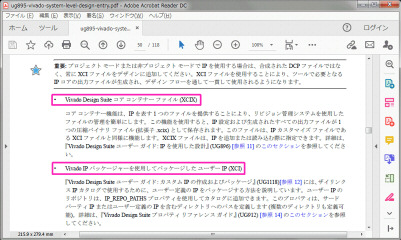

ドキュメントを確認します。コアコンテナはXCIXファイル、通常はXCIファイルを使うと書いてあります。ソースの追加時にXCIファイルを指定しているので、コアコンテナになっていないはずですが〜

12月31日

アマゾンでFPGAマガジンの4号を購入しました。昔のISE環境でSPIマスタIPとFatfsでSDカードを制御する記事が載っています。

2021年

1月2日

お正月です。色々と調べたところ、コアコンテナをディセーブルにする方法がザイリンクスのユーザーガイド”IPを使用した設計”にコアコンテナのディゼーブルというのがありました。

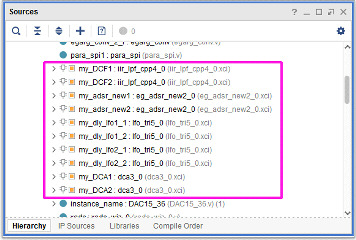

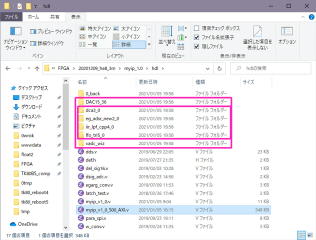

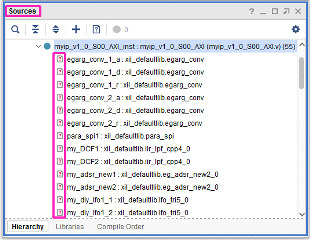

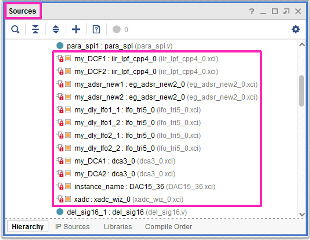

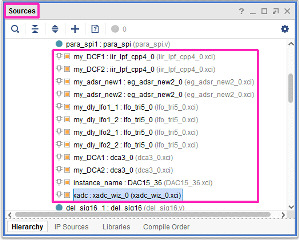

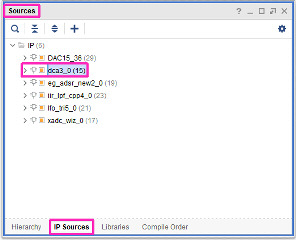

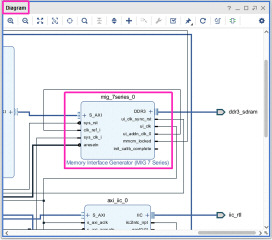

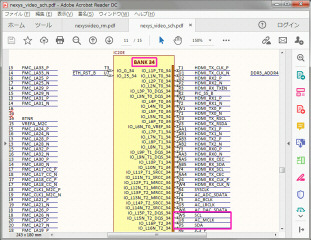

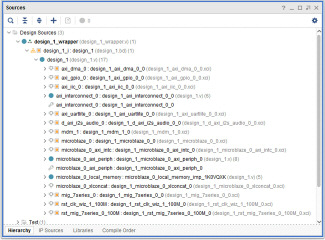

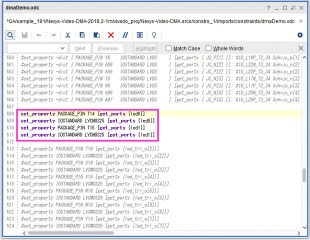

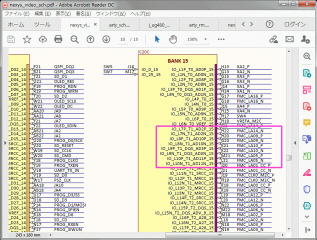

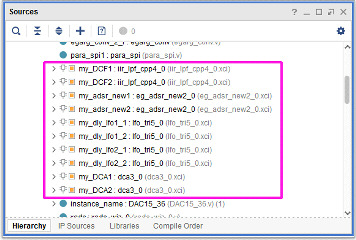

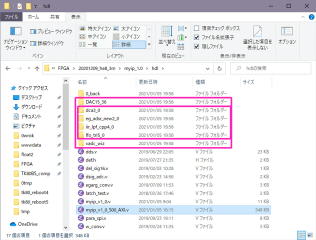

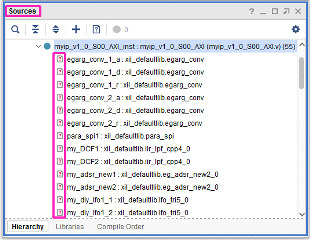

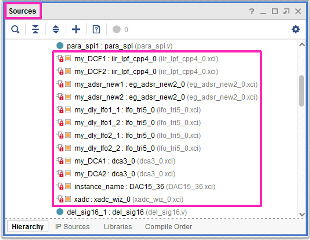

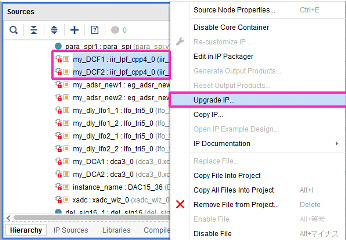

備忘録に、一通り手順を残しておきます。初めに、HLSシンセで使っているVerilogのソース、HLSで作成したIPをローカルにまとめておきます。2重枠の中がHLSで作成したIP、外枠は通常のIPです。その他、Verilogは本体から呼んでいるモジュールです。myip_V1_0_S00_AXI.vがHLSシンセの本体、myip_V1_0.vがラッパーです。

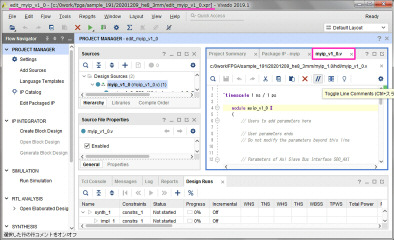

簡易IP作成機能のCreate And Package

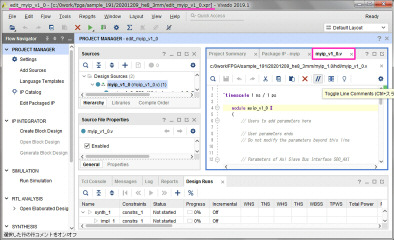

IPから、EDIT IPを選択して別ウインドを起動します。

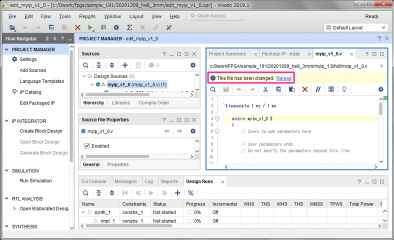

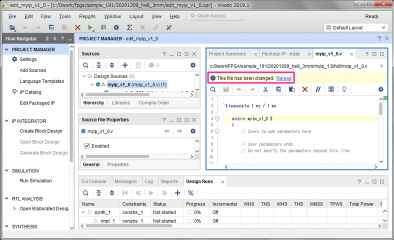

上位のラッパー、myip_v1_0.vを開いておいて、変更済みのファイルを上書きすると、変更されたことが認識されてReloadのボタンが出現するので、クリックしてセーブします。

Sourceペインで必要なソースの一覧が出現します。?マークが付きます。

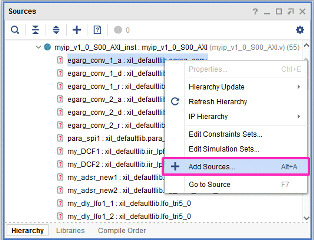

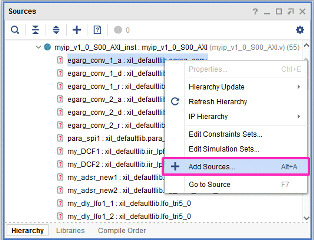

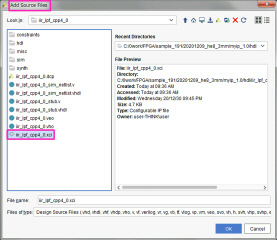

右クリックから、Add Sourcesを選択します。

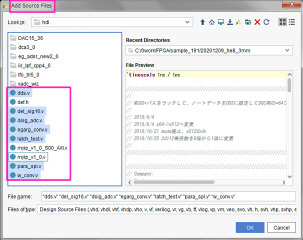

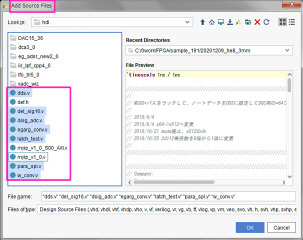

初めに、Verilogのソースを指定し、OKボタンを押します。

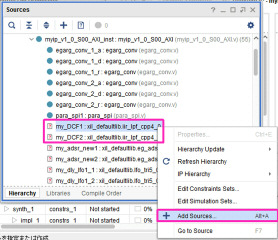

Sourceペインが更新され、Verilogで書いたモジュールは●マークになります。

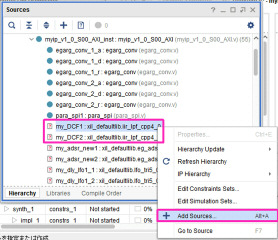

さらに、右クリックでAdd Sourcesを選択し、HLSのソースを追加します。

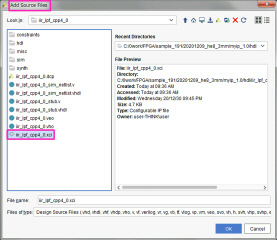

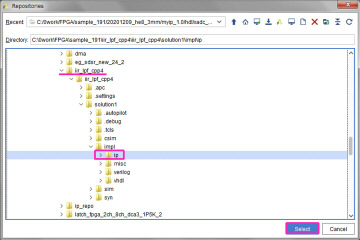

各HLSのローカルにコピーしたxciファイルを選択し、OKボタンで確定します。下図ではDCFのIPを選択しています。

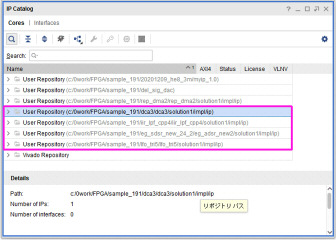

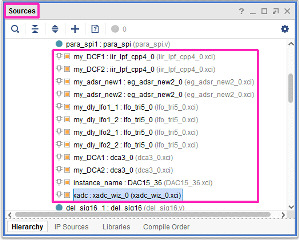

HLSで作成した4つのモジュールのDCF、EG、LFO、DCAのxciファイルを選択すると、下図のように鍵マークになります。

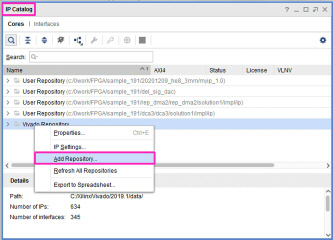

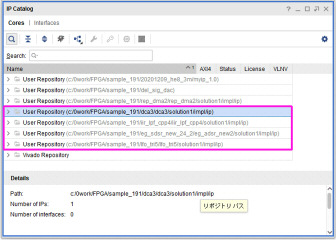

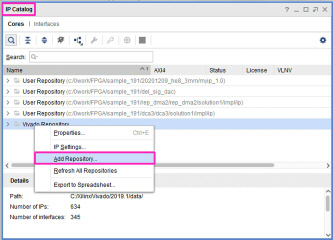

鍵マークはIPカタログにIPが登録されていないということなので、IPカタログでIPを追加します。

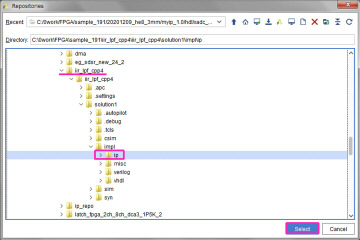

各HLSで作成したIPディレクトリを指定します。

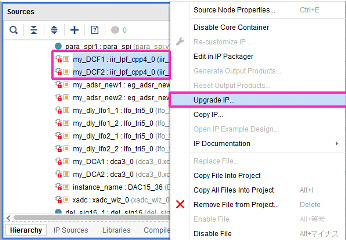

指定後、右クリックでUpgrade IPを選択します。

Generateボタンで生成します。

残りの3つのHLSモジュールも同じオペレーションでアップグレード/生成を行います。鍵マークが消えます。

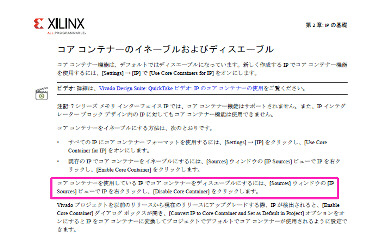

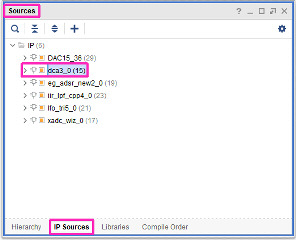

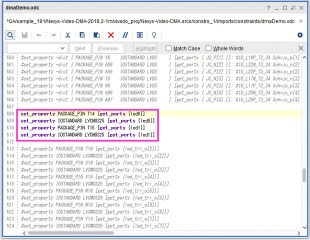

次が肝心のコアコンテナをディセーブルにする方法です。SourceペインのIP Sourcesタブに切り替え、HLSで作成したDCAを選択します。

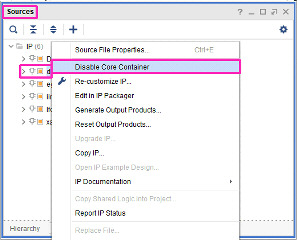

右クリックでDisable Core Containerを選択します。同じオペレーションで残りの3つのモジュールのDCF、EG、LFOのコアコンテナを全て解除します。

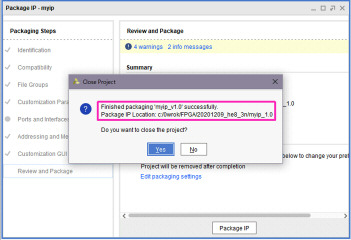

以上のオペレーションで新しいmyipの生成が完了しました。

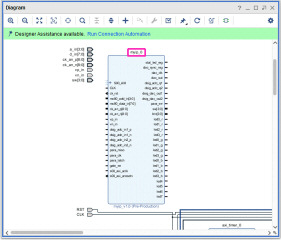

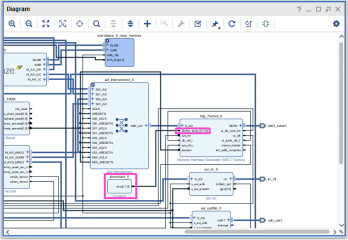

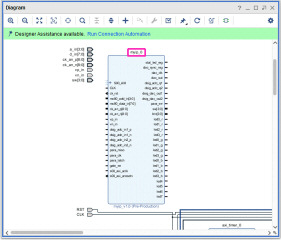

myip用のVivadoが閉じ、親Vivadoに戻るので、ブロックデザインで新しいmyipを追加してみます。中途半端に2ch化したmyipが出てきました。このIPは確認用に作ったものなので動作しません。

1月9日

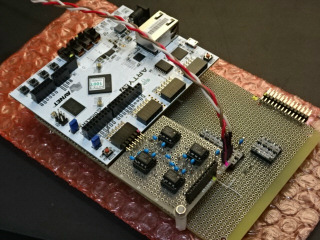

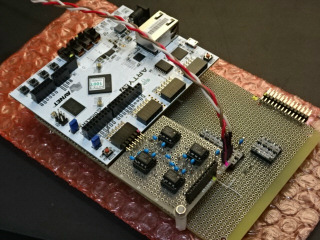

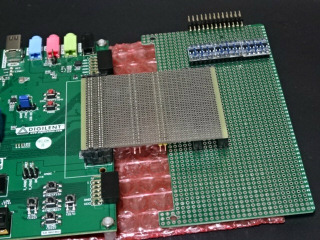

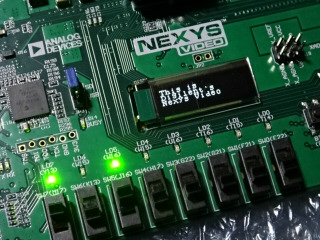

3連休です。秋月で購入したNexys Videoボードが到着しました。ARTY−7と比べると、箱が大きいです。12V電源が同梱されているからです。

FPGAにはヒートシンクが付いています。

同梱されていた12V3Aの電源です。PSEの関係でしょうか?秋月製です。

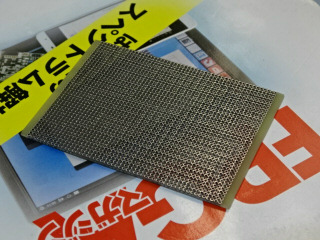

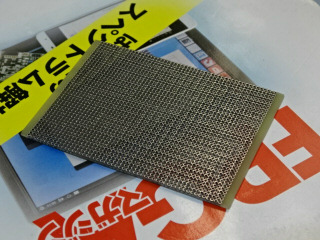

FMCコネクタを載せるハーフピッチのユニバーサル基板です。その他、フィルタボード用のコンデンサ、プラスマイナス5Vの絶縁電源は秋月です。DINコネクタのみマルツで購入しました。

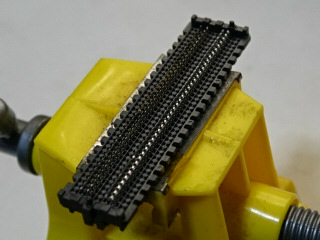

こちらはマルツ経由のDIGIKEYで購入のFPGAボードのFMCコネクタに勘合するプラグコネクタです。型番はサムテックのASP−134604−01です。価格は少し高くて、2400円くらいします。

以前に購入したタカチのアルミケースにFPGAボードを入れてみます。電源を外付けにすれば入りそうです。

1月10日

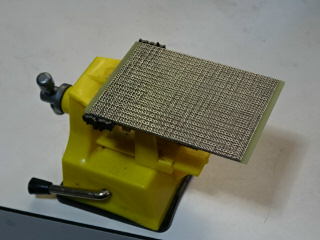

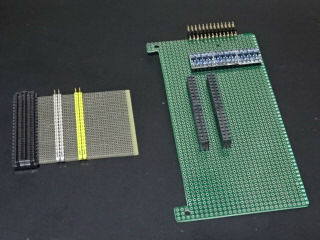

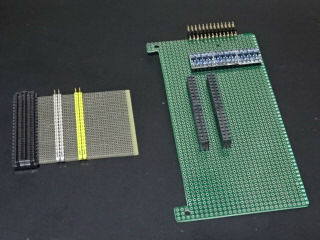

FMCコネクタ用にハーフピッチのユニバーサル基板を外形加工しました。

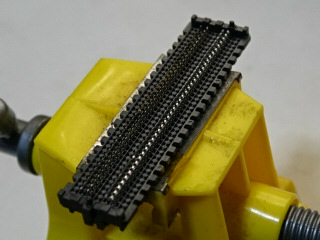

FMCプラグコネクタは表面実装タイプなので、端子の先端に半田ボールが付いています。半田吸収線でボールを取り除くと、ハーフピッチのユニバーサル基板に入れることができます。左は片側だけ半田ボールと取ったところです。

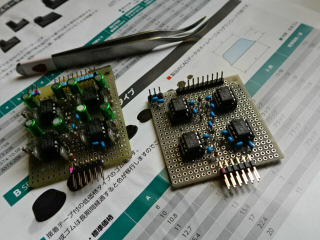

先週、4チャンネルまで作製して、コンデンサが不足していたデルタシグマDAC用のフィルタボードの残り4チャンネルを作製して完成しました。手前が新しいフィルタボードです。

アナログディスカバリで残りの4チャンネルの動作確認を行いました。動作良好です。

1月11日

FMCコネクタのボードに40ピンのピンヘッダを2個実装します。180ピンのうち半分の80ピンを接続できるようにします。相手側のベースボードも作製しました。FPGAボードの固定穴を2個使って固定します。使用するピン数はMC80バスが8+4=12、ゲート、LFOのLEDが8x3=24、XADC=8、合計44です。MC80バス用の5V−>3.3Vのレベル変換を実装します。

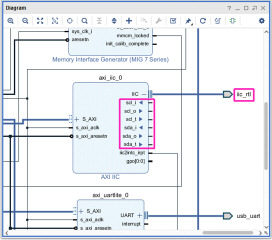

年末のNexys Videoボード用のDMAのIPを使ったI2Sのデモプロジェクトです。MIGの温度入力をデフォルトに戻しました。

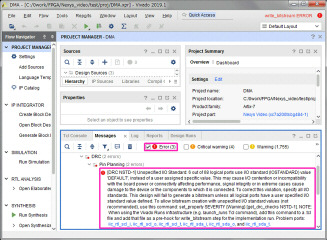

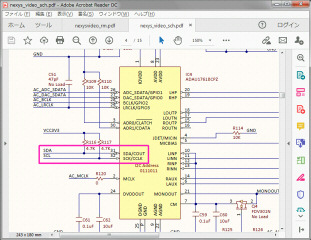

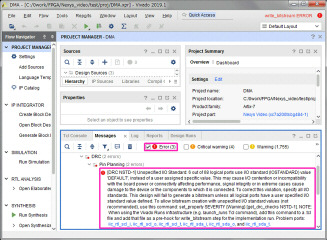

2019.1のVivadoでビットストリームを生成すると下のエラーが出ました。I2C周りのエラーです。

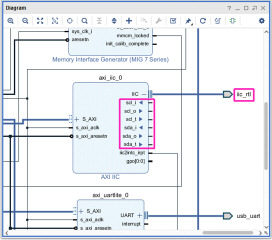

気になったので、ブロックデザインでiic_rtlのを確認すると、6本の信号線が接続されていてます。ブロックデザインではI2Cのスリーステートドライバが無い状態です。

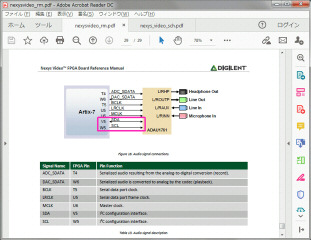

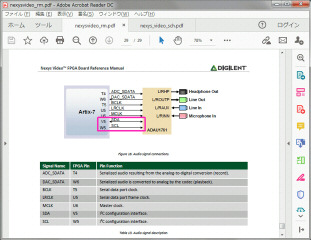

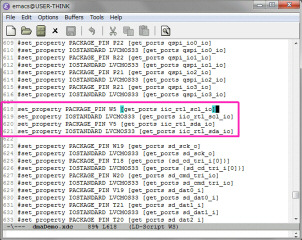

リファレンスマニュアルと制約ファイルではIICはSDAとSCLの2本の信号線になっています。

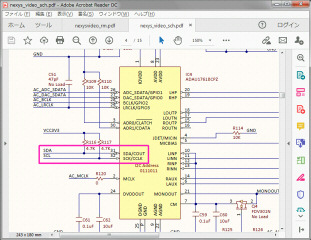

回路図でも同等にSDAとSCLの2本の信号線です。何処かの段階で上手く、スリーステートバッファが推論されるようです。

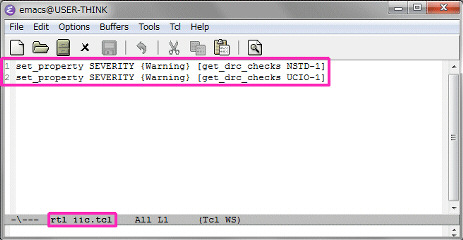

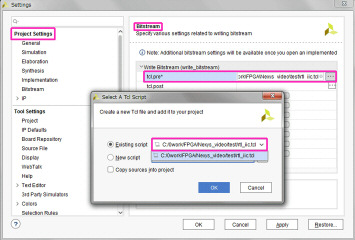

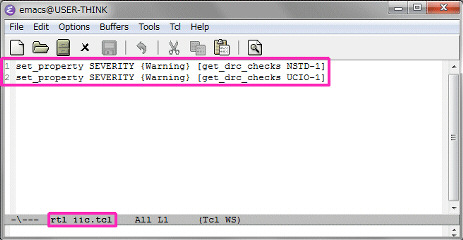

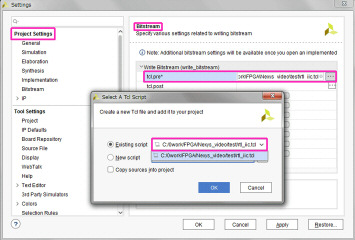

エラーの回避方法はザイリンクスのWEBにあり、TCLファイルを作って、Vivadoのビットストリームに設定すると回避できます。

1月12日

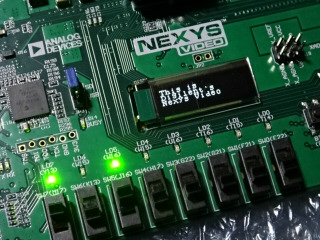

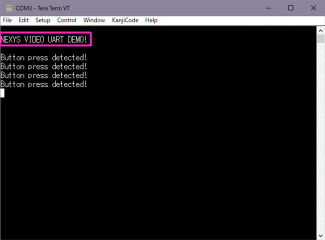

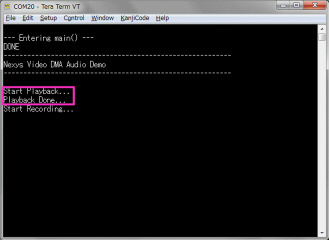

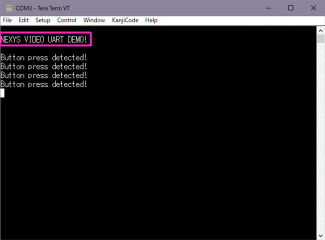

アパート作業です。上記のDDR3とI2SのDMAのIPを使ったデモはSDK内でMicroBlazeが停止せず、上手く動かないため、まずは一番簡単なGPIOデモでボードの動作確認しました。プロセッサ無しのハードロジックです。8個のLEDがスライドスイッチに対応して点灯し、小さなOLEDパネルに文字が出ます。ブッシュスイッチはUARTにイベントが送信されます。上記のDMAのIPを使ったデモもGitHubにVivadoのプロジェクト形式でありました。GitHubの方がDIGILENTのページより新しいプロジェクトです。

1月16日

サウンドハウスでミキサを買った時のポイントが消滅しそうだったので、ケーブルとフォーンコネクタを購入しました。ケーブルは3m長で10色です。

Nexys

VideoボードのDDR3とI2SのDMAのIPを使ったデモの続きです。古いノートにデモのバージョンと同じ2018.2のVidadoが

入っていたので、このバージョンで合成/インプリしたところ、SDKからMicroBlazeが制御できました。ただし、デモの動作で録音がうまくいきま

せん。5秒で録音が終了するはずですが、停止しませんでした。

1月17日

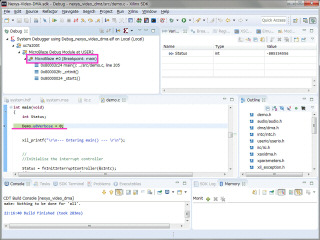

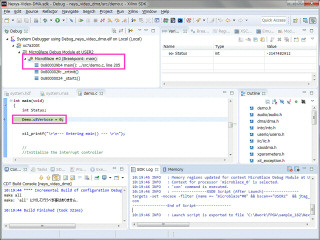

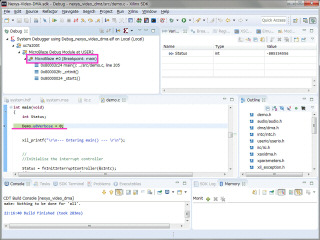

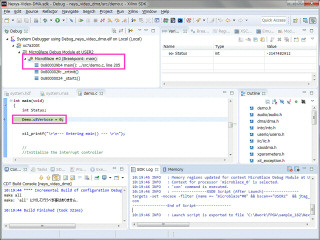

2019.

1で合成/インプリした場合は、下のSDKの起動直後にMicroBlazeが走っている状態で制御できません。ただ、ボードの電源投入直後に稀に動作

する場合もあります。

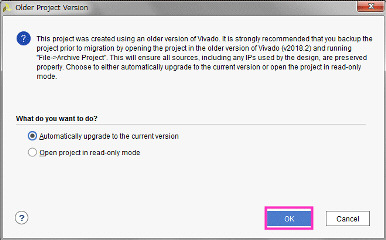

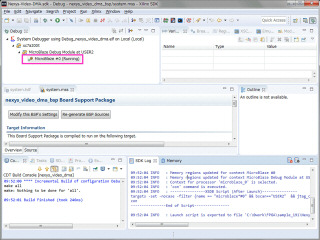

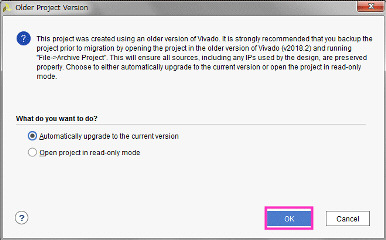

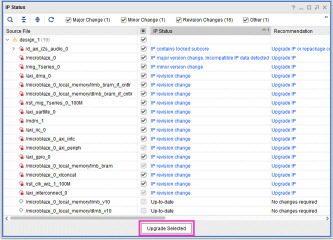

2018.2用I2SのDMAのIPを使ったデモプロジェクトを2019.1に読み込んだ時の手順です。自動的アップグレードするか確認が出るので、OKを押します。

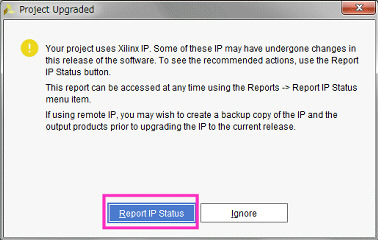

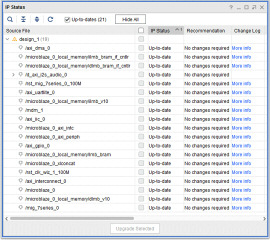

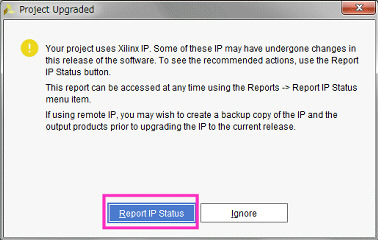

IPステータスの状態を表示させるか確認が出るので、Report IP Statusを押します。

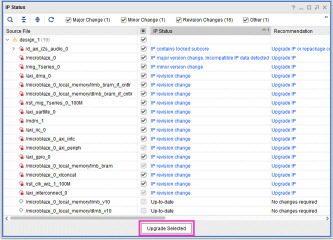

各IPのバージョンが表示され、アップグレードが必要かどうか、赤鍵マークで表示されます。Upgread Selectedを押します。

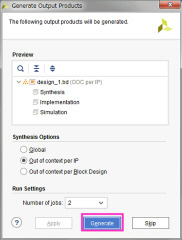

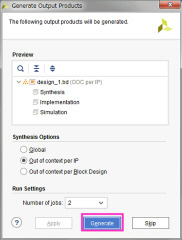

アップグレードが終了すると、ジェネレーションを行うか確認が出ます。デフォルトのOut of context per IPを選んでGenarteを押します。

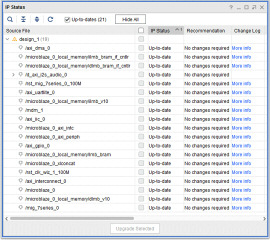

IPのアップグレードが完了すると赤鍵マークが消えます。

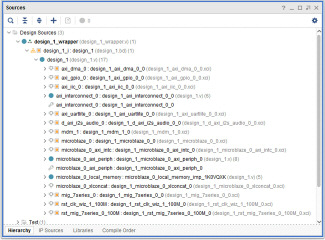

ソースペインのIPの階層表示でIPが正しい状態になります。この後、合成/インプリを行い、ビットストリームをSDKにエクスポートします。

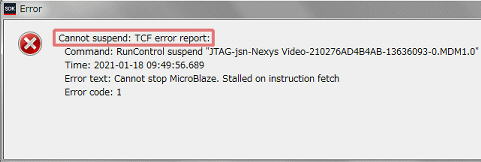

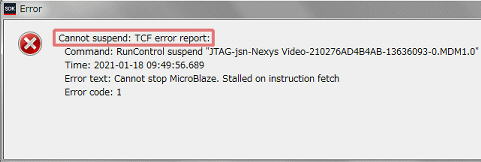

SDKを立ち上げると、MicroBlazeが制御できない状態になります。このプログラムはリセットベクタがSRAMにある以外はDDR上に動作するようになっています。多分、制御できないのはDDR

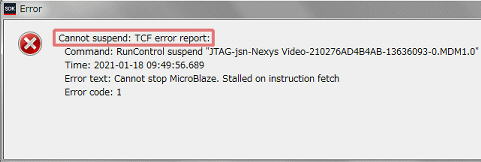

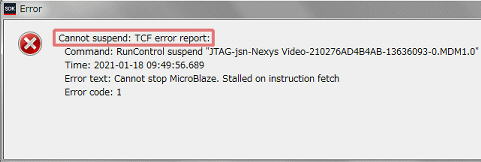

の初期化が正しく行われないからだと思われます。停止ボタンでさせると以下のエラーが出ます。再度、FPGAにロジックをダウンロードする以外のオペレーションはできません。

Nexys

VideoボードのDDR3の問題点のまとめ

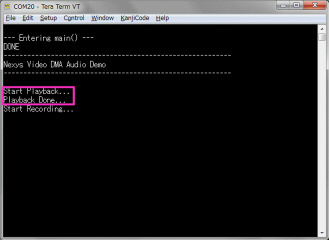

・2018.2でI2SのDMAのIPを使ったデモで録音が停止しない。(DDR3は動作してます)

・2019.1でI2SのDMAのIPを使ったデモのSDKでMicroblazeが停止しせず、制御できない。(稀にできる場合もある)

1月19日

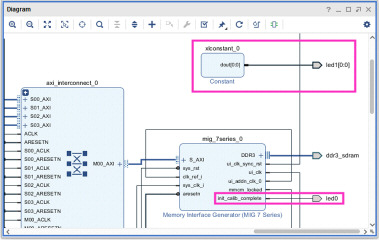

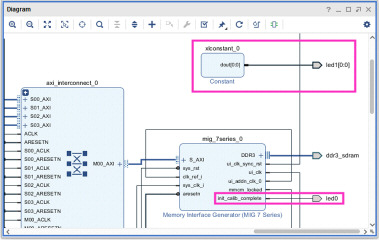

アパート作業です。MIGにはDDRのキャリブレーションが正しく行われたというinit_calib_completeステータス出力があります。アクティブHighなので、LED0に接続します。ロジックが正しく更新されたことが分かるように、もう一つLED1を使って、無条件に点灯させます。

制約ファイルのLED0と1を復活させます。

初めに2018.2で合成/インプリしたロジックをダウンロードします。こちらは、少なくとも、プログラムが動作しているので、DDRは正常に動作していると思われます。予想の通り、LED0/1が点灯しました。

TeraTermにメッセージも出力され、録音しないで、プレイボタンを押すと5秒間ノイズが出力されます。残念ながら、録音は停止しません。

続いて、2019.1で合成/インプリしたロジックです。予想に反して、LED0が点灯しました。DDR3は正しく動作しているようです。DDR

の初期化が正しく行われないためにMicroBlazeの制御ができないというのは間違えでした。

1月21日

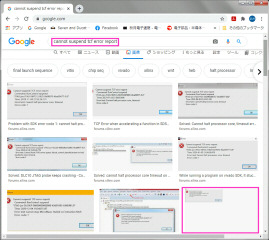

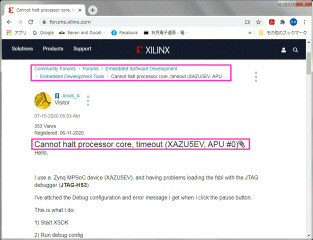

アパート作業です。DDR3とI2SのDMAのIPを使ったデモでMicroBlazeが止まらない不具合の続きです。エラーのポップアップウインドの”Cannot Suspend: TCF error”をキーワードにGoogle検索します。

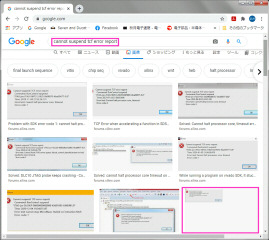

検索の種類を画像にして検索すると、同じような不具合が多数ヒットします(笑)。文字で検索したよりもヒットの数が多いようです。内容を確認して、現象が似ているものを探します。

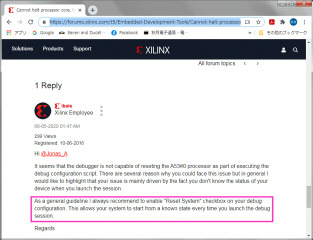

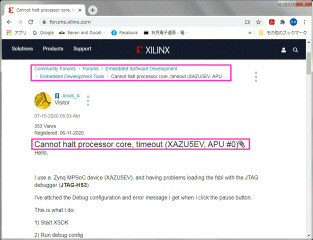

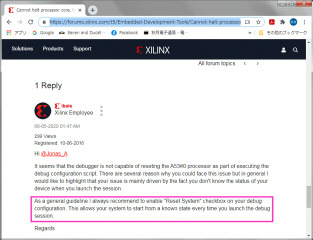

9個目に、MicroBlazeでは無く、Zynqですが、ここにに解決策のそれらしい物がみつかりました。”SDKのデバッグ設定で、リセットシステムを設定しろ”という回答です。

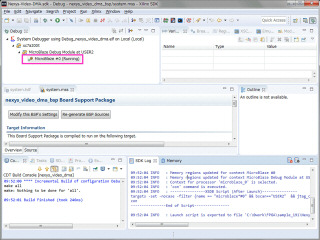

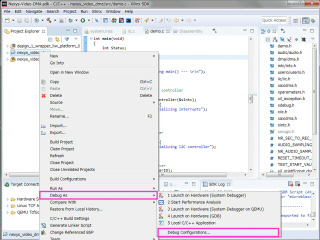

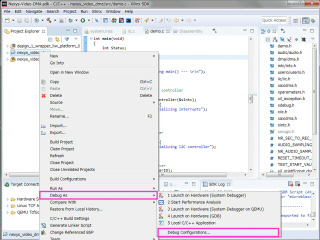

早速、2019.1のSDKのデバッグ設定を確認してみます。

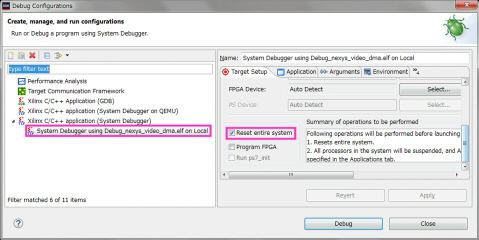

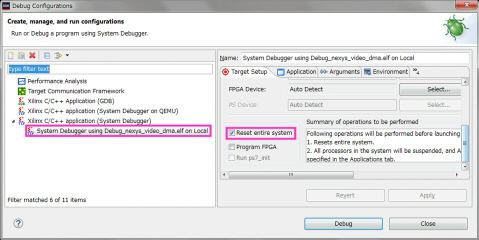

”Reset entire system”というチェックボックスがあり、これにチェックします。

この設定により、2019.1のSDKのデバッグ開始時にMicroblazeが停止して、制御できるようになりました。また、録音が5秒で停止しない不具合も直りました。ただ、先頭部に短時間のノイズが録音されています。2018.2のSDKのデバッグ設定のチェックボックスも外れていました。Vivadoのバージョンにより、微妙なタイミングの違いがあり、2018.2では動作していたと思われます。