TK80/BSの

シンセシステムを復活/拡張したい〜

その29

EGとLFOの実験、DCAの追加

2018年

2018年

9月29日

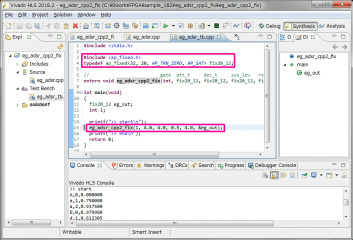

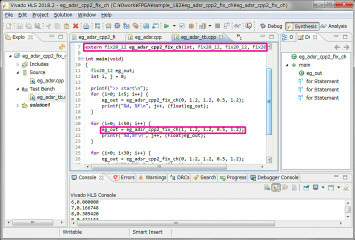

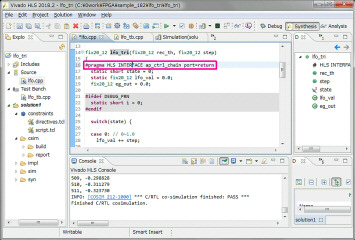

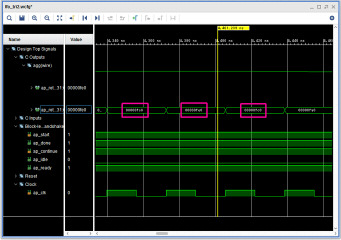

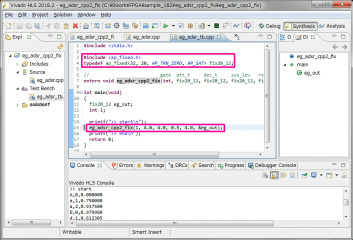

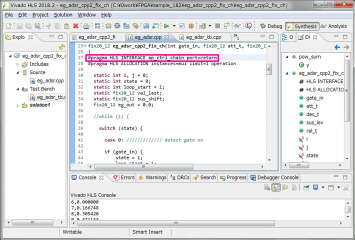

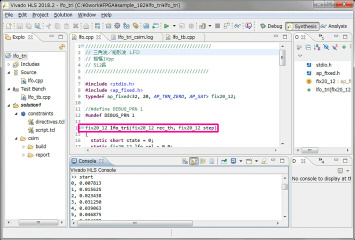

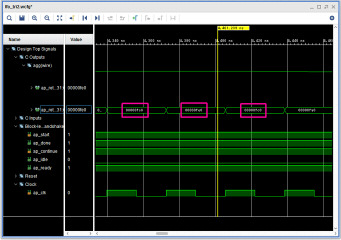

先週からのエンベロープジェネレータの続きです。浮動小数点の部分をすべて固定小数点に変更し、アタック、ディケイ、サスティーン、リリースを引数で設定できるようにしました。下はテストベンチです。

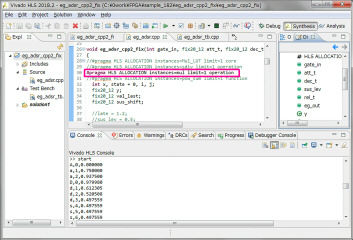

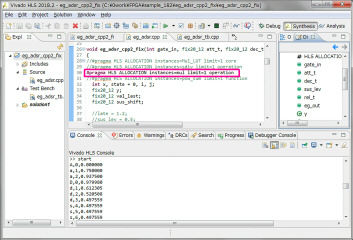

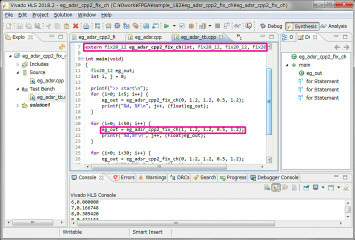

最適化指示は色々と試したところ、同時に動作する乗算を1個に制限すると、リソースが少なくなりました。その他は効果ありませんでした。

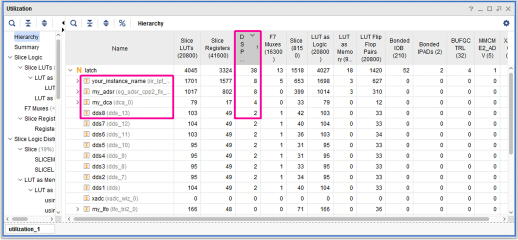

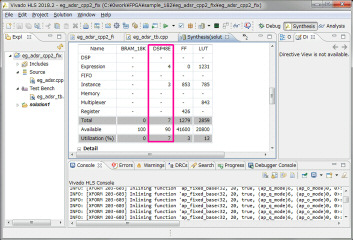

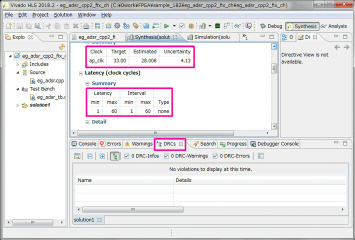

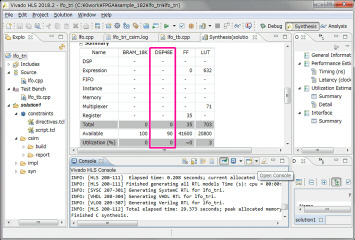

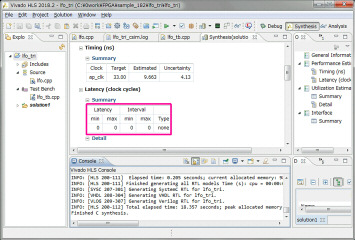

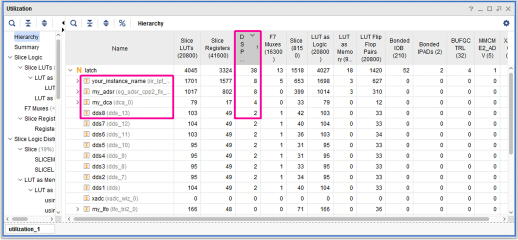

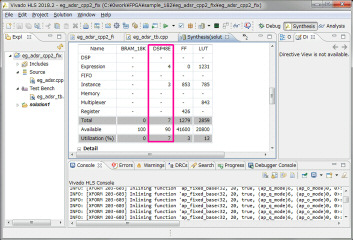

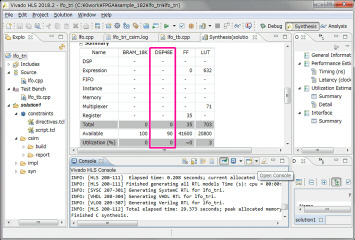

合成後、リソースを確認します。DSP48Eは7個使用しています。

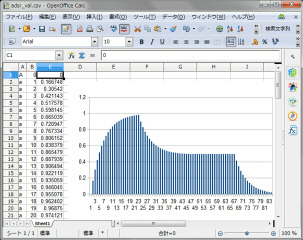

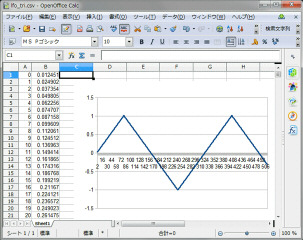

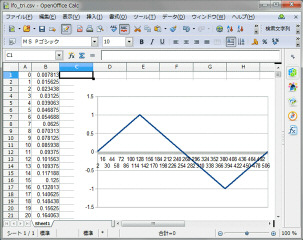

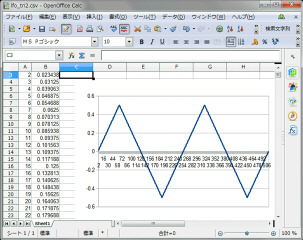

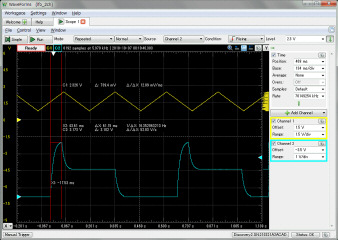

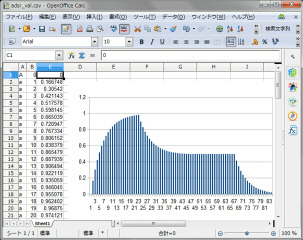

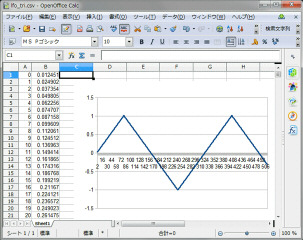

C/RTLシミュレーションの結果をグラフにしました。動作良好です。

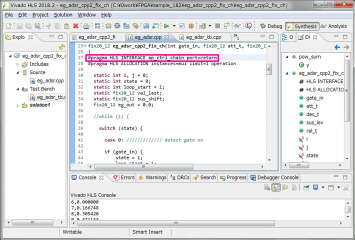

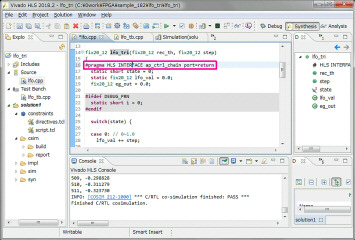

上記のエンベロープジェネレータは戻り値が無く、出力結果はポインタ渡しの変数に逐次、代入されます。これではタイミングが制御しにくいので、ラダーフィルタと同じく、出力結果を戻り値で返し、外部からタイミングを制御できるようにap_ctrl_chainインターフェースに変更します。この変更により、関数は1回づつ、戻り値を持って戻るように修正します。

テストベンチでは前後にゲートオフの部分を挟んで、ゲートオンで関数を複数回呼んでテストします。

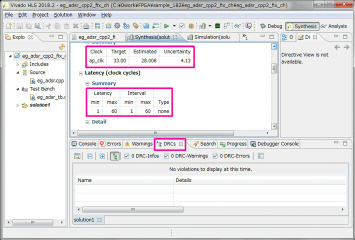

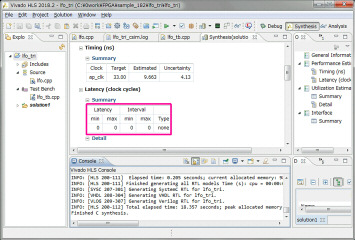

合成後、タイミングを確認しておきます。サスティーン中は計算が少ないためか、レイテンシが1〜60と幅が大きいです。

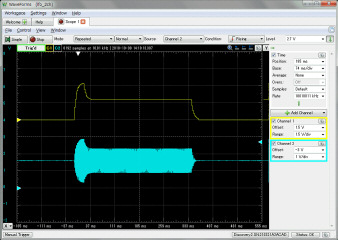

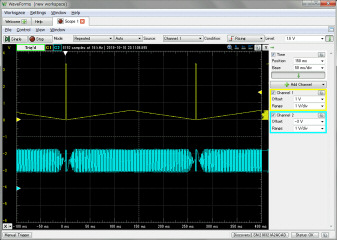

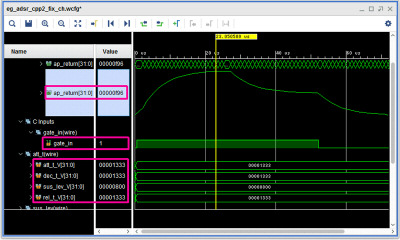

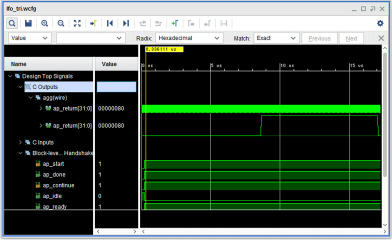

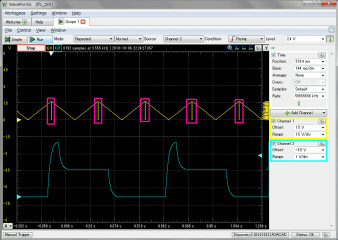

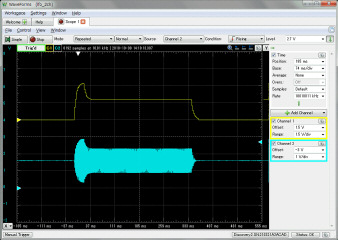

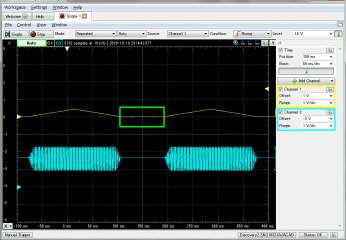

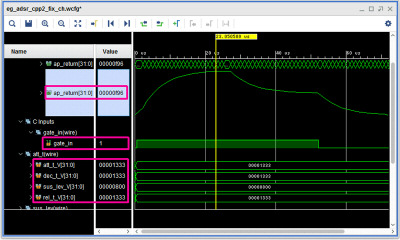

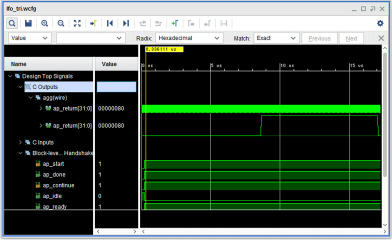

波形を確認します。戻り値をアナログ表示してみました。動作良好です。

9月30日

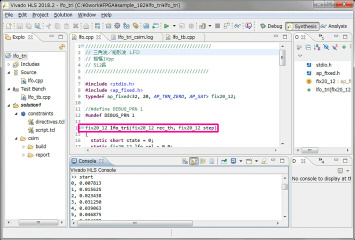

エンベロープジェネレータが良さそうなので、続いてLFOを作ってみます。SIN波はリソースを食いそうなので、三角波と矩形波のみ実装してみます。三角波と矩形波はmode引数で切り替える仕様で、同時には出力できません。慣れてきたので、cygwinのCでプログラムせず、初めからHLSの固定小数点で作ります(笑)。

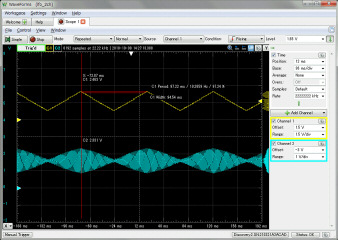

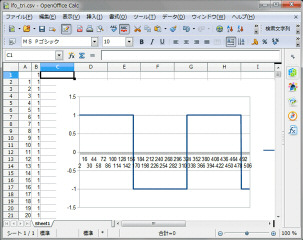

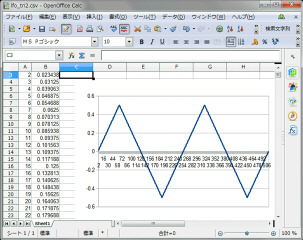

シミュレーション結果をオープンオフィスで波形にして確認します。振幅は+1.0〜−1.0です。周波数の設定は引数のstepで設定します。

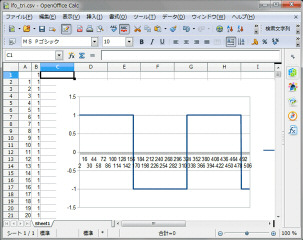

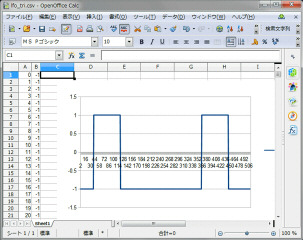

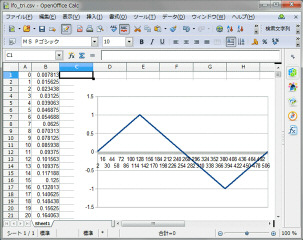

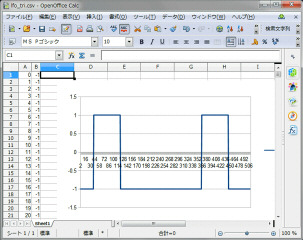

mode引数(矩形波の閾値兼用)でモードを矩形波にしてみます。矩形波では閾値を変えてPWMもできます。右は閾値0.5の時です。

リソースを確認すると、乗算器は0でした。

こちらも、エンベロープジェネレータと同じく、外部からタイミングが制御できるように、ap_ctrl_chainインターフェースに変更します。

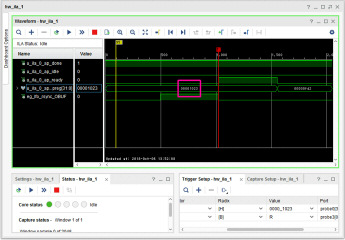

合成後、タイミングを確認しておきます。主に、加算器とコンパレータなので、レイテンシが0、インターバルが1です。

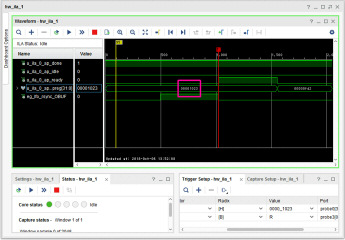

波形を確認します。出力はfix20_12の合計32ビットの+1.0〜−1.0で符号付です。小数点部の下位しか動かないため、アナログ表示は変な表示になっています。

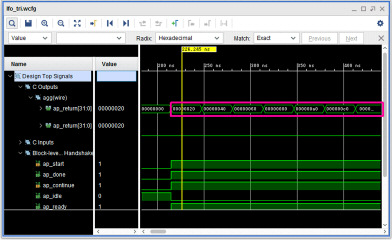

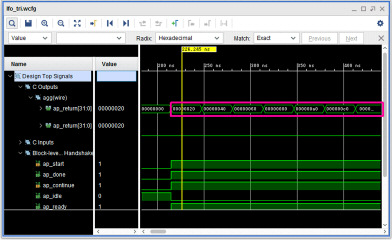

データを詳しくみると、小数点部がインクリメントされていて正常のようです。ap_ctrl_chainインターフェースの各ハンドシェイク信号はレイテンシが0、インターバルが1のためか、関数を呼んだ分のパルスが出ず、1個になっています。この日は台風接近のため、午後4時にガレージを出ました。アパートでは音出しはできませんが、アナログディスカバリを使って簡単なテストはできるので、ラダーフィルタの論理にエンベロープジェネレータとLFOを追加して動作確認する予定です。

10月6日

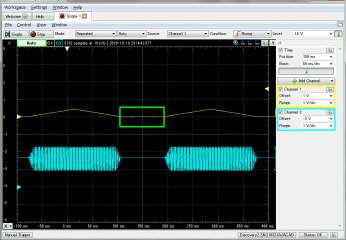

LFOとEGの出力をSPI−DACへデバッグ出力して確認します。EGはゲートを疑似的に入力してテストします。双方とも小数点部をシフトして、SPI−DACに出力します。LFOの出力がオーバフローしています。

最大値を1.0から0.992Vに少し小さくしました。HLSのシミュレーション波形では最大値は1を超えていないです。

IP組み込み後にVivadoデバッグ用のロジックアナライザでいろいろと調べると、1を超えていると時があります。不思議です。

10月7日

とりあえず、LFOの振幅を0.5〜−0.5に小さくして、再IP化しました。

SPI−DACへのデバッグ出力して、再確認します。当然ですが、LFOもオーバフローせず、正しく出力されています。

10月8日

EGのADSRに対応させるためにXADCに接続している、ボリュームを4個にしました。プッシュボタンでラダーフィルタとEGとLFOを切り替えて、パラメータを設定します。

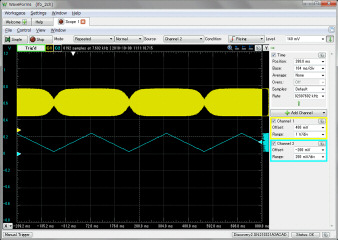

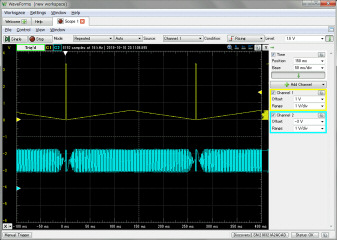

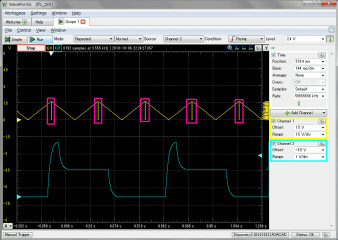

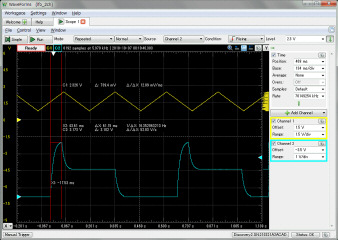

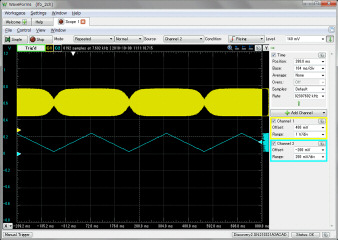

ロジックを修正して、ラダーフィルタをLFOとEGで変調できるようにしました。下はLFOで変調した時です。

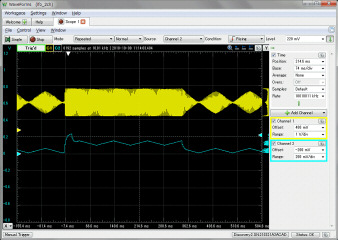

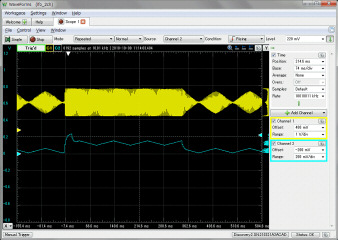

続いて、EGで変調した時です。カットオフレベルを低めにして、EGで大きく変調すると、DCA的な動作になります。

EGとLFOをミックスしてみます。ただし、オーバ、アンダフロー未対応のため、設定によっては、異常値になります。これは対策が必要です。

、

、

以前のグラスに続いて、今回は100円ショップの200円の耐熱カップをTK80のロゴでサンドブラストします。

完成しました。カップ底のμCOM−80のロゴはミラー反転させ、上から覗いた時に、普通に見えるようにしました。沸騰したお湯を入れて割れないことを確認しました。

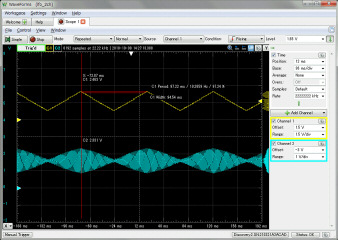

HLSでDCAを作成してIP化後、パラメータの設定も共にロジックに追加しました。DCAは出力、入力、CVともfix20_12フォーマットの単純な乗算器です。LFOで変調してみます。

続いて、EGで変調します。ラダーフィルタと同様にLFOとEGをミックスできます。

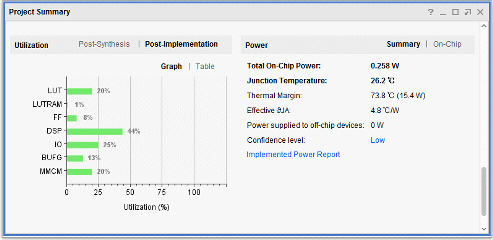

現状で基本動作しているFPGA内のシンセモジュールはDDS/DCO(方形波のみ)、DCF(ラダーフィルタ)、EG、LFO、DCAです。リソースの内、当初から不足気味の

DSP48Eは22個/chです。35TデバイスのDSP48E数は90個なので、4ch分しか入りません。100Tデバイスは240個で足りそうです。

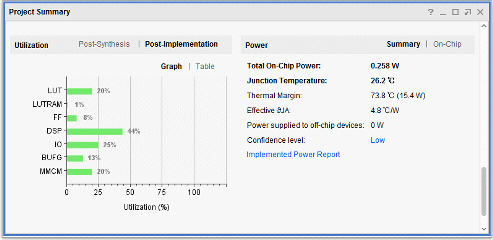

リソースをグラフで確認しておきます。

ソースウインド内の階層とライブラリの現状です。

以下、追加予定の機能です。

<DDS/DCO>

・LFO変調

・ノコギリ波を追加

・方形波を廃止してPWMに変更(LFO、EGで変調可)

・1/2、1/4.1/8分周波の生成と上記ノコギリ、PWMとのミックス

・外部入力用のSPI−ADC追加、DCO信号とのミックス

<LFO>

・ゲートシンクロディレイドLFO

<パラメータ入力SPIインターフェース>

・MSP430制御のロータリエンコーダと128x64ドットLCD

10月10日

アパートのPCで作業します。ラダーフィルタとDCAの制御値がアンダーフローしないように対策します。下はダラーフィルタの動作です。左は未対策、右は対策後です。予めLFOの加減算を行い、アンダーフローが発生していたら、0でクリップさせます。

、

、