TK80/BSの

シンセシステムを復活/拡張したい〜

その37

FPAGシンセの作製

2019年

2019年

4月6日

FPGAとMSP430の開発用ノートPCのキーボードが調子悪いです。’L’のキーが連続で入ります。消える寸前のポイントがあったので、ヤフオクでキーボードを購入し交換しました。キーボードも調子よくなったので、先週からの続きのEGの不具合を修正します。

4月7日

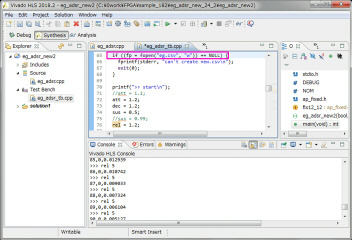

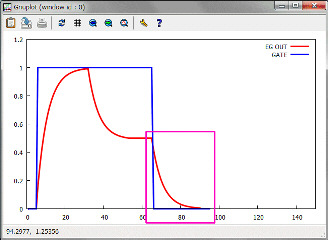

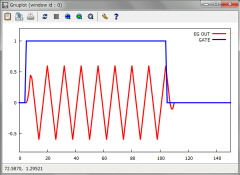

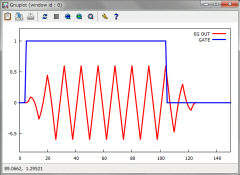

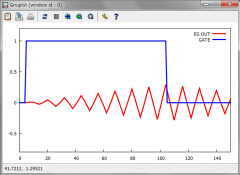

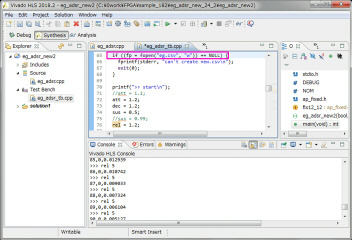

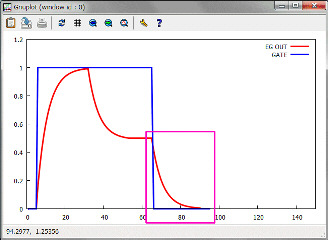

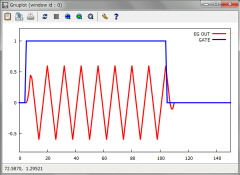

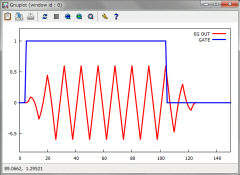

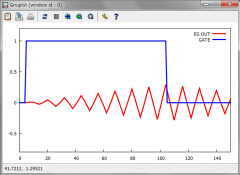

HLSのシミュレーション出力結果をコピーしてオープンオフィスのCALCで確認するのは面倒なので、テストベンチからゲートとEGの出力をCSVファイルに出力します。テストベンチ内のfopenで生成されるファイルはパス無しの場合、プロジェクトの下の”solutionX/csim/build”に出力されます。直ぐ忘れてしまうので、備忘録として書いておきます。gnuplotでCSVファイルを読み込んで、ゲートと重ねて出力します。時間がかかりましたが、不具合箇所が判明し修正しました。分かりやすいようにIPの名前の後ろに2をつけておきます。

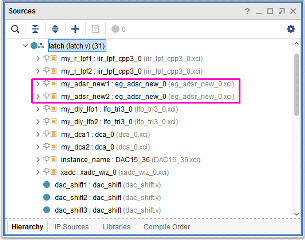

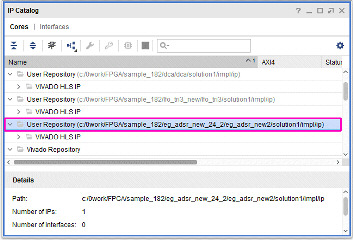

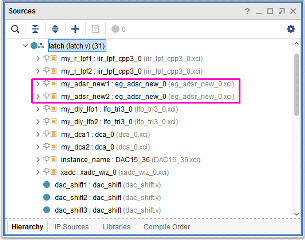

EGが直ったところで、VivadoプロジェクトのFPGAシンセに組み込まれているEGのIPを修正した新しいものと入れ替えます。下は現状のIPです。はじめに、これを削除します。

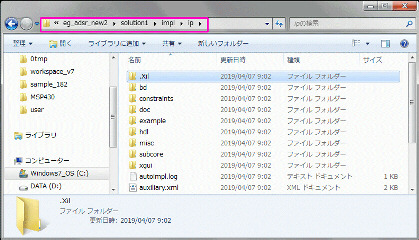

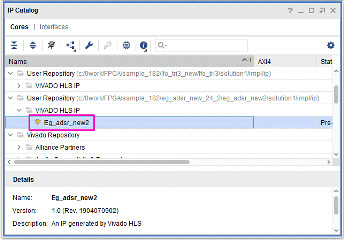

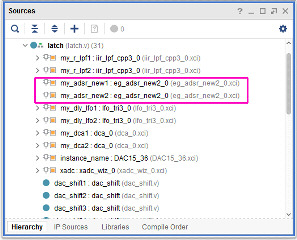

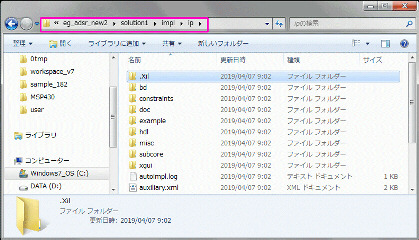

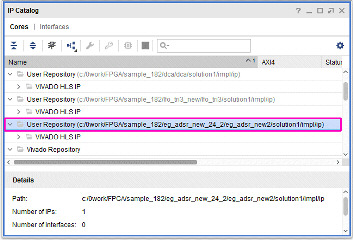

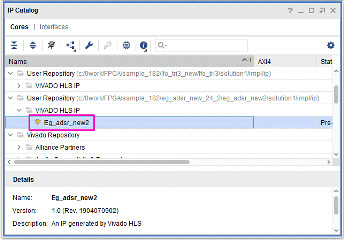

HLS内でRTLをエクスポートするとIP一式が左のようにプロジェクトの”solutionX/impX/ip”に出力されます。VivadoからIPカタログを起動し、古いIPを削除して、新しく作成した"eg_adsr_new2”を右クリックで追加します。

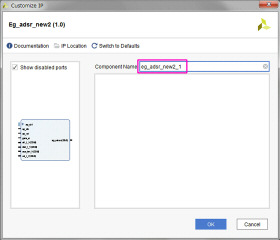

IPを展開して、ダブルクリックします。

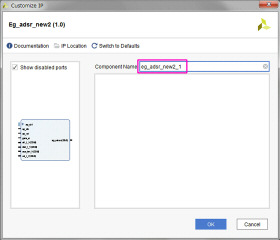

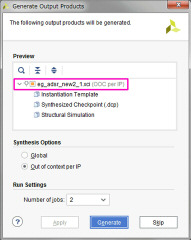

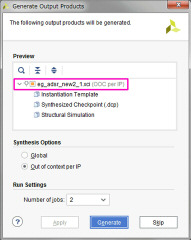

”Customize IP”のウインドが出るので、OKを押します。その後、”Generate Output Product”のウインドが出るので、Generateを押してジェネレートします。

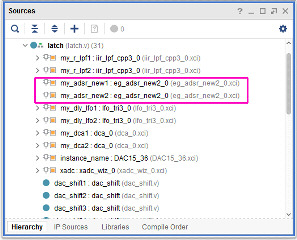

少し待っていると、階層表示に修正したIPが出てきます。当然ですが、IPの名前を変更したのでロジック内の呼び出し名も変更します。その後、合成、インプリしてビットデータを生成します。

FPGAに書き込んで、動作確認します。リリースの減衰波形が直りました。タイミングも他と同じように伸びるようになりました。

続いて、最小でもアタックが長い件です。8ビットのパラメータ値が程良い調整範囲になるように、整数部12ビット、固定小数点部12ビットの値にマッピングします。約8mSecまで短くなりました。

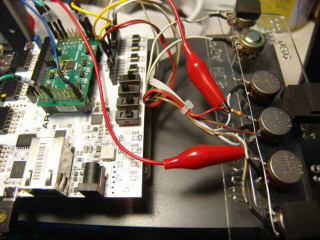

次は最大でもサスティーンが低い件ですが、XADCの保護用に入れていた抵抗が原因でした。ワニ口クリップでスキップしたところ、ほぼ解消しました。

4月13日

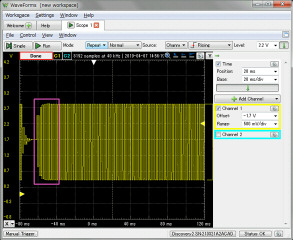

ディレイドLFOのアタックとリリースの調整範囲を広くしました。8ビットのパラメータを整数部12ビット、固定小数点部12ビット引数の良さそうな位置にマッピングします。HLSのテストベンチでCSVファイルを出力して、GNUPLOTでタイミングを確認します。下は時間係数が約0.25で最短の時です。

続いて、時間係数が約0.05の時です。

続いて、時間係数が約0.005の時です。また、リリースもアタックと同様にタイミングで出力されることを確認しました。

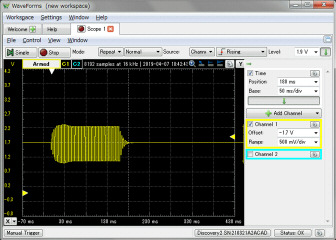

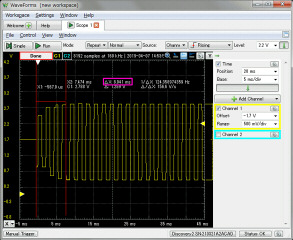

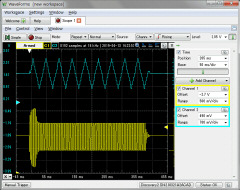

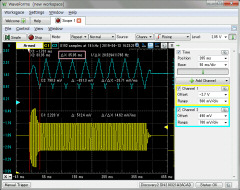

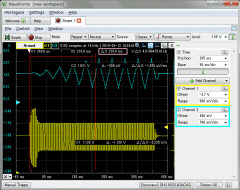

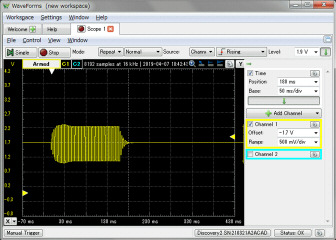

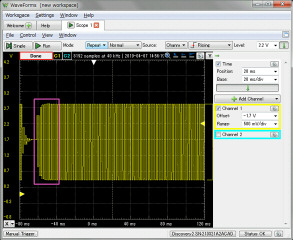

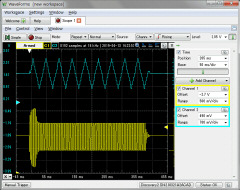

Vivado内で新しいLFOのIPに更新し、実際にLFOの出力を確認します。上の緑がデバッグ用のSPI−ADCから出力したLFO出力で、下がデルタシグマDACで出力したシンセ出力です。はじめに、パラメータの設定ボリュームが最小の時です。

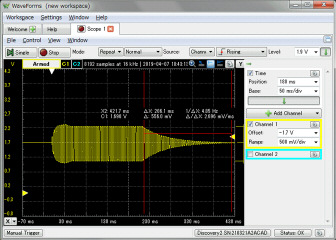

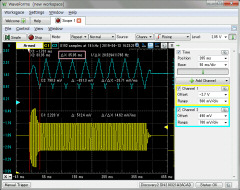

続いて、ボリュームが12時の位置です。

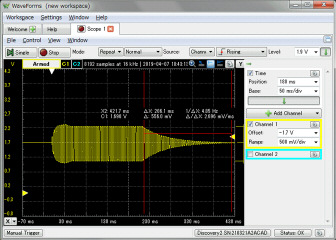

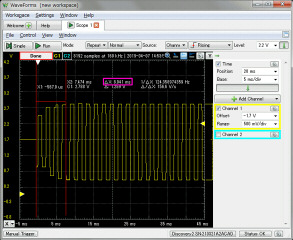

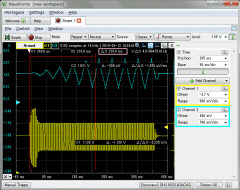

続いて、ボリュームが3時の位置です。調整範囲が広がりました。

4月14日

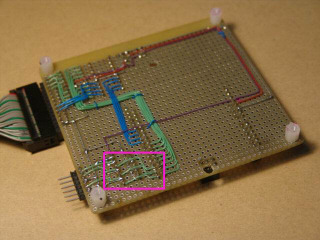

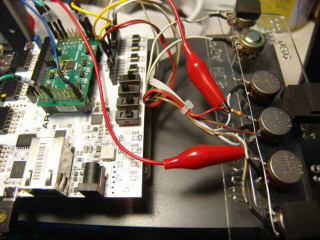

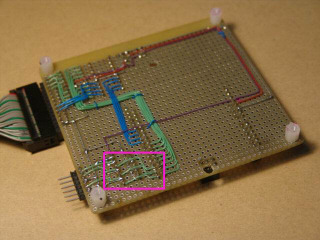

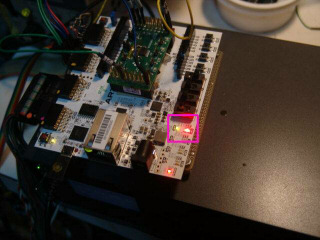

FPGAシンセにSPIスレーブ受信のロジックを追加しました。パラメータ設定器からのデータが受信できるか確認します。未配線だったベースボード上のHCT14とFPGA間を配線します。

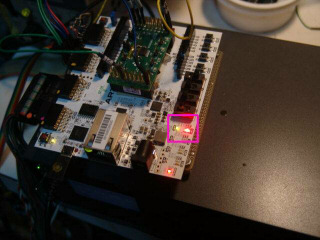

パラメータ設定器とFPGAシンセをケーブル接続し、デバッグ用のロジックを追加して、パラメータ設定器が出力するチャンネルとファンクションをボード上のLEDに表示します。チャンネルを2に変更すると、ボード上のLEDが点灯します。

続いて、ファンクションを2(DCO2)に変更すると別のLEDが点灯しました。チャンネルとファンクションの6ビットが正しく、FPAGシンセ本体で受信できてるようです。パラメータ変更ができるかは次回、確認します。

4月17日

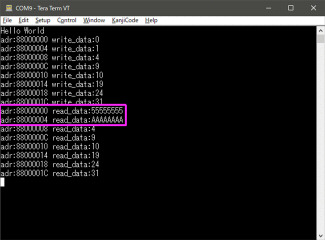

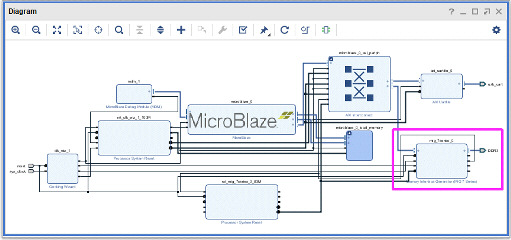

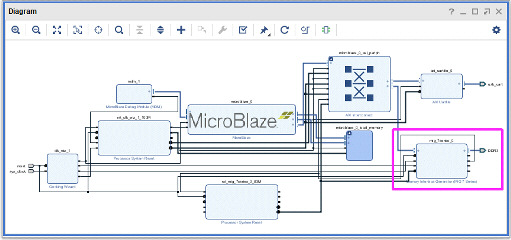

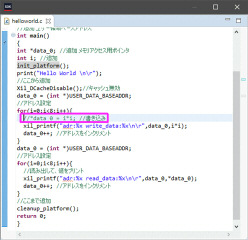

会社の昼休みに35Tボードでちょっと実験です。去年の夏に行ったFPGAマガジンのARTYボードのDDR3の続きです。ビットファイルを作ったままになっていましたが、マイクロブレーズのテストプログラムをSDKで作成してDDRにアクセスしてみます。

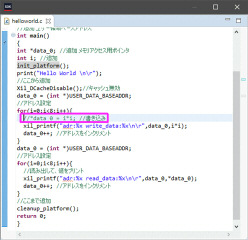

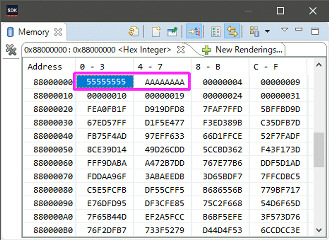

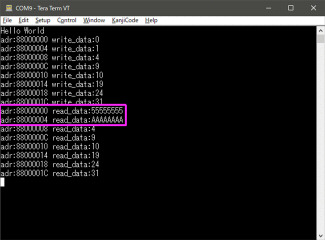

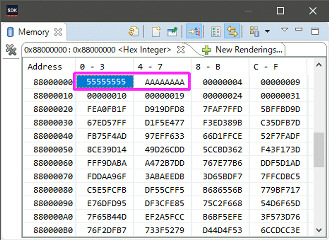

プログラムを実行して、DDR3が正しく動作していることを確認しました。その後、プログラムを修正してデータを書かないようにビルドし、デバッグのメモリウインドでメモリの値を書き換えます。

再実行すると、メモリウインドで書き換えた値が正しくターミナルに表示されました。デバッガからのメモリアクセスも問題なく出来ました。大容量メモリ用途はシンセではウェーブメモリしか思い当たりませんが、何か有効利用できるロジックを考えたいです。